# 42V クワッド、ギャング可能、同期整流式 モノリシック降圧レギュレータ

### 特長

- Silent Switcher®2アーキテクチャ

- 超低EMI放射

- オプションのスペクトラム拡散変調

- 2つの高電圧同期整流式降圧レギュレータ

- 入力電圧範囲:3V~42V

- 出力電流:最大2A/チャンネル

- 1つのインダクタでチャンネルを並列に接続可能

- 2つの低電圧同期整流式降圧レギュレータ

- 入力電圧範囲:3V~8V

- 出力電流:最大2A/チャンネル

- 1つのインダクタでチャンネルを並列に接続可能

- Io:12µA(全チャンネル・アクティブかつ無負荷時)

- 柔軟な電源シーケンスと制御

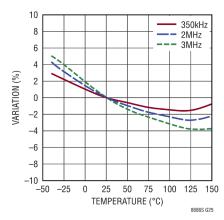

- 調整と同期が可能:350kHz~3MHz

- 32ピンのLQFN(5mm×5mm)で提供可能

- オートモーティブ・アプリケーション向けの AEC-Q100 に 適合

### アプリケーション

- 車載システム

- 産業用制御および電源

### 概要

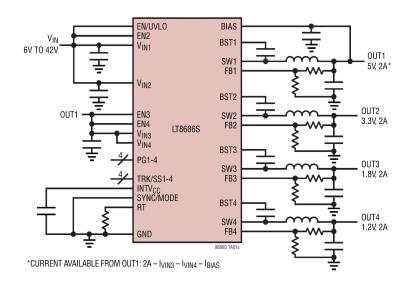

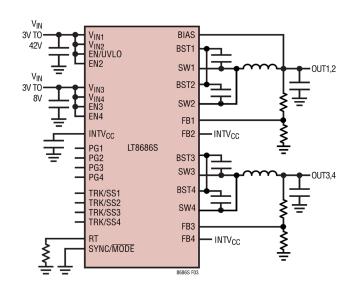

LT®8686Sは、柔軟性の高い4チャンネルの電流モード・モノリシック・レギュレータで、最小限の基板スペースで多様な車載および産業用アプリケーションに電源を供給できます。

LT8686Sは、2つの42V対応2A降圧レギュレータと2つの8V対応2A降圧レギュレータを組み合わせたものです。2つの42Vレギュレータを組み合わせることにより、1つのインダクタで最大4Aの出力電流を供給できます。同様に、2つの8Vレギュレータを組み合わせることにより、1つのインダクタで最大4Aの出力電流を供給できます。また、チャンネル・イネーブル、トラック/ソフトスタート、パワー・グッドの各ピンにより、柔軟な電源シーケンスと制御が可能です。LT8686Sは、Silent Switcher 2アーキテクチャと選択可能なスペクトラム拡散モードにより、高スイッチング周波数で高効率を実現しながら、極めて低いEMI/EMC放射を実現しています。

LT8686Sは、サーマル・シャットダウン機能と各チャンネルでのサイクルごとの電流制限機能を内蔵しており、短絡保護と 堅牢な動作を実現しています。

全ての登録商標および商標の所有権は、それぞれの所有者に帰属します。

### 標準的応用例

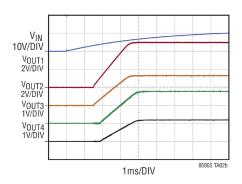

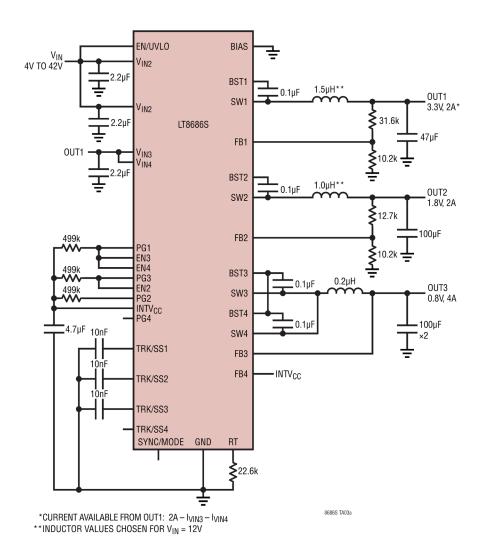

#### 42V 入力、クワッド出力 2MHz 降圧レギュレータ

# 絶対最大定格

| V <sub>IN1</sub> , V <sub>IN2</sub> | 0.3V~42V   |

|-------------------------------------|------------|

| V <sub>IN3</sub> , V <sub>IN4</sub> | 0.3V~10V   |

| EN/UVLO、EN2、EN3、EN4                 | 42V        |

| PG1、PG2、PG3、PG4、SYNC/MODE           | 6V         |

| BIAS                                | 0.3V~14V   |

| FB1、FB2、FB3、FB4                     | 4V         |

| TRK/SS1、TRK/SS2、TRK/SS3、TRK/SS4     | 4V         |

| 動作ジャンクション温度(Note 2, 3)              |            |

| LT8686SJ                            | 40°C~150°C |

| 保存温度範囲                              | 65°C~150°C |

| 最高リフロー(パッケージ・ボディ)温度                 | E260°C     |

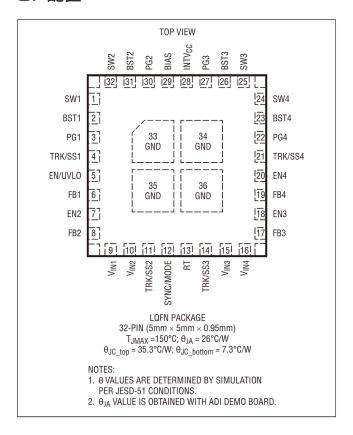

## ピン配置

• 推奨されるBGA PCB のアセンブリおよび製造手順。

• BGAのパッケージ図面とトレイ図面。

### 発注情報

|                |                  |           | 製品マーキング |        |                              | MSL    | 温度範囲        |

|----------------|------------------|-----------|---------|--------|------------------------------|--------|-------------|

| 製品番号           | テープ&リール          | パッド仕上げ    | デバイス    | 仕上げコード | パッケージ・タイプ*                   | レーティング | (Note 2)    |

| LT8686SJV#PBF  | LT8686SJV#TRPBF  | Au (RoHS) | 8686S   | e4     | LQFN(QFNフットプリント<br>の積層パッケージ) | 3      | -40°C∼150°C |

| オートモーティブ製品**   |                  |           |         |        |                              |        |             |

| LT8686SJV#WPBF | LT8686SJV#WTRPBF | Au (RoHS) | 8686S   | e4     | LQFN(QFNフットプリント<br>の積層パッケージ) | 3      | -40°C∼150°C |

- ・ パッドまたはボールの仕上げコードはIPC/JEDEC J-STD-609によります。

- テープ&リールの仕様。

- 製品番号末尾がPBFとなっている製品はRoHSおよびWEEEに準拠しています。

- \* LT8686Sのパッケージ寸法は、標準の5mm×5mm QFNパッケージと同じです。

- \*\* このデパイスの各パージョンは、オートモーティブ・アプリケーションの品質と信頼性の条件に対応するよう管理された製造工程により提供されています。これらのモデルは「#W」というサフィックスで指定 されます。オートモーティブ・アプリケーション向けには、上記のオートモーティブ・グレード製品のみを提供しています。特定製品のオーダー情報とこれらのモデル固有のオートモーティブ信頼性レポート については、最寄りのアナログ・デバイセズまでお問い合わせください。

## 電気的特性

は、全動作温度範囲に適用される仕様であることを示します。それ以外の仕様は、T<sub>A</sub> = 25℃でのものです。

また、特に指定のない限り、V<sub>IN1</sub> = V<sub>IN2</sub> = 12V、V<sub>IN3</sub> = V<sub>IN4</sub> = 5V、f<sub>SW</sub> = 2MHzでの仕様です。

| PARAMETER                                                                      | CONDITIONS                                                                                                                                                        |   | MIN                 | TYP            | MAX                 | UNITS             |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|----------------|---------------------|-------------------|

| Quiescent Current, Shutdown                                                    |                                                                                                                                                                   |   |                     | 0.5            | 1.5                 | μA                |

| Total Operating Input Current, Burst                                           | V <sub>OUT1</sub> = V <sub>BIAS</sub> = 5V, V <sub>OUT2</sub> = 3.3V, V <sub>OUT3</sub> = 1.8V,<br>V <sub>OUT4</sub> = 1.2V, V <sub>SYNC/MODE</sub> = 0V, No Load |   |                     | 12             |                     | μA                |

| Total Operating Input Current, Pulse-Skipping                                  | V <sub>OUT1</sub> = 5V, V <sub>OUT2</sub> = 3.3V, V <sub>OUT3</sub> = 1.8V, V <sub>OUT4</sub> = 1.2V, V <sub>SYNC/MODE</sub> = Floating, No Load                  |   |                     | 1100           |                     | μА                |

| Switching Frequency                                                            | R <sub>RT</sub> = 154k<br>R <sub>RT</sub> = 22.6k<br>R <sub>RT</sub> = 13.7k                                                                                      | • | 0.28<br>1.8<br>2.65 | 0.35<br>2<br>3 | 0.45<br>2.25<br>3.4 | MHz<br>MHz<br>MHz |

| SYNC Threshold Voltage                                                         | V <sub>IL</sub><br>V <sub>IH</sub>                                                                                                                                | • | 1.5                 |                | 0.4                 | V                 |

| SYNC/MODE Pin Input Current                                                    | V <sub>SYNC/MODE</sub> = 6V                                                                                                                                       |   |                     | 75             |                     | μA                |

| Internal V <sub>CC</sub> Regulator                                             |                                                                                                                                                                   |   |                     | 3.4            |                     | V                 |

| Internal V <sub>CC</sub> Undervoltage Lockout                                  | Falling                                                                                                                                                           |   | 2.3                 | 2.4            | 2.5                 | V                 |

| BIAS Pin Threshold                                                             |                                                                                                                                                                   |   |                     | 4.5            |                     | V                 |

| Channels 1, 2                                                                  |                                                                                                                                                                   |   |                     |                |                     |                   |

| Minimum Input Voltage (CH1 Only)                                               |                                                                                                                                                                   | • |                     | 2.8            | 3.0                 | V                 |

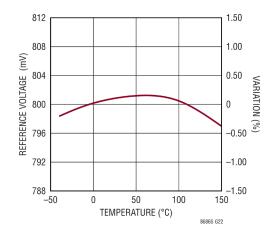

| Feedback Reference Voltage                                                     |                                                                                                                                                                   | • | 0.786               | 0.8            | 0.812               | V                 |

| Feedback Input Current                                                         |                                                                                                                                                                   | • | -100                | 0              | 100                 | nA                |

| V <sub>FB1</sub> , V <sub>FB2</sub> Line Regulation                            | V <sub>VIN1</sub> = 3V to 42V                                                                                                                                     |   |                     | 0.01           |                     | %/V               |

| Peak Current Limit                                                             |                                                                                                                                                                   |   | 3.5                 | 4              | 4.5                 | А                 |

| Power MOSFET On-Resistance<br>Main Switch (Top)<br>Synchronous Switch (Bottom) | I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A<br>I <sub>SW1</sub> , I <sub>SW2</sub> = 0.1A                                                                          |   |                     | 250<br>130     |                     | mΩ<br>mΩ          |

| EN/UVLO Threshold                                                              | EN/UVLO Falling                                                                                                                                                   | • | 0.78                | 0.8            | 0.82                | V                 |

| EN/UVLO Hysteresis                                                             |                                                                                                                                                                   |   |                     | 100            |                     | mV                |

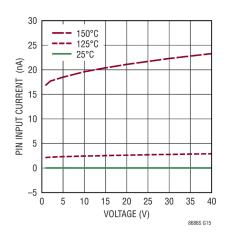

| EN/UVLO Input Current                                                          | V <sub>EN/UVLO</sub> = 42V                                                                                                                                        |   | -250                | 0              | 250                 | nA                |

| EN2 Threshold                                                                  | EN2 Falling                                                                                                                                                       | • | 0.78                | 0.81           | 0.84                | V                 |

| EN2 Hysteresis                                                                 |                                                                                                                                                                   |   |                     | 50             |                     | mV                |

| EN2 Input Current                                                              | V <sub>EN2</sub> = 42V                                                                                                                                            |   | -250                | 0              | 250                 | nA                |

| PGOOD Upper Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub>          | V <sub>FB1</sub> , V <sub>FB2</sub> Rising                                                                                                                        | • | 4.5                 | 7.5            | 10                  | %                 |

| PGOOD Lower Threshold Offset from V <sub>FB1</sub> , V <sub>FB2</sub>          | V <sub>FB1</sub> , V <sub>FB2</sub> Falling                                                                                                                       | • | -10                 | -7.5           | -4.5                | %                 |

| PGOOD Hysteresis                                                               |                                                                                                                                                                   |   |                     | 1.2            |                     | %                 |

| PGOOD Leakage                                                                  | V <sub>PG1</sub> , V <sub>PG2</sub> = 6V                                                                                                                          |   | -250                | 0              | 250                 | nA                |

| PGOOD Pull-Down Resistance                                                     | V <sub>PG1</sub> , V <sub>PG2</sub> = 0.1V                                                                                                                        |   |                     | 500            | 1200                | Ω                 |

| TRK/SS1, TRK/SS2 Pull-Up Current                                               | V <sub>TRK/SS1</sub> , V <sub>TRK/SS2</sub> = 0V                                                                                                                  |   |                     | 2.0            |                     | μA                |

### 電気的特性

は、全動作温度範囲に適用される仕様であることを示します。それ以外の仕様は、T<sub>A</sub> = 25℃でのものです。

また、特に指定のない限り、V<sub>IN1</sub> = V<sub>IN2</sub> = 12V、V<sub>IN3</sub> = V<sub>IN4</sub> = 5V、f<sub>SW</sub> = 2MHzでの仕様です。

| PARAMETER                                                             | CONDITIONS                                       |   | MIN   | TYP  | MAX              | UNITS |

|-----------------------------------------------------------------------|--------------------------------------------------|---|-------|------|------------------|-------|

| Channels 3, 4                                                         |                                                  |   |       |      |                  |       |

| Feedback Reference Voltage                                            |                                                  | • | 0.786 | 0.8  | 0.812            | V     |

| Feedback Input Current                                                |                                                  | • | -100  | 0    | 100              | nA    |

| V <sub>FB3</sub> , V <sub>FB4</sub> Line Regulation                   | V <sub>VIN1</sub> = 3V to 42V                    |   |       | 0.01 |                  | %/V   |

| Peak Current Limit                                                    |                                                  |   | 3.5   | 4    | 4.5              | А     |

| Power MOSFET On-Resistance Main Switch                                | I <sub>SW3</sub> , I <sub>SW4</sub> = 0.1A       |   |       | 120  |                  | mΩ    |

| Synchronous Switch (Bottom)                                           | I <sub>SW3</sub> , I <sub>SW4</sub> = 0.1A       |   |       | 65   |                  | mΩ    |

| EN3, EN4 Threshold                                                    | EN3, EN4 Falling                                 | • | 0.78  | 0.81 | 0.84             | V     |

| EN3, EN4 Hysteresis                                                   |                                                  |   |       | 50   |                  | mV    |

| EN3, EN4 Input Current                                                | V <sub>EN3</sub> , V <sub>EN4</sub> = 42V        |   | -250  | 0    | 250              | nA    |

| PGOOD Upper Threshold Offset from V <sub>FB3</sub> , V <sub>FB4</sub> | V <sub>FB3</sub> , V <sub>FB4</sub> Rising       | • | 4.5   | 7.5  | 10               | %     |

| PGOOD Lower Threshold Offset from V <sub>FB3</sub> , V <sub>FB4</sub> | V <sub>FB3</sub> , V <sub>FB4</sub> Falling      | • | -10   | -7.5 | <del>-4</del> .5 | %     |

| PGOOD Hysteresis                                                      |                                                  |   |       | 1.2  |                  | %     |

| PGOOD Leakage                                                         | V <sub>PG3</sub> , V <sub>PG4</sub> = 6V         |   | -250  | 0    | 250              | nA    |

| PGOOD Pull-Down Resistance                                            | V <sub>PG3</sub> , V <sub>PG4</sub> = 0.1V       |   |       | 500  | 1200             | Ω     |

| TRK/SS3, TRK/SS4 Pull-Up Current                                      | V <sub>TRK/SS3</sub> , V <sub>TRK/SS4</sub> = 0V |   |       | 2.0  |                  | μA    |

Note 1: 上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。デバイスを長時間絶対最大定格状態に置くと、デバイスの信頼性と寿命に影響を与えることがあります。

Note 2: LT8686SJの動作ジャンクション温度範囲の仕様値は、-40℃~150℃です。ジャンクション温度が高い場合は動作寿命が低下します。ここに示す仕様に見合った最大周囲温

度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。

Note 3:このIC は、過負荷状態からデバイスを保護することを目的とした過熱保護機能を備えています。過熱保護機能が作動した場合、ジャンクション温度は最大動作ジャンクション温度を超えてデバイスを連続動作させると、寿命が短くなります。

ロバチャンクリか

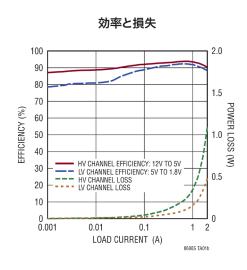

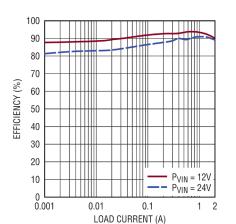

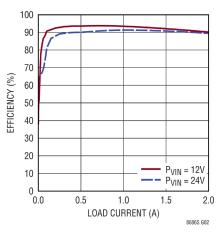

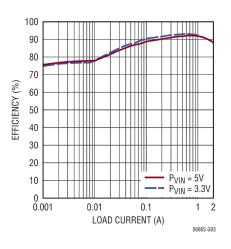

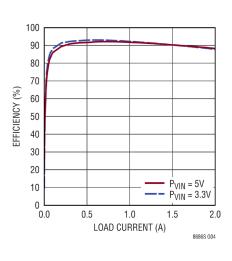

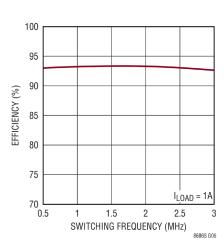

特に指定のない限り、TA=25℃、VIN1=VIN2=12V、VIN3=VIN4=3.3V、fSW=2MHz。

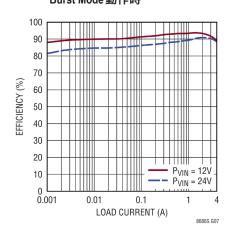

HV チャンネル効率と負荷の関係 V<sub>OUT</sub> = 5V、Burst Mode 動作時

HV チャンネル効率と負荷の関係 V<sub>OUT</sub> = 5V、パルス・スキッピング・ モード時

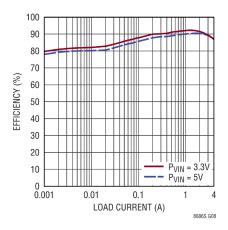

LV チャンネル効率と負荷の関係 V<sub>OUT</sub> = 1.8V、Burst Mode 動作時

LV チャンネル効率と負荷の関係 V<sub>OUT</sub> = 1.8V、パルス・スキッピング・ モード時

8686S G01

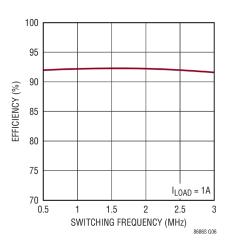

HVチャンネル効率と周波数の関係 V<sub>OUT</sub> = 5V、Burst Mode 動作時

LV チャンネル効率と周波数の関係 V<sub>OUT</sub> = 1.8V、Burst Mode 動作時

HV チャンネル効率と負荷の関係 CH1と CH2を共有、V<sub>OUT</sub> = 5V、 Burst Mode 動作時

LV チャンネル効率と負荷の関係 CH3とCH4を共有、V<sub>OUT</sub> = 1.8V、 Burst Mode 動作時

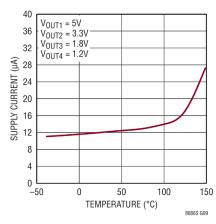

無負荷時供給電流と温度の関係、 Burst Mode 動作時

特に指定のない限り、TA=25℃、VIN1=VIN2=12V、VIN3=VIN4=3.3V、fSW=2MHz。

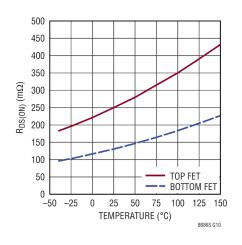

HV チャンネルの R<sub>DS(ON)</sub>と 温度の関係

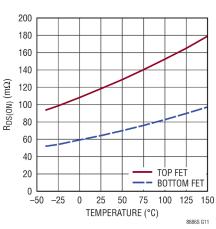

LV チャンネルの R<sub>DS(ON)</sub>と 温度の関係

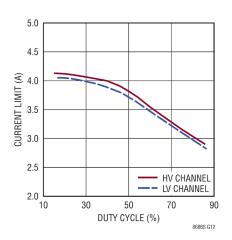

上側 MOSFET の電流制限値と デューティ・サイクルの関係

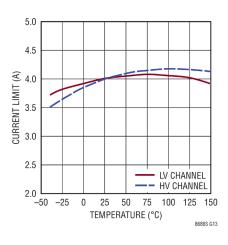

上側 MOSFET の電流制限値と 温度の関係

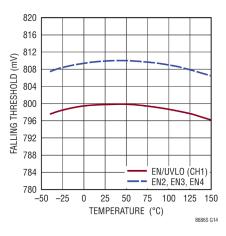

イネーブル・ピンの立下がり閾値と 温度の関係

イネーブル・ピンの電流と 電圧および温度の関係

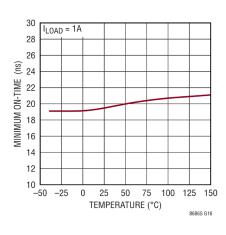

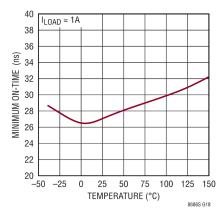

HV チャンネルの最小オン時間と 温度の関係

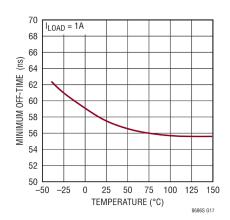

HV チャンネルの最小オフ時間と 温度の関係

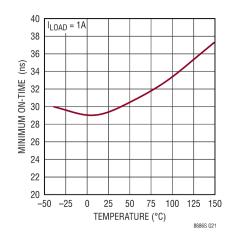

HVチャンネルの最小オン時間と 温度の関係、CH1とCH2を共有時

45

\_50 \_25 0 25 50 75 100

特に指定のない限り、T<sub>A</sub> = 25°C、V<sub>IN1</sub> = V<sub>IN2</sub> = 12V、V<sub>IN3</sub> = V<sub>IN4</sub> = 3.3V、f<sub>SW</sub> = 2MHz。

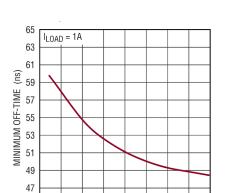

HVチャンネルの最小オフ時間と 温度の関係、CH1とCH2を共有時

TEMPERATURE (°C)

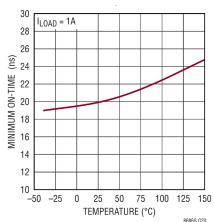

LVチャンネルの最小オン時間と 温度の関係

LVチャンネルの最小オン時間と 温度の関係、CH3とCH4を共有時

リファレンス電圧と温度の関係

125 150

8686S G19

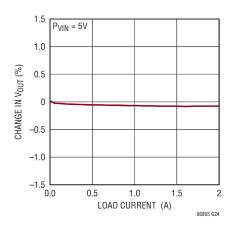

HV チャンネルの 負荷レギュレーション

LVチャンネルの 負荷レギュレーション

スイッチング周波数と温度の関係

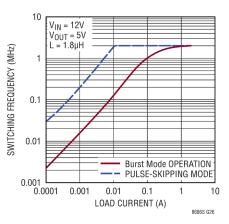

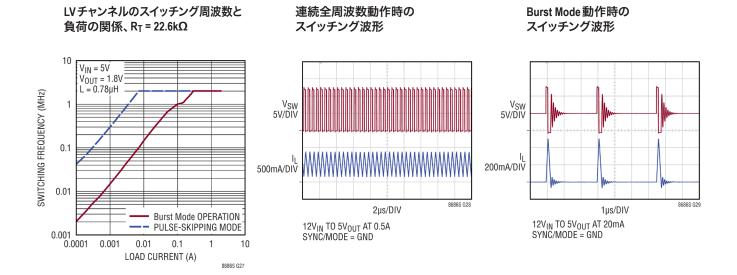

HV チャンネルのスイッチング周波数と 負荷の関係、 $R_T$  = 22.6 $k\Omega$

Rev. A

7

特に指定のない限り、TA=25℃、VIN1=VIN2=12V、VIN3=VIN4=3.3V、fSW=2MHz。

パルス・スキッピング動作時の スイッチング波形

12V<sub>IN</sub> TO 5V<sub>OUT</sub> AT 20mA SYNC/MODE = FLOATING

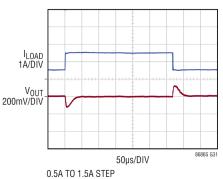

### HVチャンネルの負荷ステップ

5V<sub>OUT</sub> = 47µF Burst Mode OPERATION, f<sub>SW</sub> = 2MHz

#### LVチャンネルの負荷ステップ

1.8V<sub>OUT</sub> C<sub>OUT</sub> = 47µF ×2 Burst Mode OPERATION, f<sub>SW</sub> = 2MHz

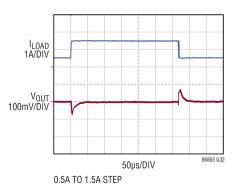

#### 伝導 EMI 性能

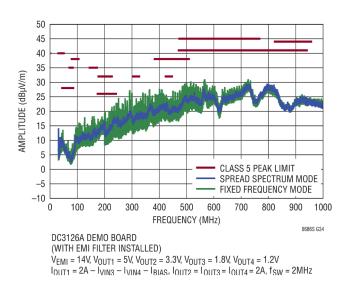

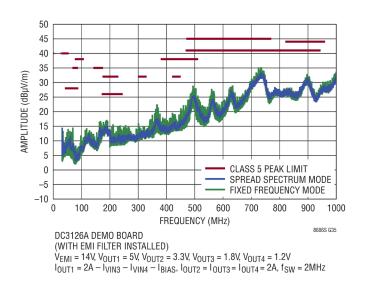

DC3126A DEMO BOARD (WITH EMI FILTER INSTALLED)  $V_{EMI} = 14V, V_{OUT1} = 5V, V_{OUT2} = 3.3V, V_{OUT3} = 1.8V, V_{OUT4} = 1.2V \\ I_{OUT1} = 2A - I_{VIN3} - I_{VIN4} - I_{BIAS}, I_{OUT2} = I_{OUT3} = I_{OUT4} = 2A, f_{SW} = 2MHz$

特に指定のない限り、TA = 25°C、VIN1 = VIN2 = 12V、VIN3 = VIN4 = 3.3V、fSW = 2MHz。

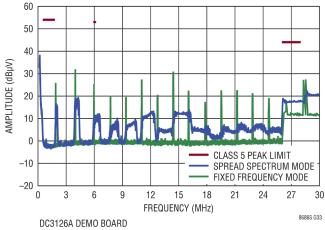

#### 放射 EMI 性能 - 垂直偏波 (CISPR25 放射妨害波試験、クラス5ピーク限界値)

#### 放射 EMI 性能 - 水平偏波 (CISPR25 放射妨害波試験、クラス5ピーク限界値)

### ピン機能

SW1、SW2、SW3、SW4(ピン1、ピン32、ピン25、ピン24):チャンネル・スイッチ・ピン。これらのピンは対応するチャンネルの内部パワー・スイッチの出力です。個別に動作させる場合は、それぞれのSWピンを対応するチャンネルのインダクタと昇圧コンデンサに接続します。チャンネルを組み合わせる場合は、組み合わせるチャンネルのSWピン同士を低インピーダンスで接続します。優れた効率とEMI性能を得るため、プリント基板上でのSWパターンは短くしてください。

BST1、BST2、BST3、BST4(ピン2、ピン31、ピン26、ピン23): チャンネル昇圧ピン。これらのピンは、各チャンネルの上側 パワー・スイッチのゲートに電源電圧より高い駆動電圧を 供給します。

PG1、PG2、PG3、PG4(ピン3、ピン30、ピン27、ピン22):オープンドレインのパワー・グッド出力ピン。各チャンネルのPGピンは、対応するFBピンの電圧が内部0.8Vリファレンス電圧の $\pm7.5\%$ の範囲から外れると、グラウンドにプルダウンされます。対応するFBピンの電圧が内部リファレンス電圧の $\pm6\%$ の範囲内に戻ると、PGピンは高インピーダンスになります。イネーブルされたチャンネルのPG出力は、 $V_{\rm IN1}$ 電圧が3Vを超えたときに有効になります。イネーブルされていないチャンネルのPG出力は、uーにプルダウンされます。チャンネルを組み合わせる場合、従属u0、レーブu0、チャンネルのPGピンはオープンにする必要があります。

TRK/SS1、TRK/SS2、TRK/SS3、TRK/SS4(ピン4、ピン11、ピン14、ピン21):出力トラッキングおよびソフトスタート・ピン。これらのピンを使用すると、起動時に出力電圧の上昇率を制御することができます。TRK/SSxピンの電圧が0.8Vより低くなると、そのチャンネルは、FBxピンの電圧がTRK/SSxピンの電圧と等しくなるように調整します。TRK/SSピンの電圧が0.8Vより高くなると、トラッキング機能が無効化され、内部リファレンスによってエラー・アンプの制御が再開されます。このピンにはINTV<sub>CC</sub>から2µAの内部プルアップ電流が流れるので、コンデンサを使って出力電圧のスルー・レートを設定できます。チャンネルを組み合わせる場合、従属(スレーブ)チャンネルのTRK/SSピンはオープンにする必要があります。

**EN/UVLO(ピン5)**:チャンネル1イネーブルおよび低電圧ロックアウト・ピン。このピンが0.4Vより低くなると、LT8686Sの他のイネーブル・ピンの状態に関係なく、LT8686Sは低消費電力シャットダウン状態になります。電圧が0.9V(立上がり)を

超えると、LT8686の動作とチャンネル1がイネーブルになります。0.8V(立下がり)の高精度閾値により、V<sub>IN1</sub>とグラウンドの間に抵抗分圧器を接続すると、このピンを入力低電圧ロックアウトとして使用できます。

FB1(ピン6): チャンネル1の出力電圧帰還ピン。チャンネル1では、このピンを高精度な0.8Vの内部リファレンス電圧に調整します。このピンを適切な抵抗分圧器に接続し、必要な出力電圧を設定します。

EN2、EN3、EN4(ピン7、ピン18、ピン20):チャンネル・イネーブルピン。LT8686Sの各チャンネルは、対応するイネーブル・ピンの電圧が0.9V(立上がり)を超えると、アクティブになります。0.81V(立下がり)の高精度閾値により、対応する入力電源とグラウンドの間に抵抗分圧器を接続すると、各イネーブル・ピンはプログラマブルな低電圧ロックアウトとして機能します。チャンネルを組み合わせる場合、従属(スレーブ)チャンネルのENピンを制御(マスタ)チャンネルのイネーブル・ピンに接続する必要があります。

FB2(ピン8): チャンネル2の出力電圧帰還ピン。チャンネル2では、このピンを高精度な0.8Vの内部リファレンス電圧に調整します。このピンを適切な抵抗分圧器に接続し、必要な出力電圧を設定します。このピンをINTVccに接続すると、チャンネル2はチャンネル1と組み合わされて1つの出力チャンネルになり、出力電流能力が増大します。詳細についてはアプリケーション情報のセクションを参照してください。

$V_{IN1}$ (ピン9): チャンネル1と内部 INTV<sub>CC</sub>レギュレータの電源入力。このピンは、 $2.2\mu$ F以上の低 ESR コンデンサでグラウンドと確実にデカップリングする必要があります。

$V_{IN2}$ (ピン10): チャンネル2の電源入力。このピンは2.2 $\mu$ F以上の低ESR コンデンサでグラウンドと確実にデカップリングする必要があります。 チャンネル2をチャンネル1と組み合わせる場合は、このピンを $V_{IN1}$ と短絡します。

SYNC/MODE (ピン12): モード選択および外部同期入力ピン。このピンをグラウンドに接続すると、LT8686Sのアクティブな全チャンネルが高効率のBurst Mode®動作になります。このピンを $26k\Omega$  (許容差5%以下)の抵抗でグラウンドに接続すると、スペクトラム拡散変調を用いた高効率のBurst Modeが有効になります。このピンをフロートにすると、パルス・スキッピング・モードが有効になります。このピンをINTVCCに接続すると、スペクトラム拡散変調を用いたパル

### ピン機能

ス・スキッピング・モードが有効になります。このピンを外部クロック源で駆動すると、LT8686Sはスイッチング周波数を外部クロックに同期させ、パルス・スキッピング・モードで動作します。チャンネル1~4のクロック位相は、個別に動作させる場合、それぞれ0°、180°、270°、90°に初期設定されます。チャンネルを組み合わせる場合は、マスタ・チャンネルで動作位相が決定されます。詳細についてはアプリケーション情報のセクションを参照してください。

RT(ピン13):スイッチング周波数設定ピン。このピンとグラウンドの間に抵抗を外付けすると、LT8686Sのスイッチング周波数を350kHz~3MHzの範囲で設定できます。外部クロック同期を使用する場合、R<sub>T</sub>抵抗を公称入力クロック周波数と一致するように選択する必要があります。詳細についてはアプリケーション情報のセクションを参照してください。

$V_{IN3}$ (ピン15): チャンネル3の電源入力。他のLT8686Sチャンネルから駆動する場合、このピンに必要なデカップリング容量は、駆動チャンネルの出力容量でほぼ満たされます。この場合、一般的には、 $1\mu$ F以上の低ESRコンデンサを $V_{IN3}$ ピンの近くに配置すれば十分です。外部ソースから駆動する場合は、このピンを、 $4.7\mu$ F以上の低ESRコンデンサを用いて確実にデカップリングする必要があります。

$V_{IN4}$ (ピン16): チャンネル4の電源入力。他のLT8686Sチャンネルから駆動する場合、このピンに必要なデカップリング容量は、駆動チャンネルの出力容量でほぼ満たされます。この場合、一般的には、 $1\mu$ F以上の低ESRコンデンサを $V_{IN4}$ ピンの近くに配置すれば十分です。外部ソースから駆動する場合は、このピンを、 $4.7\mu$ F以上の低ESRコンデンサを用いて確実にデカップリングする必要があります。

FB3(ピン17):チャンネル3の出力電圧帰還ピン。チャンネル3では、このピンを高精度な0.8Vの内部リファレンス電圧に調整します。このピンを適切な抵抗分圧器に接続し、必要な出力電圧を設定します。

FB4(ピン19):チャンネル4の出力電圧帰還ピン。チャンネル4では、このピンを高精度な0.8Vの内部リファレンス電圧に調整します。このピンを適切な抵抗分圧器に接続し、必要な出力電圧を設定します。このピンをINTVccに接続すると、チャンネル4はチャンネル3と組み合わされて1つの出力チャンネルになり、出力電流能力が増大します。詳細についてはアプリケーション情報のセクションを参照してください。

INTVcc (ピン28): 内部レギュレータの出力ピン。このレギュレータは、パワーMOSFETドライバ回路と内部制御回路に電流を供給します。このピンは4.7µFの低ESRセラミック・コンデンサでグラウンド・ピンとデカップリングします。このコンデンサは、INTVccピンの近くに配置し、露出パッドのグラウンドに低インピーダンスで接続する必要があります。この電源は、電源出力を意図したものではありません。このピンには外部の回路を接続しないでください。

BIAS (ピン29):外付けレギュレータの入力ピン。BIASを4.5Vよりも高い電圧に接続し、かつ、VVIN1がVBIAS + 1Vよりも大きい場合、内部レギュレータ(INTVCC)にはVIN1の代わりに、この電源から電流が流れます。このピンを、5VにレギュレーションするLT8686Sの出力チャンネルなどの高効率電源に接続すると、VIN1から電流が流れる際に通常生じるオンチップ消費電力が低減し、全体的な効率が向上します。このピンを使用する場合は、0.1µF以上の低ESRセラミック・コンデンサでグラウンド・ピンとデカップリングします。他のLT8686Sチャンネルで駆動する場合、必要なデカップリング容量は、駆動チャンネルの出力容量で満たすことができます。使用しない場合は、このピンをグラウンドに接続します。

GND(露出パッド・ピン33~36):グラウンド・ピン。これらのピンは、低インピーダンスでグラウンドに電気的に接続し、PCBとの熱接触が良くなるよう、PCBにハンダ処理する必要があります。詳細についてはアプリケーション情報のセクションを参照してください。

**コーナー・ピン**: これらのピンは、機械的に支持するためのものに過ぎず、PCB上の任意の場所(通常はグラウンド)に接続できます。

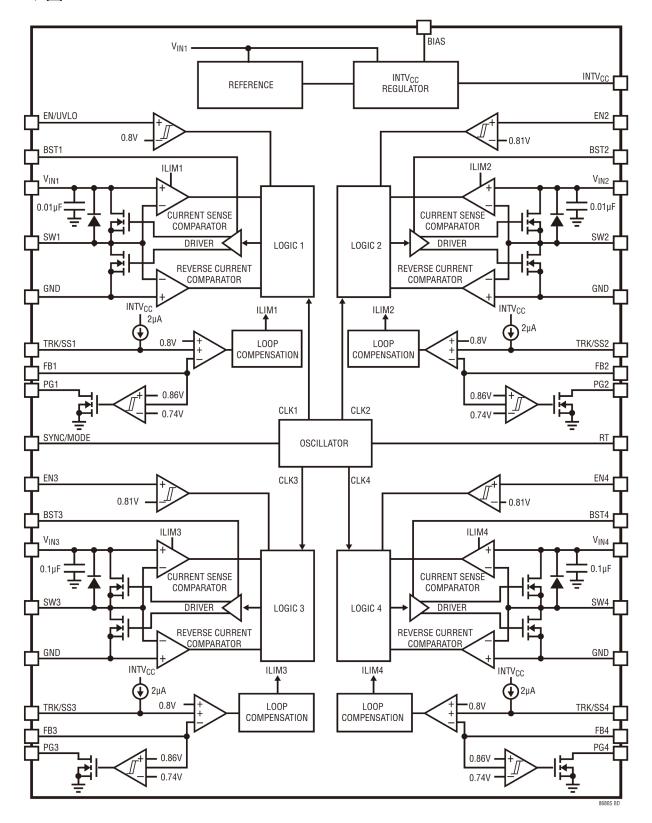

## ブロック図

### 動作

LT8686Sは、アナログ・デバイセズの第2世代Silent Switcher 技術を採用した42V入力対応のクワッド・モノリシック降圧レギュレータで、高速スイッチング・エッジにより高スイッチング周波数で高効率を可能にし、同時に優れたEMI/EMC性能も実現しています。

チャンネル1と2は、最大42Vの入力電圧から、それぞれ最大2Aの出力電流を供給できるように設計されています。チャンネル3と4は、最大8Vの入力電圧から、それぞれ最大2Aの出力電流を供給できるように設計されています。1つのインダクタを用いてチャンネルを組み合わせることで、より大きな出力電流を得ることができます。例えば、チャンネル1と2を1つのインダクタで結合し、最大4Aのレギュレーション出力を得ることができます。また、チャンネル3と4を1つのインダクタで結合し、最大8Aの安定化出力を得ることができます。VINピンが個別となっているため、1つのチャンネルの出力を他のチャンネルの入力に供給できます。

#### 起動

EN/UVLO電圧を閾値より高く設定すると、LT8686SのINTV<sub>CC</sub>レギュレータは出力コンデンサを充電して内部チップ回路に電力を供給します。EN/UVLO電圧を0.9V(立上がり)よりも高く設定すると、チャンネル1レギュレータがイネーブルになります。EN/UVLO電圧をUVLO閾値より低く設定すると、他のイネーブル・ピンの状態に関係なく、デバイスは低消費電力シャットダウン・モードになります。

チャンネル2、3、4は、対応するイネーブル・ピンを0.9V立上がり)よりも高く(設定すると、イネーブルされます。チャンネルを組み合わせる場合、スレーブ・チャンネルのイネーブル・ピンを制御側チャンネルのイネーブル・ピンに接続します。詳細は、アプリケーション情報のセクションの「チャンネルの組み合わせ」を参照してください。

#### 降圧レギュレータの動作

各チャンネルは、個別のV<sub>IN</sub>ピンにより動作するモノリシック同期整流式降圧レギュレータです。内蔵の上側パワーMOSFETは発振器サイクルの開始ごとにオンになり、上側MOSFETを通過する電流がエラー・アンプによって決められたレベルに達するとオフになります。エラー・アンプはFBピンに接続さ

れた外付け抵抗分圧器を介して出力電圧を測定し、上側スイッチのピーク電流を制御します。エラー・アンプの基準は、0.8V内部リファレンスとソフトスタート(TRK/SSx)ピンの電圧の低い方で決定されます。上側MOSFETがオフの間、下側MOSFETは発振周期の残り時間またはインダクタ電流が反転し始めるまでオンになります。電流オーバーロード状態では、下側MOSFETはオンのままになり、スイッチ電流が減少するまで次のクロック・サイクルが遅延します。

#### 高精度イネーブル・ピン

EN/UVLOピンの電圧を0.4Vよりも低くすると、LT8686Sは低消費電力シャットダウン・モードになります。EN/UVLOピンの電圧を0.9V(立上がり)よりも高くすると、チャンネル1の動作がイネーブルになります。チャンネル2、3、4も、それぞれ対応するEN2、EN3、EN4ピンを0.9V(立上がり)よりも高くするとアクティブになります。

0.8V(立下がり)の高精度閾値により、V<sub>IN1</sub>とグラウンドの間に抵抗分圧器を接続することで、EN/UVLOを入力低電圧ロックアウトとして使用できます。同様に、0.81Vの高精度閾値により、EN2、EN3、EN4も入力低電圧ロックアウトとして使用できます。詳細については、アプリケーション情報のセクションを参照してください。

#### パワー・グッド・コンパレータ

各チャンネルには、オープンドレイン出力のパワー・グッド・コンパレータがあり、帰還電圧がリファレンス電圧より7.5%以上高いか低い場合に、PGピンをローにプルダウンします。帰還電圧がリファレンス電圧の±6%以内になると、PGピンが解放されます。PG出力は、INTV<sub>CC</sub>が2.7Vに立ち上がるまでは有効になりません。

#### スイッチング周波数

各チャンネルは、内部発振器のクロックで動作し、その周波数は、RTピンからグラウンドに接続された外付け抵抗で決定されます。外付け抵抗の値を適切に選択することにより、スイッチング周波数を350kHz~3MHzの範囲で設定できます。周波数選択の詳細については、アプリケーション情報のセクションを参照してください。

### 動作

発振器は4つのクロック位相を生成します。個別動作の場合、各チャンネルの相対位相は、CH1が0°、CH2が180°、CH3が270°、CH4が90°となります。多相化により、入力電流のリップル振幅は減少しますが、リップル周波数が高くなるため、必要な入力容量は減少します。チャンネルを組み合わせる場合は、マスタ・チャンネルの位相で組み合わせるチャンネルのクロック位相が決定されます。

#### モード選択と同期

LT8686Sには、Burst Mode動作とパルス・スキッピング・モードの2つの主要動作モードがあり、それぞれ周波数スペクトラム拡散を選択できます。パルス・スキッピング・モードでは、全てのスイッチング・サイクルが内部クロックに揃ったままになります。更に、Burst Mode動作よりも負荷電流を低く抑えるために、最大のスイッチング周波数が維持されます。逆に、Burst Mode動作では低負荷電流時に入力電流が減少するため、パルス・スキッピング・モードよりも低負荷時に高い効率を実現できます。スペクトラム拡散を選択すると、設定したクロック周波数が周波数変調されて、EMI/EMC放射が低減します。また、このモードを選択した場合、クロック周波数は設定周波数と設定周波数プラス約20%の間で変化します。

SYNC/MODEピンは、必要な動作モードを選択するのに使用します。低リップル、高効率のBurst Mode 動作を選択する場合は、SYNC/MODEピンをグラウンドに接続します。また、26kΩ(許容差5%以下)の抵抗を接続することで、スペクトラム拡散を用いた低リップル高効率のBurst Mode 動作が有効になります。パルス・スキッピング・モードを選択するには、SYNC/MODEピンをフロート状態にします。あるいは、スペクトラム拡散を用いたパルス・スキッピングを有効にするには、SYNC/MODEピンをINTVCCに接続します。

最後に、SYNC/MODEピンを、ハイ電圧が最小1.5V、ロー電圧が最大0.4Vのクロック信号で駆動することにより、LT8686Sを外部クロック源に同期させることができます。必要な最小パルス幅は、ハイ・パルスで100ns、ロー・パルスで100nsです。同期させる場合は、LT8686Sのスイッチング周波数が同期周波数に近くなるようにRT抵抗を選択する必要があります。LT8686Sは、外部クロックに同期している間は、パルス・スキッピング・モードで動作します。

#### INTVcc レギュレータ

INTVCCレギュレータは、LT8686Sの内部回路に電源を供給します。流れる電流は動作周波数によって変わり、スイッチング周波数が高いほどINTVCCから流れる電流は大きくなります。レギュレータは、起動時にVINIから電源供給されますが、バイアス電圧が4.5Vを超え、VVINIがVBIAS+1Vよりも大きいと、バイアスから電源電流が流れます。BIASピンを、4.5V以上のスイッチング・レギュレータのチャンネルに接続すると、効率が向上し、オンチップの消費電力が減少して、必要な電流は低下します。INTVCCレギュレータは、LT8686Sに関連する他の入力ピンや出力プルアップの設定に使用できます。予期しない相互作用を避けるため、LT8686Sに関連しない部品に接続することは避けてください。

Rev. A

14

LT8686Sは、4つの降圧コンバータを組み合わせ、最小限の基板スペースで2~4つの安定化出力を生成するように構成できる、柔軟なシステム電源を提供します。

#### 高精度低電圧ロックアウト

EN/UVLOピンの高精度な0.8V 閾値(立下がり)により、 $V_{IN1}$ 入力電源ピンとEN/UVLOピンの間に抵抗分圧器を外付けすることで、LT8686Sでプログラマブルな低電圧ロックアウト機能が実現できます。EN/UVLOがロジック・ローの入力になると、EN2、EN3、EN4ピンの状態に関わらず、全てのチャンネルがオフになります。

図1に、LT8686SのUVLO分圧器回路を示します。UVLO閾値は、式1で与えられます。

$$V_{(LT8686S\_UVLO)} = \frac{R_{UV1} + R_{UV2}}{R_{UV2}} \bullet 0.8V$$

図1.LT8686S UVLO抵抗分圧器の接続

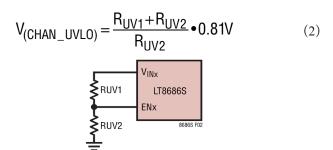

EN/UVLOピンと同様に、EN2、EN3、EN4ピンの高精度な0.81Vリファレンスにより、対応するチャンネルの入力電源ピンとそのENピンの間に抵抗分圧器を外付けすることで、各チャンネルでプログラマブルな低電圧ロックアウト機能が得られます。

各チャンネルのUVLO分圧回路を図2に示します。 閾値は、 式2で与えられます。

図2. 個別チャンネルUVLO抵抗分圧器の接続

#### スイッチング周波数

各チャンネルは、内部発振器のクロックで動作し、その周波数は、 $R_T$ ピンからグラウンドに接続された外付け抵抗で決定されます。外付け抵抗の値を適切に選択することにより、スイッチング周波数を $350kHz\sim3MHz$ の範囲で設定できます。

表1は、いくつかの一般的なスイッチング周波数におけるRT 抵抗の推奨値を示しています。

表1.スイッチング周波数(fsw)とRTの値の関係

| SWITCHING FREQUENCY<br>(MHz) | R <sub>T</sub><br>(kΩ) |

|------------------------------|------------------------|

| 0.35                         | 154                    |

| 0.5                          | 107                    |

| 0.75                         | 69                     |

| 1.0                          | 49.9                   |

| 1.25                         | 39.0                   |

| 1.5                          | 32.0                   |

| 1.75                         | 26.4                   |

| 2.0                          | 22.6                   |

| 2.25                         | 19.6                   |

| 2.5                          | 17.2                   |

| 2.75                         | 15.4                   |

| 3.0                          | 13.7                   |

式3は表1に示したものに近い値を示します。

$$R_T = \frac{55.4}{f_{SW} - 0.002} - 5 \tag{3}$$

ここで、 $f_{SW}$ の単位はMHzで、 $R_T$ の単位は $k\Omega$ です。 $R_T$ ピンはノイズに敏感なため、抵抗はLT8686Sの近くに配置し、ノイズ源から離します。

発振器は4つのクロック位相を生成します。個別動作の場合、各チャンネルの相対位相は、CH1が0°、CH2が180°、CH3が270°、CH4が90°となります。チャンネルを組み合わせる場合は、マスタ・チャンネルの位相によって、組み合わせるチャンネルのクロック位相が決定されます。

#### チャンネルの組み合わせ

LT8686Sでは、複数のレギュレータを組み合わせることで、1 つのインダクタでより大きな出力電流が得られるレギュレータを作ることができます。

可能なチャンネルの組み合わせを表2に示します。

表2. 可能なチャンネルの組み合わせ

|   | CONFIGURATION | NUMBER OF INDEPENDENT REGULATORS |

|---|---------------|----------------------------------|

| 1 | 1, 2, 3, 4    | 4                                |

| 2 | 1, 2, 3 + 4   | 3                                |

| 3 | 1 + 2, 3, 4   | 3                                |

| 4 | 1 + 2, 3 + 4  | 2                                |

組み合わせる場合、最も小さい番号のチャンネルが、組み合わせたレギュレータを制御します。例えば、チャンネル1とチャンネル2を組み合わせた場合、チャンネル1が制御(マスタ)、チャンネル2が従属(スレーブ)となります。組み合わせたレギュレータの出力電圧を設定するために、帰還ネットワークをマスタ・チャンネルにのみ接続します。スレーブ・チャンネルの帰還ピンは、INTV<sub>CC</sub>に接続する必要があります。

組み合わせたチャンネルは、それぞれの $V_{IN}$ ピン、SWピン、BSTピン同士を低インピーダンスで接続する必要があります。組み合わせたSWピンにはインダクタを1つだけ接続します。また、組み合わせたBSTピン同士を接続しますが、昇圧コンデンサは各チャンネルごとに接続します。

チャンネル1と2およびチャンネル3と4で共有する場合の簡単なアプリケーションの回路図を図3に示します。

#### 逆入力保護

バッテリ充電やバッテリ・バックアップなど一部のアプリケーションでは、入力がフロート状態またはグラウンド電位になった場合、LT8686Sのチャンネル出力がハイに保持されることがあります。

図3.チャンネルを共有した場合の簡略回路図

もし、チャンネルの入力がフロート状態で、LT8686Sがイネーブルの場合、LT8686Sの内部回路には、その静止電流がSWピンを介して流れます。入力がフロート状態で、LT8686Sがディスエーブルの場合、SWピンの電流は1μA以下に低下します。入力をグラウンド電位にする場合は、出力から上側パワーMOSFETのボディ・ダイオードを通ってV<sub>INx</sub>ピンからグラウンド電位の入力へ流れる逆電流を防ぐために入力保護ダイオードが必要です(ブロック図を参照)。

#### 降圧レギュレータの部品選択

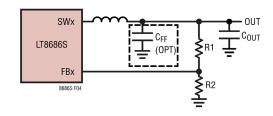

#### 出力電圧の設定

降圧チャンネルの出力電圧は、出力から対応するFBxピンへの抵抗分圧器で設定します(図4を参照)。

図4.帰還抵抗分圧器

16

まず、R2の最適値を選択します。この値は、I = 0.8V/R2で計算される、抵抗分圧器に流れる電流量を決定するためです。電流は、予想されるリークやノイズに影響されないように選択する必要があります。次に、R1を式4で計算します。

$$R1 = R2 \cdot \left( \frac{V_{0UTx}}{0.8} - 1 \right) \tag{4}$$

C<sub>FF</sub>はオプションで、内部補償された帰還ループの過渡応答と安定性を向上させるために使用できます。標準的応用例のセクションに示す値は、C<sub>FF</sub>を選択する際の良い出発点となりますが、十分な設計マージンを確保するために、レギュレータの安定性を慎重に評価する必要があります。

LT8686Sの42V入力対応チャンネルでは、設定可能な最大許容出力電圧は14Vです。

8V入力対応チャンネルを組み合わせた場合(チャンネル3と4)、設定可能な最大出力電圧は4Vです。

#### 動作周波数と入力電圧範囲

それぞれの降圧レギュレータの最小オン時間toN(MIN)と最小オフ時間toFF(MIN)により、実現可能なデューティ・サイクルの範囲と動作周波数に制限が課されます。降圧レギュレータの場合、デューティ・サイクルは式5で計算します。

$$D = \frac{V_{OUTx}}{V_{INx}} \tag{5}$$

更に、所定の動作周波数で実現可能な最小デューティ・サイクルは、式6で計算します。

$$D_{MIN} = t_{ON(MIN)} \bullet f_{SW}$$

(6)

ここで、fSWは設定する動作周波数です。

所定の動作周波数で実現可能な最大デューティ・サイクルは、式7で計算します。

$$D_{MAX} = 1 - (t_{OFF(MIN)} \bullet f_{SW})$$

(7)

式6と式7を組み合わせると、最大周波数におけるレギュレーション時の最小の $V_{\rm IN}$ 電圧は式8で与えられます。

$$V_{\text{IN}_{\mathcal{X}}(\text{MIN})} = \frac{V_{\text{OUT}_{\mathcal{X}}}}{1 - (t_{\text{OFF}(\text{MIN})} \bullet f_{\text{SW}})}$$

(8)

VVINx(MIN)以下では、降圧レギュレータはドロップアウト状態になり、上側スイッチは1クロック・サイクルより長くオン状態を維持します。ドロップアウトでの動作時、降圧レギュレータの出力電圧は設定された値より低くなります。

最大周波数でのレギュレーション時における最大の $V_{IN}$ 電圧は、式9で与えられます。

$$V_{\text{IN}x(\text{MAX})} = \frac{V_{\text{OUT}x}}{t_{\text{ON(MIN)}} \cdot f_{\text{SW}}}$$

(9)

レギュレーション時に上記のV<sub>VINX(MAX)</sub>を超えると、降圧 レギュレータはレギュレーションを維持するためにスイッチ オン・サイクルをスキップします。

#### インダクタの選択

所与の入出力電圧に対し、インダクタ値と動作周波数によってインダクタのリップル電流が決まります。具体的には、式10により、インダクタ値が高いほど、あるいは動作周波数が高いほど、インダクタのリップル電流は減少します。

$$\Delta I_{L} = \left(\frac{V_{OUT}}{f_{SW} \cdot L}\right) \cdot \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(10)

ここで、 $\Delta I_L$  = インダクタのリップル電流 (A)、 $f_{SW}$  = スイッチング周波数 (Hz)、L = インダクタ値 (H)、 $V_{IN}$  = 公称入力電圧定格です。式 10から、部品サイズ、効率、動作周波数のトレードオフがわかります。 $\Delta I_L$ を大きくするとインダクタの値を小さくできますが、インダクタのコア・ロスと出力コンデンサの ESR ロスが大きくなり、出力リップルも大きくなります。

インダクタの値は、公称入力電圧におけるピークtoピークのリップル電流  $\Delta I_L$ が定格チャンネル出力電流の $35\%\sim45\%$ になるように選択する必要があります。定格チャンネル出力電流は、個々のチャンネルでは2A、組み合わせチャンネルでは4Aです。式10を整形し、式11に従ってインダクタの値を選択します。

$$L = \left(\frac{V_{0UT}}{f_{SW} \cdot \Delta I_{I}}\right) \cdot \left(1 - \frac{V_{0UT}}{V_{IN}}\right)$$

(11)

過熱や効率低下を防ぐために、インダクタは、その実効電流 定格値がアプリケーションの予想最大出力負荷より大きい ものを選ぶ必要があります。また、効率を最大化するには、 インダクタの直列抵抗をできる限り小さくし、コア材をアプリ ケーションのスイッチング周波数に適したものにする必要が あります。

インダクタの飽和電流定格は、負荷にリップル電流の半分を加えた値より大きくなければなりません。このインダクタのピーク電流は、式12で計算できます。

$$I_{L(PEAK)} = I_{OUT(MAX)} + \frac{\Delta I_L}{2}$$

(12)

ここで、I<sub>OUT(MAX)</sub>は所定のアプリケーションにおける最大 出力電流です。

特定のアプリケーションに最適なインダクタは、この設計ガイドに示すものと異なる場合があります。十分な設計マージンを確保するために、選択したインダクタでアプリケーション回路を慎重に評価する必要があります。

#### 入力コンデンサの選択

降圧コンバータには入力電源から電流が流れますが、この電流は立上がり時間と立下がり時間が非常に短いパルスです。入力コンデンサは、入力の電圧リップルを低減し、EMIを最小化するために必要です。この機能のために、バイパス用にX7RまたはX5Rのセラミック・コンデンサを各降圧レギュレータのVINピンとグラウンドの間に配置する必要があります。最も効果的なのは、入力コンデンサがそのスイッチング周波数でロー・インピーダンスであって、リップル電流定格に適切であることです。

最も厳しい条件のリップル電流は、VOUTがVINの1/2のときに発生します。この条件下では、リップル電流は式13で与えられます。

$$I_{CIN(RMS)} = \frac{I_{OUT}}{2} \tag{13}$$

入力容量の適切な開始値は、チャンネル1と2が2.2 $\mu$ F、チャンネル3と4が1 $\mu$ Fです。

チャンネルを組み合わせる場合は、共有するチャンネルの $V_{\rm IN}$ ピン同士を接続し、組み合わせるチャンネルから供給される合計電流に基づいて入力コンデンサを選択する必要があります。

#### 出力コンデンサの選択

出力コンデンサは、次の2つの機能を実行します。1つは、インダクタ電流をフィルタ処理し、低リップル電圧の出力を生成します。2つ目は、エネルギーを蓄えて、トランジェント負荷時のドループとオーバーシュートを最小化します。LT8686Sの降圧コンバータは高周波で動作できるため、出力容量は最小限にする必要があります。内部補償された電流モード制御ループは安定していて、出力コンデンサの直列抵抗(ESR)を最小化する必要はありません。従って、セラミック・コンデンサを使用することができ、出力リップルは非常に小さくなります。

出力リップルの推定値はコンデンサの種類によって異なり、 式14と式15で表されます。

$$V_{RIPPLE} = \frac{\Delta I_{L}}{8 \cdot f_{SW} \cdot C_{OUT}}$$

(14)

セラミック・コンデンサでは、式14のようになります。

$$V_{RIPPIF} = \Delta I_{I} \bullet ESR \tag{15}$$

アルミ・コンデンサまたはタンタル・コンデンサでは、式 15のようになります。 $V_{RIPPLE}$ はピークtoピークの出力リップル、 $f_{SW}$ はスイッチング周波数 (MHz)、 $\Delta I_L$ はインダクタに流れるピークtoピークのリップル電流、COUTは出力コンデンサ値 ( $\mu$ F)、ESR は出力コンデンサの等価直列抵抗です。

セラミック・コンデンサは、ESRが低く、サイズが小さいため、 LT8686Sのアプリケーションに推奨されます。しかし、全ての

セラミック・コンデンサが同じというわけではありません。大容量コンデンサの多くは、温度係数や電圧係数の高い誘電体を使用しています。Y5VとZ5Uのタイプは、極端な印加電圧と温度の場合、静電容量が大きく失われます。ループ安定性、過渡応答、リップル、EMIは入出力コンデンサの値に依存するため、動作温度範囲に応じて、X5R(最大85℃)、X7R(最大125℃)、X8R(最大150℃)のコンデンサを使用することを推奨します。

また、電解コンデンサも選択肢のひとつです。ほとんどのアルミ電解コンデンサはESRが大きすぎて、出力リップルを低く抑えることができません。タンタル・コンデンサや電源用の低ESR有機電解コンデンサが適しています。必要な出力リップルに対応する十分低いESRのコンデンサを選択します。コンデンサは体積でESRが決まるので、同じようなリップル性能を持つセラミック・コンデンサよりサイズ、値共に大きくなります。

標準的応用例のセクションでは、出力コンデンサの値に関する妥当な出発点を示しています。 設計上のマージンを確保するために、各アプリケーションを慎重に評価する必要があります。

#### 昇圧コンデンサの選択

各チャンネルのBSTピンとSWピンの間にコンデンサを接続することで、内部パワー・デバイスを駆動するための約3.4Vの内部電源が生成されます。ほとんどのアプリケーションでは、0.1μFのセラミック・コンデンサで十分に機能します。

なお、基板上では、1つのインダクタを駆動するために、各 チャンネルのSWピンとBSTピンを接続しますが、堅牢な動 作のためには、組み合わせるチャンネルのそれぞれのBSTピンとSWピンの間に昇圧コンデンサをする必要があります。

#### 出力電圧のトラッキングとソフトスタート

LT8686Sは、起動時の出力電圧の立上がり時間を制御するプログラマブルなチャンネル・ソフトスタート機能と、チャンネルのパワー・グッド(PG)機能およびイネーブル(EN)機能とを組み合わせ、起動時のシーケンスや制御を柔軟に行

えるようにしています。また、ソフトスタート機能を使用することで、入力サージ電流を低減したり、出力電圧のオーバーシュートを防止したりできます。出力電圧のソフトスタート時間を設定するには、式16に従って、チャンネルのTRK/SSピンとグラウンドの間にコンデンサを接続します。

$$t_{SS} = \frac{C_{SS} \bullet 0.8V}{2\mu A} \tag{16}$$

ここで、 $2\mu A$ はTRK/SSプルアップ電流、 $C_{SS}$ はコンデンサの静電容量(F)です。

TRK/SSxピンは約300kでプルダウンされており、デバイスがシャットダウンされたときや特定のフォールト状態のときに、外付けのソフトスタート・コンデンサを放電させます。

出力電圧のトラッキングのために、チャンネルのTRK/SSピンを外部電圧源で駆動できます。具体的には、TRK/SSピンは、0V~0.8Vの電圧で駆動されると、エラー・アンプへの0.8V内部リファレンス入力をオーバーライドし、FB電圧をTRK/SSピンの電圧にレギュレーションします。TRK/SSピンの電圧が0.8Vよりも高くなると、トラッキングはディスエーブルされ、帰還電圧は内部リファレンス電圧にレギュレーションされます。

チャンネルを組み合わせる場合、スレーブ・チャンネルの TRK/SSピンはオープンにします。

### パワー・グッド・コンパレータ

LT8686Sの各チャンネルにはパワー・グッド・コンパレータが搭載されていて、オープンドレインのPGxピンに出力されます。各PGピンは、対応する帰還電圧がリファレンス電圧よりも7.5%以上高いか低い場合に、ローにプルダウンされます。各チャンネルのパワー・グッド閾値の詳細については、電気的特性の表を参照してください。デバイスがシャットダウンすると、全てのPGピンがローにプルダウンされます。各チャンネルのPGピンは、対応するENピンがローのとき、ローにプルダウンされます。

チャンネルを組み合わせる場合、マスタ・チャンネルのPGピンだけが有効になります。スレーブのPGピンはオープンにする必要があります。

#### PCBレイアウト

LT8686Sは、EMI/EMC放射を最小限に抑えながら、高周波数でのスイッチング時に最大限の効率が得られるように特別に設計されています。

適切な動作と最小のEMIを確保するためプリント回路基板のレイアウト時には注意が必要です。推奨基板レイアウトは、最新のLT8686Sデモ・ボードで入手できます。本セクションの残りの部分で、一般的なガイドラインをいくつかご紹介します。

アプリケーション回路の下に切れ目のないグランド・プレーンを表面層に最も近い層に局部的に配置し、露出したGNDパッドをこの層に接続します。基板グラウンドへの熱および電気インピーダンスを低減するため、露出パッドのグラウンド接続は、可能な限り多くのビアを用いて行います。最高性能を得るためには、LT8686Sの近傍で基板グランド・プレーンを切れ目なく最大にします。

SWとBSTのノードはできるだけ小さくして、高感度なパターンへのノイズ結合を最小にする必要があります。RTピンおよび全てのFBピンに接続するパターンは最小限にし、こうした敏感なノードへのノイズ結合を最小化するために、必要に応じてグラウンド・シールドを施します。

それぞれの降圧レギュレータには、入力バイパス・コンデンサを $V_{INx}$ ピンの近くに配置し、上記のグランド・プレーンを介して露出パッドに低インピーダンスで接続します。

4層基板で推奨されるレイヤは次のとおりです。

- ・レイヤ1(部品):2オンス(70μm)の銅を使用します。SW およびBSTノードの配線と、インダクタおよび入出力コン デンサの配置を含め、高周波/大電流配線が途切れなく連続になるようにします。他はグラウンドで埋めます。

- レイヤ2(内部):切れ目のないグランド・プレーン。

- レイヤ3(内部):信号の配線(他はグランド・プレーン)。

- レイヤ4(底面):2オンス(70μm)の銅を使用します。残りの信号配線に使用し、他はグラウンドで埋めます。

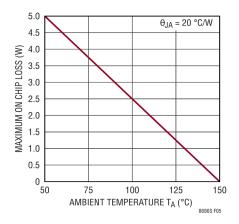

#### 熱に関する考慮事項

露出パッドは、シリコン・ダイからPC基板や周囲の空気に熱を伝導させる経路となります。熱伝導をよくするために、デバイスの下にサーマル・ビアを配置して、内部のグランド・プレーンや基板の裏側まで熱を伝導させる必要があります。ビアの銅メッキは、ビアの容積を埋める埋めないに関わらずハンダよりはるかに優れた導電体であるため、少数の大きなビアよりも多数の小さなビアの方が効果的です。プレーンは、広い面積に熱を分散させます。

LT8686S内の消費電力は、パッケージの熱抵抗θJA(℃/W) に比例して、ジャンクション温度を周囲温度以上に上昇させます。LT8686S内の消費電力は、総電力損失を計算し、それからインダクタのDCR損など、LT8686Sの外付け部品での電力損失を差し引くことで、効率の測定結果から推定できます。次に、推定したLT8686Sの電力損失にパッケージのθJAを乗じ、その結果にアプリケーションの最大周囲温度を加算すると、最大動作ジャンクション温度が算出されます。

優れた基板設計では、20°C/WのθJAを実現できます。最大ジャンクション温度の計算で、LT8686Sが許容ジャンクション温度付近かそれ以上で動作することが示された場合、より高精度な熱モデリングが必要になることがあります。あるいは、ダイのジャンクション温度を下げるための設計変更を行う必要があります。設計変更には、VVINxの低減、fswの低減、または動作負荷電流の低減などがあります。負荷電流の低減は、直接負荷電流を減少させるか、デューティ・サイクルを低下させるか、最大負荷電流が発生する期間を短

縮することで実現できます。また、ダイ・ジャンクション温度は、周囲温度を下げるかエア・フローを追加することで低下させることができます。 図 5 は、 $\theta_{JA}=20$ °C/Wとして、所定の周囲温度に対するオンチップ許容損失の近似値を示しています。

LT8686Sは、サーマル・シャットダウン機能を内蔵しており、ダイ温度が約177℃まで上昇するとスイッチングを停止します。温度が約5℃下がるとスイッチングを再開します。この機能は製造試験を行っておらず、フェイルセーフとしてのみ使用されることを意図しています。

図5.最大損失と周囲温度の関係

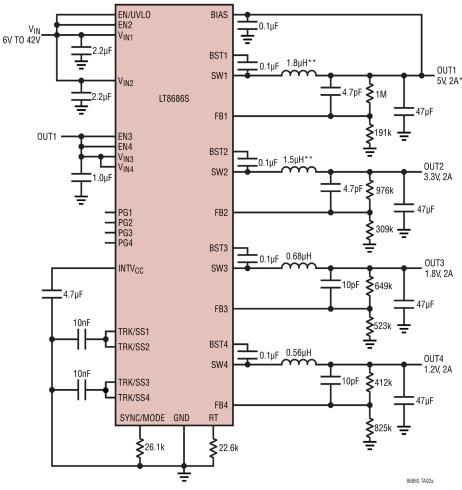

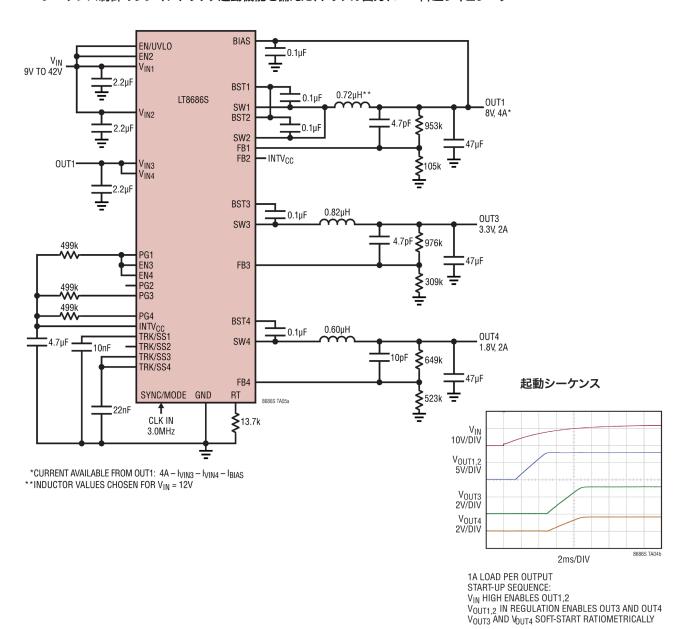

スペクトラム拡散およびレシオメトリック出力起動機能を備えた、42V入力、クワッド出力、2MHz 降圧レギュレータ (表紙に示したアプリケーションの詳細図)

\*CURRENT AVAILABLE FROM OUT1: 2A - IVIN3 - IVIN4 - IBIAS

\*\*INDUCTOR VALUES CHOSEN FOR V<sub>IN</sub> = 12V

#### 起動シーケンス

START-UP SEQUENCE:  $V_{\rm IN}$  HIGH ENABLES HV CHANNELS HV CHANNELS TRACK RATIOMETRICALLY  $V_{\rm OUT1}$  HIGH ENABLES LV CHANNELS LV CHANNELS TRACK RATIOMETRICALLY

Rev. A

22

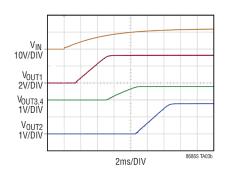

#### 電源シーケンス機能を備えたコンパクトなマイクロコントローラ電源

#### 起動シーケンス

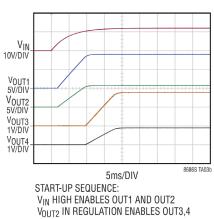

1A LOAD PER OUTPUT START-UP SEQUENCE: V<sub>IN</sub> HIGH ENABLES OUT1 V<sub>OUT1</sub> IN REGULATION ENABLES OUT3,4 V<sub>OUT3,4</sub> IN REGULATION ENABLES OUT2

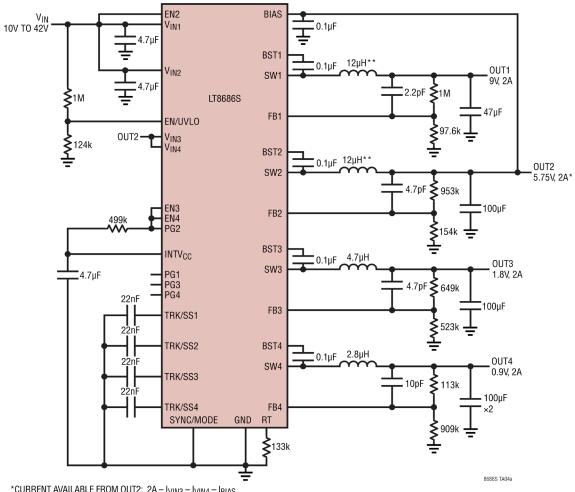

#### 複数のLDOまたはリモート回路の駆動に適した高効率クワッド出力レギュレータ

\*CURRENT AVAILABLE FROM OUT2:  $2A - I_{VIN3} - I_{VIN4} - I_{BIAS}$  \*\*INDUCTOR VALUES CHOSEN FOR  $V_{IN}$  = 12V

#### 起動シーケンス

LOFN 32 1020 REV B

## パッケージの説明

32-Lead (5mm  $\times$  5mm  $\times$  0.95mm) (Reference LTC DWG # 05-08-7048 Rev B)

**LQFN Package**

4 METAL FEATURES UNDER THE SOLDER MASK OPENING NOT SHOWN SO AS NOT TO OBSCURE THESE TERMINALS AND HEAT FEATURES PIN 1 NOTCH 0.2 × 45° DETAILS OF PIN 1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE ZONE INDICATED. THE PIN 1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE THE EXPOSED HEAT FEATURE IS SEGMENTED AND ARRANGED IN A MATRIX FORMAT. IT MAY HAVE OPTIONAL CORNER RADII ON EACH SEGMENT SEE NOTES SEE NOTES 6 NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994 | X | Z | (M) ⊃⊃⊃ | ⊕ PACKAGE IN TRAY LOADING ORIENTATION CORNER SUPPORT PAD CHAMFER IS OPTIONAL 0.37 0.20 DETAIL A PACKAGE BOTTOM VIEW  $\subset$ 3. PRIMARY DATUM -Z- IS SEATING PLANE 2. ALL DIMENSIONS ARE IN MILLIMETERS 0.37 <u>10</u> -1.63 0.375 COMPONENT\_ PIN 1 TRAY PIN 1, BEVEL → e ← ← Ó SUBSTRATE THK MOLD CAP HT e e/2 NOTES 0.10 0.10 0.15 MAX 0.50 0.03 0.10 1.04 0.28 DIMENSIONS 0.25 REF MOM 0.40 5.00 5.00 3.46 3.46 0.50 0.70 REF 0.25 0.95 DETAIL C DETAIL C SUBSTRATE 0.30 M 0.86 0.22 DETAIL B SYMBOL MOLD aaa bbb ddd ddd ## Ξ 무 1 Ш Z |qqq |// --- 0.750 --- 0.750 --1.2501.750 F -Ш SUGGESTED PCB LAYOUT TOP VIEW 0.20 -1.63-PACKAGE TOP VIEW 057.0 0.20 Z×C aaa Z PACKAGE OUTLINE 0.25 REF 0.70 REF-CORNER 5 5.50 ±0.05

# LT8686S

## 改訂履歴

| 改訂日   | 説明      | 改訂ページ |

|-------|---------|-------|

| 02/23 | ピン配置を更新 | 2     |

シーケンス制御のレシオメトリック起動機能を備えた、トリプル出力、3MHz 降圧レギュレータ

## 関連製品

| 製品番号   | 概要                                                                                           | 注釈                                                                                                            |

|--------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| LT8601 | 42V、効率94%、2.2MHzトリプル出力(1.5A + 2.5A + 1.8A)、同期整流式マイクロパワー降圧 DC/DC コンバータ(I <sub>Q</sub> = 30μA) | $V_{IN}$ : $3V\sim42V$ , $V_{OUT(MIN)}=0.8V$ , $I_Q=30\mu A$ , $I_{SD}<25\mu A$ , $6mm\times6mm$ QFN-40 パッケージ |

| LT8602 |                                                                                              | $V_{IN}$ : $3V\sim42V$ , $V_{OUT(MIN)}=0.8V$ , $I_Q=25\mu A$ , $I_{SD}<25\mu A$ , $6mm\times6mm$ QFN-40 パッケージ |

| LT8603 | 42V、低IQ、クワッド出力、トリプル・モノリシック降圧コンバータおよび昇<br>圧コントローラ                                             | $V_{IN}: 3V\sim 42V$ 、 $V_{OUT(MIN)}=0.8V$ 、 $I_Q=25\mu A$ 、 $I_{SD}<25\mu A$ 、6mm × 6mm QFN-40 パッケージ         |