# 入力遮断機能と PassThru 機能を備えた 40V、9A、低 Igの同期整流式昇圧 Silent Switcher

# 特長

- ▶ Silent Switcher™アーキテクチャ

- ▶ 超低 EMI 放射

- ▶ オプションのスペクトラム拡散周波数変調

- ▶ 40V、9Aのパワー・スイッチを内蔵

- ▶ 出力短絡保護/突入電流低減

- ▶ 広い入力電圧範囲:2.8V~40V

- ▶ 出力電圧:最大 36V までプログラム可能

- ▶ オプションの 2本のピンで 21 通りの出力電圧を選択可能

- 低 V<sub>IN</sub> ピン静止電流:

- シャットダウン時 350nA、Burst Mode 時 9µA、 PassThru™時 12µA (V<sub>IN</sub> ≥ V<sub>OUT</sub>)

- ▶ 100%のデューティ・サイクルで動作可能

- ▶ 調整と同期が可能:300kHz~3MHz

- ▶ 軽負荷時はパルススキッピング・モードまたは Burst Mode

- ▶ 出力ソフトスタートおよびパワー・グッド・モニタリング

- ▶ 小型 24 ピン (4mm×4mm) LQFN パッケージ

# アプリケーション

- ▶ 自動車用および工業用電源

- ▶ 汎用昇圧

# 概要

LT®8342 は、低  $I_Q$ の同期整流式昇圧 DC/DC コンバータです。このデバイスは、高スイッチング周波数で高い効率を実現しながら電磁干渉 (EMI) の放射を最小限に抑える Silent Switcher アーキテクチャを採用しており、オプションでスペクトラム拡散周波数変調機能を使用することができます。出力短絡保護および突入電流低減機能はオプションです。

広い入出力電圧範囲、Burst Mode 動作時の低  $V_{\rm IN}$  ピン静止電流、PassThru 動作( $V_{\rm IN} \ge V_{\rm OUT}$ )時における同期 MOSFET の 100% デューティ・サイクル能力といった特長を備えているため、LT8342 は汎用昇圧アプリケーションや自動車用事前昇圧アプリケーションに最適なデバイスとなっています。

帰還ループの  $V_{\text{OUT}}$  静止電流を削減するために、オプションの内部抵抗分圧器 ( $\geq 10 \text{M}\Omega$ ) と 2 本のピンで 21 種類の出力電圧レベルを選択できます。

LT8342 は 40V、9A のパワー・スイッチを内蔵しており、300kHz~3MHz の範囲にプログラム可能なスイッチング周波数で動作します。外部クロックに同期することも可能です。

LT8342 は、プログラマブル出力ソフトスタート、出力パワー・グッド・フラグ、および出力過電圧ロックアウト機能を備えています。

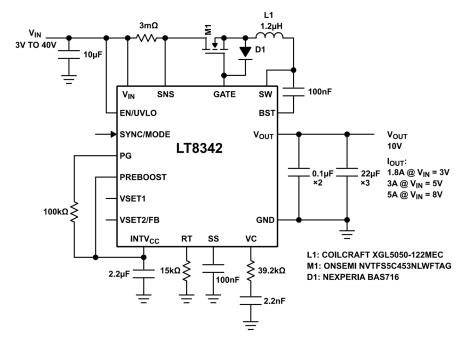

# 標準的応用例

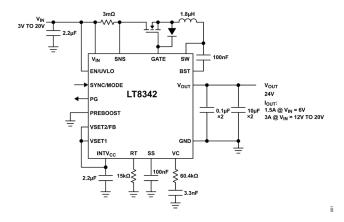

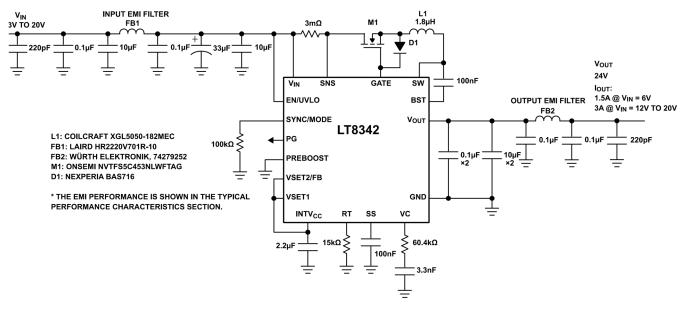

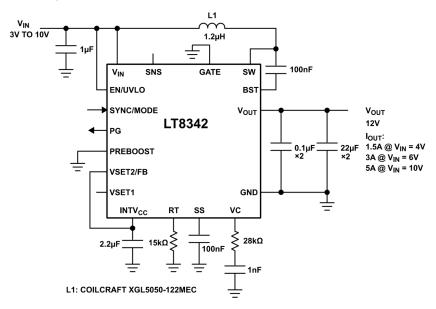

図 1. 出力短絡保護機能を備えた 2MHz、24V の昇圧コンバータ

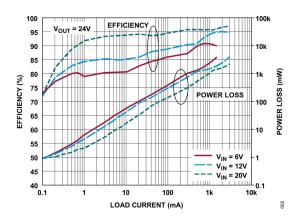

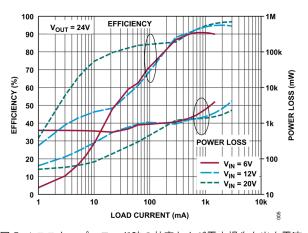

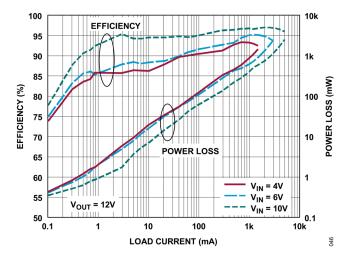

図 2. Burst Mode 時の効率および電力損失と負荷電流の関係 (SYNC/MODE = 0V)

# 目次

| 符支                                                   | 1  |

|------------------------------------------------------|----|

| アプリケーション                                             | 1  |

| 概要                                                   | 1  |

| 標準的応用例                                               | 1  |

| 改訂履歴                                                 | 3  |

| 仕様                                                   | 4  |

| 絶対最大定格                                               | 7  |

| 熱抵抗                                                  | 8  |

| 静電放電 (ESD)                                           | 8  |

| ESD 定格                                               | 8  |

| ESD に関する注意                                           | 8  |

| ピン配置およびピン機能の説明                                       | 9  |

| 代表的な性能特性                                             | 12 |

| ブロック図                                                | 19 |

| 動作原理                                                 | 20 |

| アプリケーション情報                                           | 21 |

| EN/UVLO ピンによる $V_{ m IN}$ オン/オフ閾値のプログラミング            | 21 |

| INTV <sub>cc</sub> レギュレータ                            | 21 |

| 出力電圧のプログラミング                                         | 21 |

| 軽負荷電流時の動作 — Burst Mode またはパルススキッピング・モード              | 22 |

| スイッチング周波数のプログラミングと同期                                 |    |

| スペクトラム拡散周波数変調                                        |    |

| V <sub>IN</sub> -V <sub>OUT</sub> PassThru モード動作     |    |

| $ m V_{IN}$ が $ m V_{OUT}$ に近付いた場合のスイッチング周波数フォールドバック | 24 |

| 出力短絡保護                                               |    |

| スタートアップ                                              |    |

| ループ補償                                                | 25 |

| 熱に関する考慮事項                                            | 25 |

| 過熱ロックアウト                                             | 26 |

| インダクタの選択                                             | 26 |

| 入力コンデンサの選択                                           | 26 |

| 出力コンデンサの選択                                           | 27 |

| 推奨 PCB レイアウトのガイドライン                                  | 27 |

| 標準的応用例                                               | 29 |

# データシート

| 低 IQ、低 EMI の SSFM 機能付き 24V 昇圧コンバータ                          | 29 |

|-------------------------------------------------------------|----|

| 2MHz、12V の昇圧コンバータ                                           | 30 |

| 出力短絡保護機能を備えた 500kHz、36V、低 I <sub>Q</sub> の昇圧コンバータ           | 31 |

| 10V 出力と短絡保護機能を備え、ストップ・スタートやコールド・クランクに適した自動車用 2MHz 事前昇圧コンバータ | 32 |

| パッケージ情報                                                     | 33 |

| オーダー・ガイド                                                    | 34 |

| 関連製品                                                        | 35 |

# 改訂履歴

| 版数    | 改訂日  | 説明   | 改訂ページ |

|-------|------|------|-------|

| Rev 0 | 6/24 | 初版発行 | _     |

analog.com.jp Rev 0 | 3 of 36

# 仕様

表 1. 電気的特性

(特に指定のない限り、仕様は  $T_J = 25$ °C、 $V_{IN} = SNS = EN/UVLO = 5$ V での値  $^1$ )

| PARAMETER                                     | CONDITIONS                                                        | COMMENTS                       | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------|-------------------------------------------------------------------|--------------------------------|------|------|------|-------|

| V <sub>IN</sub> SUPPLY                        |                                                                   |                                |      |      |      |       |

| V <sub>IN</sub> Operating Range               |                                                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C | 2.8  |      | 40   | V     |

| V <sub>IN</sub> Quiescent Current in Shutdown | EN/UVLO < 0.15V                                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C |      | 0.35 | 1.2  | μΑ    |

|                                               | SYNC/MODE = 0V                                                    |                                |      | 9    | 15   | μΑ    |

| V <sub>IN</sub> Quiescent Current             | (Burst Mode)                                                      | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 20   | μΑ    |

| During Zero Load                              | SYNC/MODE = INTV <sub>CC</sub>                                    |                                |      | 1.9  | 2.5  | mA    |

| Conditions (No<br>Switching), without         | (Pulse-Skipping<br>Mode)                                          | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 3    | mA    |

| external N-Channel<br>FET (GATE = 0V)         | $V_{IN} = 10.1V, V_{OUT} \le 10V$                                 |                                |      | 12   | 20   | μΑ    |

| TET (GATE - 0V)                               | (PassThru),<br>FB = 1.2V                                          | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 30   | μΑ    |

|                                               | SYNC/MODE = 0V<br>t Current (Burst Mode)                          |                                |      | 28   | 40   | μΑ    |

| V <sub>IN</sub> Quiescent Current             |                                                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 50   | μΑ    |

| During Zero Load                              | SYNC/MODE = INTV <sub>CC</sub><br>(Pulse-Skipping<br>Mode)        |                                |      | 1.9  | 2.5  | mA    |

| Conditions (No<br>Switching), with            |                                                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 3    | mA    |

| external N-Channel<br>FET                     | $V_{IN} = 10.1V, V_{OUT} \le 10V$                                 |                                |      | 26.5 | 40   | μΑ    |

|                                               | (PassThru),<br>FB = 1.2V                                          | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 55   | μΑ    |

| ENABLE/UNDERVOLT                              | AGE LOCKOUT (UVLO)                                                |                                |      |      |      |       |

| UVLO Threshold                                | EN/UVLO Falling                                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C | 0.96 | 1.02 | 1.08 | V     |

| Voltage                                       | Hysteresis                                                        |                                |      | 62   |      | mV    |

| EN/UVLO Pin Bias<br>Current                   | EN/UVLO = 1V                                                      | -40°C ≤ T <sub>J</sub> ≤ 150°C | -10  |      | 10   | nA    |

| ERROR AMPLIFIER, SO                           | OFT START, AND INTERI                                             | NAL FEEDBACK                   |      |      |      | •     |

| Feedback Reference<br>Voltage                 |                                                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C | 0.99 | 1    | 1.01 | V     |

| Reference Voltage<br>Line Regulation          | $\Delta V_{FB}/\Delta V_{IN}$ , $2.8V \le V_{IN} \le 40V$         |                                |      | 0    | 10   | μV/V  |

| VSET2/FB Pin Bias<br>Current                  | VSET1 Pin is connected to INTV <sub>cc</sub> through $100k\Omega$ |                                | -10  |      | 10   | nA    |

analog.com.jp Rev 0 | 4 of 36

| PARAMETER                                                  | CONDITIONS                      | COMMENTS                       | MIN  | TYP  | МАХ  | UNITS |

|------------------------------------------------------------|---------------------------------|--------------------------------|------|------|------|-------|

| Error Amplifier<br>Transconductance<br>(gm <sub>EA</sub> ) |                                 |                                |      | 160  |      | μS    |

| Error Amplifier<br>Voltage Gain                            |                                 |                                |      | 600  |      | V/V   |

| Power Stage<br>Transconductance<br>(gmp)                   |                                 |                                |      | 14.7 |      | S     |

| Error Amplifier<br>Source/Sink Current                     |                                 |                                |      | 36   |      | μΑ    |

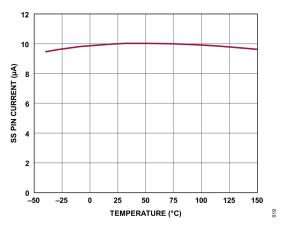

| Soft-Start Pin<br>Current                                  | SS = 0.5V                       | -40°C ≤ T <sub>J</sub> ≤ 150°C | 9.1  | 10   | 10.5 | μΑ    |

| V <sub>out</sub> Accuracy with<br>Internal Feedback        |                                 | -40°C ≤ T <sub>J</sub> ≤ 150°C | -2   |      | 2    | %     |

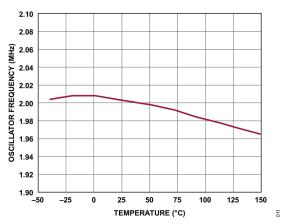

| OSCILLATOR AND SPR                                         | EAD SPECTRUM FRE                | QUENCY MODULATION (S           | SFM) |      |      |       |

| Switching<br>Frequency Range                               |                                 | -40°C ≤ T <sub>J</sub> ≤ 150°C | 0.3  |      | 3.0  | MHz   |

| Constantin                                                 | RT = 110kΩ                      | -40°C ≤ T <sub>J</sub> ≤ 150°C | 270  | 300  | 330  | kHz   |

| Switching<br>Frequency (f <sub>osc</sub> )                 | RT = 31.6kΩ                     | -40°C ≤ T <sub>J</sub> ≤ 150°C | 0.95 | 1    | 1.05 | MHz   |

| (1030)                                                     | RT = 15kΩ                       | -40°C ≤ T <sub>J</sub> ≤ 150°C | 1.9  | 2    | 2.1  | MHz   |

| SSFM Mode<br>Frequency<br>Deviation                        | $\Delta f/f_{OSC} \times 100\%$ | RT = 15kΩ                      |      | 13   | 20   | %     |

| SYNC/MODE                                                  |                                 |                                |      |      |      | •     |

| SYNC Logic Level                                           | SYNC Logic High                 | -40°C ≤ T <sub>J</sub> ≤ 150°C | 1.7  |      |      | V     |

| STIVE LOGIC LEVEL                                          | SYNC Logic Low                  | -40°C ≤ T <sub>J</sub> ≤ 150°C |      |      | 0.4  | V     |

| f <sub>SYNC</sub> /f <sub>OSC</sub> allowed ratio          |                                 |                                | 0.9  | 1    | 1.25 |       |

| INTERNAL NMOS POW                                          | ER SWITCHES                     |                                |      |      |      |       |

| Bottom Switch<br>On-Resistance                             | I <sub>SW</sub> = 2A            |                                |      | 25   |      | mΩ    |

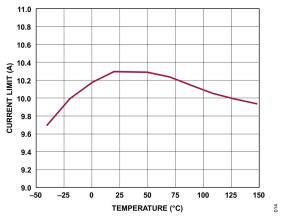

| Bottom Switch Peak<br>Current Limit                        |                                 | -40°C ≤ T <sub>J</sub> ≤ 150°C | 9    | 10.3 | 11   | А     |

| Bottom Switch<br>Minimum Off-Time                          |                                 | -40°C ≤ T <sub>J</sub> ≤ 150°C | 20   | 35   | 50   | ns    |

analog.com.jp Rev 0 | 5 of 36

(特に指定のない限り、仕様は  $T_J = 25^{\circ}C$ 、 $V_{IN} = SNS = EN/UVLO = 5V$  での値  $^{1}$ )

| PARAMETER                                                   | CONDITIONS                                   | COMMENTS                         | MIN  | TYP | MAX  | UNITS |

|-------------------------------------------------------------|----------------------------------------------|----------------------------------|------|-----|------|-------|

| Bottom Switch<br>Minimum On-Time                            | $V_{IN} = 9.5V, V_{OUT} = 10V$               |                                  |      | 60  |      | ns    |

| Top Switch<br>On-Resistance                                 | $BST - SW = 4V,$ $I_{SW} = 2A$               |                                  |      | 30  |      | mΩ    |

| OUTPUT POWER GOO                                            | D AND OVERVOLTAGE L                          | оскоит                           |      |     |      |       |

| Power Not Good                                              | FB Rising                                    | -40°C ≤ T <sub>J</sub> ≤ 150°C   | 7    | 11  | 15   | %     |

| High (Outside this<br>Window) <sup>2</sup>                  | Hysteresis                                   |                                  |      | 3   |      | %     |

| Power Not Good                                              | FB Falling                                   | -40°C ≤ T <sub>J</sub> ≤ 150°C   | -13  | -9  | -5   | %     |

| Low (Outside this Window)                                   | Hysteresis                                   |                                  |      | 3   |      | %     |

| PG Leakage Current                                          | PG = 20V                                     |                                  |      |     | 1    | μΑ    |

| PG Pull-Down<br>Voltage                                     | 1mA current (into the pin)                   |                                  | 200  | 400 | 600  | mV    |

| V <sub>оит</sub> Over-Voltage<br>Lockout (Rising)           | Normalized to target or 36V                  | -40°C ≤ T <sub>J</sub> ≤ 150°C   | 107  | 111 | 115  | %     |

| INPUT DISCONNECT                                            |                                              |                                  |      | 1   | •    |       |

| GATE Drive Voltage                                          | V <sub>IN</sub> = 3V, 1μA out of<br>GATE pin | -40°C ≤ T <sub>J</sub> ≤ 150°C   | 3.2  | 5   | 7    | V     |

| (GATE – V <sub>IN</sub> )                                   | V <sub>IN</sub> ≥ 5V, 1μA out of<br>GATE pin | -40°C ≤ T <sub>J</sub> ≤ 150°C   | 4.5  | 6.5 | 8.5  | V     |

| GATE to V <sub>IN</sub> Clamp<br>Voltage                    | GATE-V <sub>IN</sub> , 5mA into<br>GATE pin  |                                  | 13   | 15  | 17   | V     |

| GATE Turn-On<br>Pull-Up Current                             | GATE = 0V                                    |                                  | 5    | 9   | 13   | μΑ    |

| Over-Current Trip<br>Voltage (ΔV <sub>SNS</sub> )           | $\Delta V_{SNS} = V_{IN} - SNS$              | -40°C ≤ T <sub>J</sub> ≤ 150°C   | 37.5 | 45  | 52.5 | mV    |

| Over-Current Event<br>to GATE Turn-Off<br>Propagation Delay |                                              |                                  |      | 450 |      | ns    |

| GATE Turn-Off                                               | CATE - 5V                                    | During Over-Current<br>Condition | 80   | 135 | 190  | mA    |

| Pull-Down Current                                           | GATE = 5V                                    | During Time-Out<br>Period        |      | 20  |      | mA    |

| GATE Retry Hiccup<br>Time                                   |                                              |                                  |      | 40  |      | ms    |

<sup>&</sup>lt;sup>1</sup> LT8342R は、-40℃≤T<sub>J</sub>≤150℃の動作ジャンクション温度範囲で仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下します。この仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。

analog.com.jp Rev 0 | 6 of 36

<sup>&</sup>lt;sup>2</sup> PreBoost ピンを INTVccに接続すると、ロー側ウィンドウから外れた場合のみ PG がプルダウンされます。

### 絶対最大定格

#### 表 2. 絶対最大定格

| PARAMETER                                                           | RATING                     |

|---------------------------------------------------------------------|----------------------------|

| V <sub>IN</sub> , SNS, EN/UVLO, V <sub>OUT</sub> , SW, PG, VSET2/FB | -0.3V to 40V               |

| GATE                                                                | -0.3V to Note <sup>1</sup> |

| BST                                                                 | -0.3V to SW + 4V           |

| V <sub>IN</sub> to SNS                                              | -1V to 1V                  |

| SYNC/MODE                                                           | -0.3V to 6V                |

| PreBoost, VSET1, SS                                                 | -0.3V to 4V                |

| VC, RT                                                              | -0.3V to 2V                |

| Operating Junction Temperature Range: LT8342R <sup>2,3</sup>        | -40°C to 150°C             |

| Storage Temperature Range                                           | -65°C to 150°C             |

| Peak Solder Reflow Package Body Temperature                         | 260°C                      |

<sup>1</sup> 外部電圧源を接続しないでください。入力遮断機能を使用しない場合は GATE ピンをグラウンドに接続します。

上記の絶対最大定格を超えるストレスを加えるとデバイスに恒久的な損傷を与えることがあります。これらはストレス定格のみを定めたものであり、この仕様の動作のセクションに記載する規定値以上でデバイスが正常に動作することを示唆するものではありません。デバイスを長時間にわたり絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

analog.com.jp Rev 0 | 7 of 36

<sup>&</sup>lt;sup>2</sup> LT8342R は、-40℃~150℃ の動作ジャンクション温度範囲で仕様規定されています。ジャンクション温度が高い場合は動作寿命が低下します。ここに示す仕様に見合った最大周囲温度は、具体的な動作条件と、ボード・レイアウト、パッケージの熱抵抗定格値、およびその他の環境条件の組み合わせによって決まります。

<sup>3</sup> LT8342R は、一時的な過負荷状態からデバイスを保護することを目的とした過熱保護機能を内蔵しています。ジャンクション温度が最大動作ジャンクション温度を超えそうになると、過熱保護機能が作動します。仕様規定された最大動作ジャンクション温度を超えて連続動作させると、デバイスの信頼性を損なうおそれがあります。

### 熱抵抗

熱性能は、PCBの設計と動作環境に直接関連します。PCBの熱設計には細心の注意が必要です。

#### 表 3. 熱抵抗

| BOARD TYPE  | $oldsymbol{	heta}_{JA}$ | θ <sub>JC_TOP</sub> | θ <sub>ЈС_ВОТ</sub> | UNIT |

|-------------|-------------------------|---------------------|---------------------|------|

| JEDEC BOARD | 38                      | 44                  | 7                   | °C/W |

| DEMO BOARD  | 22                      | _                   | _                   | °C/W |

# 静電放電 (ESD)

以下の ESD 情報は、ESD に敏感なデバイスを取り扱うために示したものですが、対象は ESD 保護区域内だけに限られます。人体モデル (HBM) は ANSI/ESDA/JEDEC JS-001 に、デバイス帯電モデル (CDM) は ANSI/ESDA/JEDEC JS-002 に準拠しています。

### ESD 定格

表 4. LT8342、24 ピン(4mm×4mm)LQFN

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| НВМ       | ±4000                   | 3A    |

| CDM       | ±1250                   | C3    |

### ESD に関する注意

ESD(静電放電)の影響を受けやすいデバイスです。

電荷を帯びたデバイスや回路ボードは、検知されないまま放電することがあります。本製品は当社独自の特許技術である ESD 保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、損傷を生じる可能性があります。 したがって、性能劣化や機能低下を防止するため、ESD に対する適切な予防措置を講じることをお勧めします。

analog.com.jp Rev 0 | 8 of 36

# ピン配置およびピン機能の説明

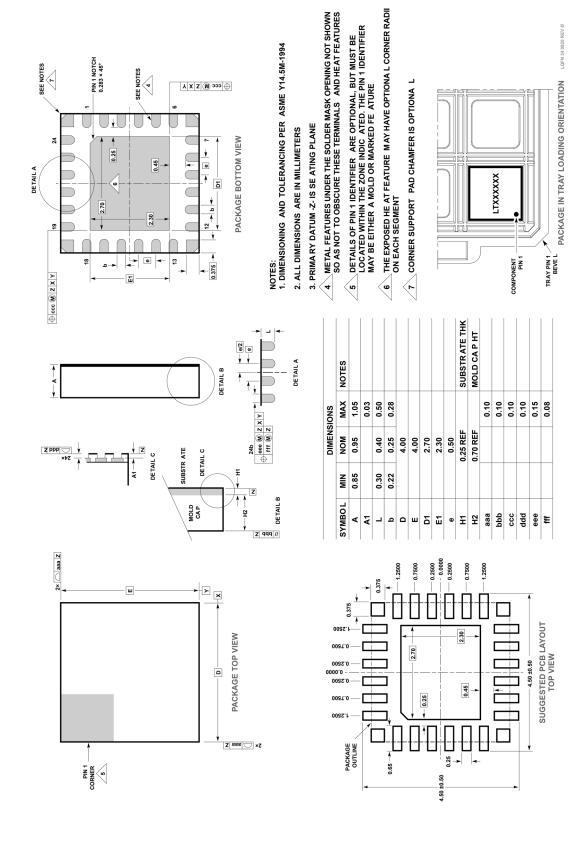

24-LEAD (4mm × 4mm) PLASTIC LQFN PACKAGE NOTE: EXPOSED PAD (PIN 25) IS GND, MUST BE SOLDERED TO PCB FOR OPTIMAL THERMAL PERFORMANCE

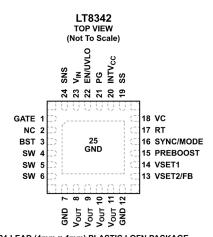

図 3. ピン配置

003

表 5. 端子説明

| ピン                       | 名称               | 説明                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | GATE             | 入力遮断用外部 N チャンネル電界効果トランジスタ(FET)のゲート・ドライバ・ピン。このピンは外部<br>FET のゲートに接続します。外部 FET のゲートとソース間のクランプにはダイオードが必要です。このピンの電圧は 9µA の内部電流源によって V <sub>IN</sub> + 6.5V まで上がります。このピンを直接駆動したり、直接負荷をかけたりしないでください。また、入力遮断 FET とグラウンドの間にコンデンサを置かないでください。外部 FET を使わない場合、GATE ピンはグラウンドに接続します。                                                                                                                                                           |

| 2                        | NC               | 内部接続されていません。                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3                        | BST              | 上側スイッチ・ドライバの電源ピン。容量 100nF、低等価直列抵抗(ESR)のセラミック・コンデンサを<br>BST ピンと SW ピンの間に接続します。接続は BST ピンにできるだけ近付けて行ってください。                                                                                                                                                                                                                                                                                                                       |

| 4, 5, 6                  | SW               | 内部パワー・スイッチの出力ピン。これは、内部ローサイド NMOS パワー・スイッチのドレインまたはハイサイド NMOS パワー・スイッチのソースです。EMI を最小限に抑えるために、金属配線パターンの面積は最小限に抑えてください。                                                                                                                                                                                                                                                                                                             |

| 7, 12, Exposed<br>Pad 25 | GND              | グラウンド・ピン。このパッケージはデバイス底面に露出パッドを備えており、このパッドがパッケージから出る熱と電流の最良の経路になっています。LT8342のダイ温度を下げて電力性能を向上させるには、これらのピンをデバイス下面にある切れ目のない銅のグランド・プレーンにハンダ付けする必要があります。GND リターンを最適化して Silent Switcher の能力を最大限に引き出すには、アプリケーション情報のセクションに示す推奨 PCB レイアウトのガイドラインを参照してください。                                                                                                                                                                                |

| 8, 9, 10, 11             | V <sub>out</sub> | コンバータの出カピン。 $V_{OUT}$ ピンの電圧リップルを適切な範囲まで除去するには、GND との間に、大容量で低 ESR のセラミック・コンデンサ( $\geq 4.7 \mu F$ )を接続する必要があります。更に、Silent Switcher の性能を最大限に引き出すために、2 つの小さなセラミック・コンデンサ( $0.1 \mu F$ )を $V_{OUT}$ と GND の間にローカルで配置することを推奨します。アプリケーション情報のセクションにある推奨 PCB レイアウトのガイドラインを参照してください外部帰還を使用する場合は( $100 k\Omega$ を介して VSET1 を INTV $_{CC}$ に接続)、 $V_{OUT}$ と GND の間にある抵抗分圧器回路を使って $V_{OUT}$ を設定します。抵抗分圧器の中間点は VSET2/FB ピン( $1V$ に安定化)に接続します。 |

analog.com.jp Rev 0 | 9 of 36

出力電圧設定 2/外部帰還ピン。内部帰還を使用する場合、VSET2/FB ピンは表 6 に示すように設定しま す。外部帰還を使用する場合は(100kΩを介して VSET1 を INTV<sub>CC</sub> に接続)、V<sub>OUT</sub> と GND の間にある抵 抗分圧器回路にこのピンを接続して、目的の V<sub>OUT</sub>電圧に設定します。LT8342 は VSET2/FB ピンを 1V (代表値)に安定化します。 表 6. 目標 Vour 設定 VSET1 VSET2/FB Target V<sub>OUT</sub> 4V **GND GND GND**  $100k\Omega$  to GND GND Open 5V 7V **GND**  $100k\Omega$  to  $INTV_{\text{CC}}$ **GND**  $\mathsf{INTV}_{\mathsf{CC}}$ Open **GND** 9V Open  $100k\Omega$  to GND 14V Open 10V Open VSET2/FB 13 Open  $100k\Omega$  to  $INTV_{CC}$ 16V Open  $INTV_{CC}$ 12V **GND**  $INTV_{CC}$ 18V  $100k\Omega$  to GND  $\mathsf{INTV}_{\mathsf{CC}}$ 22V  $\mathsf{INTV}_{\mathsf{CC}}$ 20V Open  $\mathsf{INTV}_{\mathsf{CC}}$  $100k\Omega$  to  $INTV_{CC}$ 26V  $INTV_{CC}$  $INTV_{CC}$ 24V  $100k\Omega$  to GND **GND** 28V  $100k\Omega$  to GND  $100k\Omega$  to GND 32V  $100k\Omega$  to GND Open 30V  $100 k\Omega$  to  $INTV_{\text{CC}}$  $100k\Omega$  to GND 34V  $100k\Omega$  to GND  $\mathsf{INTV}_{\mathsf{CC}}$ 36V  $100k\Omega$  to  $INTV_{\text{CC}}$ **GND** 19V  $100k\Omega$  to INTV<sub>CC</sub> FΒ 外部帰還 外部電圧設定1ピン。内部帰還を使用する場合は、このピンを表6に示すように設定します。外部帰還を VSET1 14 使用する場合は、100k $\Omega$ の抵抗を介してこのピンを INTV $_{CC}$ に接続してください。 事前昇圧アプリケーション用の PG モード・ピン。このピンを GND に接続した場合、Vouтがその目標値  $\pm 10\%$ のウィンドウを外れると PG ピンがプルダウンされます。このピンを  $\mathsf{INTV}_{\mathsf{CC}}$ に接続した場合は、 15 **PREBOOST**

analog.com.jp Rev 0 | 10 of 36

Vourが目標電圧の-10%未満になったときにのみ PG ピンがローにプルダウンされます。PassThru 時は

PG がハイに維持されて、事前昇圧アプリケーションの静止電流を低減します。

|    |                    | このピンを使用すると、5つのモードを選択して性能                                                                                                                                                                                                                                                                                                               |                              |  |  |

|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|--|

|    |                    | SYNC / MODE Pin Input                                                                                                                                                                                                                                                                                                                  | Capable Mode(s) of Operation |  |  |

|    |                    | GND or < 0.1V                                                                                                                                                                                                                                                                                                                          | Burst                        |  |  |

|    |                    | External Clock                                                                                                                                                                                                                                                                                                                         | Pulse-skip/Sync              |  |  |

|    |                    | 100k Resistor to GND                                                                                                                                                                                                                                                                                                                   | Burst/SSFM                   |  |  |

| 16 | SYNC/MODE          | Float (pin open)                                                                                                                                                                                                                                                                                                                       | Pulse-skip                   |  |  |

|    |                    | INTV <sub>CC</sub>                                                                                                                                                                                                                                                                                                                     | Pulse-skip/SSFM              |  |  |

|    |                    | 選択可能な動作モードは以下の通りです。  Burst = 軽負荷時の低 I <sub>Q</sub> 、低出カリップル動作。 パルススキップ = 軽負荷時にパルスをスキップ(クロックに同期)。 同期 = スイッチング周波数を外部クロックに同期。 SSFM = 低 EMI を目的としたスペクトラム拡散周波数変調。                                                                                                                                                                           |                              |  |  |

| 17 | RT                 | タイミング抵抗ピン。LT8342のスイッチング周波数を内部設定するには、このピンと GND の間に抵抗を接続します。このピンはフロート状態にしないでください。SYNC ピンを使って IC を外部からクロッキングする場合、外部クロック周波数は、RT ピン抵抗で設定されるスイッチング周波数の 90%未満にすることはできません。                                                                                                                                                                     |                              |  |  |

| 18 | VC                 | エラー・アンプ補償ピン。電圧ループを安定させるには、VC ピンと GND の間に外部 RC 補償回路を配置します。                                                                                                                                                                                                                                                                              |                              |  |  |

| 19 | SS                 | ソフトスタート・ピン。出力ソフトスタート時間を設定するには、このピンと GND の間にソフトスタート・コンデンサ $C_{ m SS}$ を接続します。                                                                                                                                                                                                                                                           |                              |  |  |

| 20 | INTV <sub>CC</sub> | 内部 3.6V レギュレータのバイパス・ピン。このピンと GND の間には、容量が 2.2µF (またはそれ以上) の低 ESR セラミック・バイパス・コンデンサを接続します。接続位置はできるだけピンに近付けてください。このピンを直接駆動したり、他の外部回路からこのピンに負荷を加えたりしないでください。このピンは IC の内部スイッチ・ドライバに電力を供給します。スイッチングを開始するには INTVcc が 2.75V を超えていなければなりません。                                                                                                    |                              |  |  |

| 21 | PG                 | 出力パワー・グッド・インジケータ・ピン。PG ピンは内部コンパレータのオープン・ドレイン出力です。PG ピンは、V <sub>OUT</sub> が目標電圧±10%のウィンドウを外れると、LT8342によってローにプルダウンされます。V <sub>OUT</sub> が目標電圧±7%のウィンドウ内に入ると、外部プルアップ抵抗または電流源がPG ピンをハイにプルアップします。事前昇圧アプリケーションでは、PREBOOST ピンを INTV <sub>CC</sub> に接続すれば、PassThru 時に PG ピンがハイを維持して電流を消費しないようにすることができます。                                       |                              |  |  |

| 22 | EN/UVLO            | イネーブル/入力低電圧ロックアウト・ピン。EN/UVLO ピンが 1.02V の精密閾値未満に駆動された場合、LT8342 はシャットダウンされます。LT8342 は、EN/UVLO ピンが 1.08V を超えるとイネーブルされます。 $V_{IN} \  \   \text{COND} \   \text{の間の抵抗分圧器回路に EN/UVLO ピンを接続することにより、} \   V_{IN} \   の低電圧ロックアウト閾値を設定できます。この閾値を下回ると、IC はディスエーブル/シャットダウンされます。詳細はアプリケーション情報のセクションを参照してください。シャットダウン機能を使わない場合は、このピンを直接 VIN に接続します。$ |                              |  |  |

| 23 | V <sub>IN</sub>    | 入力電源ピン。このピンと GND の間には、容量が 2.2µF(またはそれ以上)の低 ESR セラミック・バイパス・コンデンサを接続します。接続位置はできるだけピンに近付けてください。V <sub>IN</sub> ピンは、入力遮断 FET 用検出コンパレータの正入力でもあります。                                                                                                                                                                                          |                              |  |  |

| 24 | SNS                | 入力遮断 FET 用検出コンパレータの負入力。このピンは、 $V_{IN}$ と入力遮断 FET のドレインの間に配置された外部電流センス抵抗にケルビン接続します。出力短絡フォルトなど、過電流状態時の $V_{IN}$ と SNS の最大電圧差は $45 \text{mV}$ に制限されます。入力遮断 FET を使用しない場合は、このピンを $V_{IN}$ に接続するかフロート状態にしてください。                                                                                                                              |                              |  |  |

analog.com.jp Rev 0 | 11 of 36

# 代表的な性能特性

図 4. Burst Mode 時の効率および電力損失と出力電流の関係。 図 1 を参照(SYNC/MODE = 0V)

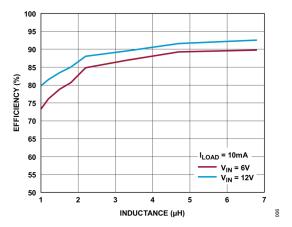

図 6. Burst Mode 時の効率とインダクタ値の関係。 図 1 を参照。V<sub>out</sub> = 24V

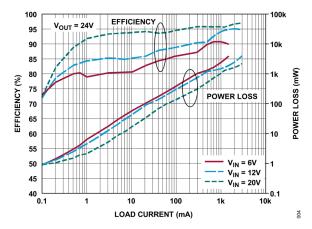

図 5. ルススキップ・モード時の効率および電力損失と出力電流の関係。図 1 を参照(SYNC/MODE オープン)

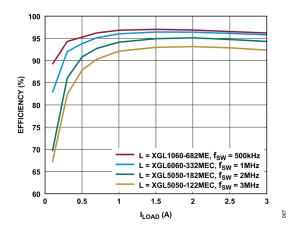

図 7. 様々なスイッチング周波数における効率と出力電流の 関係。図 1 を参照。V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 24V

analog.com.jp Rev 0 | 12 of 36

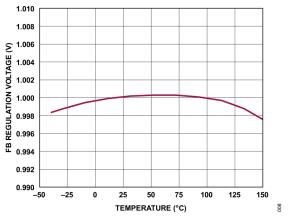

図 8. FB レギュレーション電圧と温度の関係

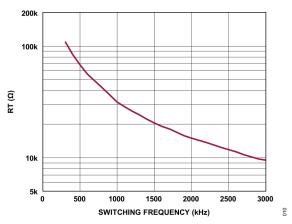

図 10. RT 値とスイッチング周波数の関係

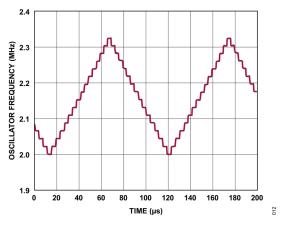

図 12. スペクトラム拡散変調時の発振周波数

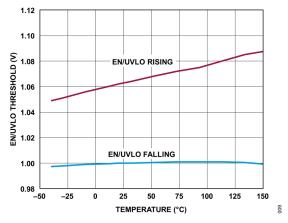

図 9. EN/UVLO 閾値と温度の関係

図 11. 発振周波数と温度の関係

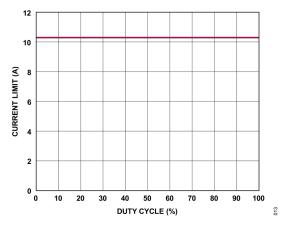

図 13. 下側スイッチの電流制限とデューティ・サイクルの関係

analog.com.jp Rev 0 | 13 of 36

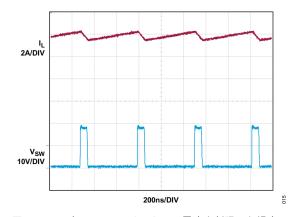

図 14. 下側スイッチの電流制限と温度の関係

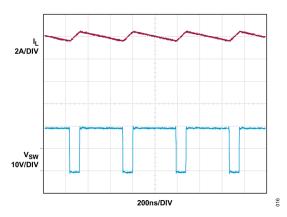

図 16. 18%デューティ・サイクルで電流を制限した場合の スイッチング波形。図 1 を参照 (V<sub>IN</sub> = 15V、V<sub>OUT</sub>への過負荷 = 19V)

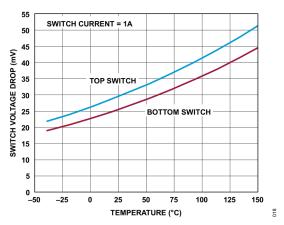

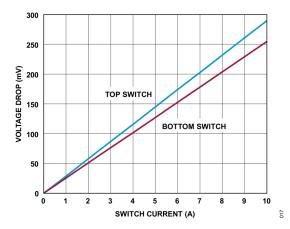

図 18. パワー・スイッチの電圧低下と温度の関係

図 15. 87%デューティ・サイクルで電流を制限した場合のスイッチング波形。図 1 を参照  $(V_{IN} = 3V, V_{OUT} \sim 0$  の過負荷 = 19V)

図 17. パワー・スイッチの電圧低下とスイッチ電流の関係

図 19. SS ピン電流と温度の関係

analog.com.jp Rev 0 | 14 of 36

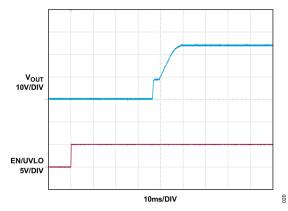

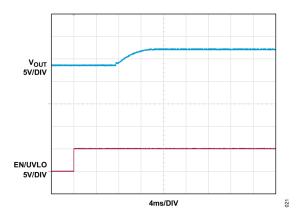

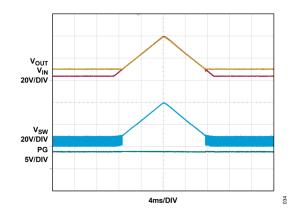

図 20. ソフトスタート、入力遮断時。 図 1 を参照(V<sub>IN</sub> = 9V、V<sub>OUT</sub> = 24V)

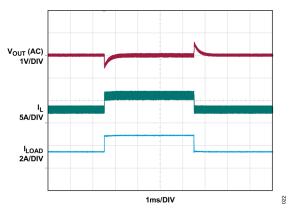

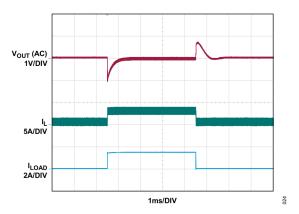

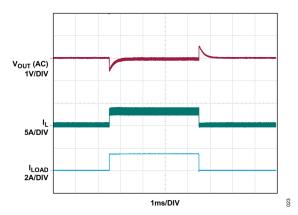

図 22. 負荷過渡応答:1.5A~3A。図 1 を参照。 V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 24V

図 24. 負荷過渡応答:50mA~1.5A。図 1 を参照 (Burst Mode)。V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 24V

図 21. ソフトスタート、入力遮断なし。 図 45 の回路を参照(V<sub>IN</sub> = 9V、V<sub>OUT</sub> = 12V)

図 23. 負荷過渡応答:50mA~1.5A。図 1 を参照 (パルススキップ・モード)。V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 24V

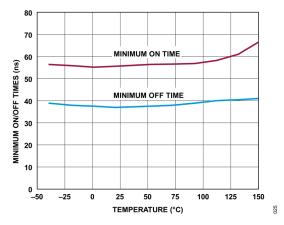

図 25. 下側スイッチの最小オン/オフ時間と温度の関係

analog.com.jp Rev 0 | 15 of 36

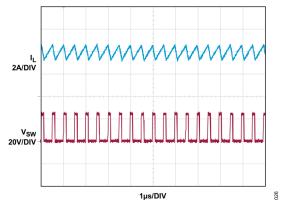

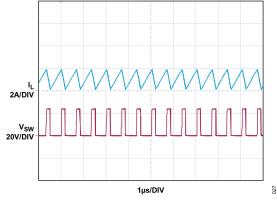

図 26. 最大周波数時の PWM 動作。図 1 を参照 (V<sub>IN</sub> = 6V、V<sub>OUT</sub> = 24V、I<sub>LOAD</sub> = 900mA)

図 28. 不連続 Burst Mode 動作。図 1 を参照 (SYNC/MODE = 0V、V<sub>IN</sub> = 6V、I<sub>LOAD</sub> = 50mA)

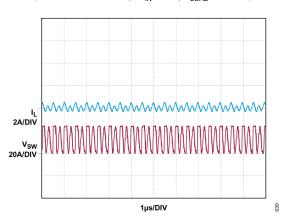

図 30. 不連続パルススキッピング・モード。図 1 を参照 (SYNC/SYNC オープン、 $V_{IN}$  = 12V、 $I_{LOAD}$  = 0A)

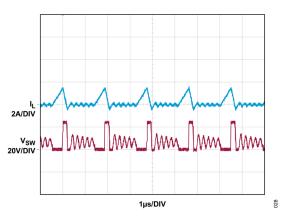

図 27. 連続 Burst Mode 動作。図 1 を参照 (SYNC/MODE = 0V、V<sub>IN</sub> = 6V、I<sub>LOAD</sub> = 230mA)

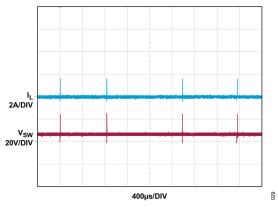

図 29. 軽負荷時の低 I<sub>Q</sub> Burst Mode 動作。図 1 を参照 (SYNC/MODE = 0V、V<sub>IN</sub> = 6V、I<sub>LOAD</sub> = 0A)

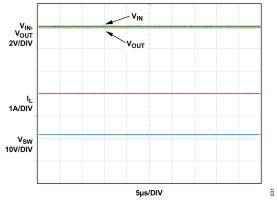

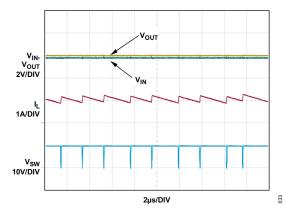

図 31. PassThru モード動作。図 49 の回路を参照 (V<sub>IN</sub> = 12V、I<sub>LOAD</sub> = 1A)

analog.com.jp Rev 0 | 16 of 36

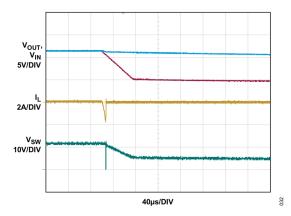

図 32. PassThru モードでの逆電流保護。図 49 の回路を参照 (V<sub>IN</sub>が 11V から 5V まで低下、無負荷時)

図 34. 事前昇圧ラインのトランジェント。図 49 の回路を参照。 3V~40Vの V<sub>IN</sub>トランジェント(1.8A 負荷)

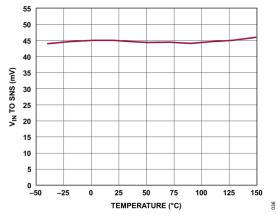

図 36. V<sub>IN</sub>~SNS 間の閾値と温度の関係

図 33. V<sub>IN</sub> が V<sub>OUT</sub> に近い場合の周波数フォールドバック。 図 49 の回路を参照(V<sub>IN</sub> = 9.8V、V<sub>OUT</sub> = 10V、I<sub>LOAD</sub> = 1A)

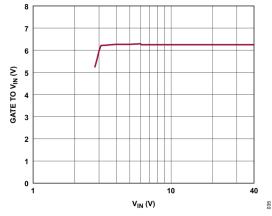

図 35. GATE $\sim$ V<sub>IN</sub>間のレギュレーション電圧と V<sub>IN</sub>の関係

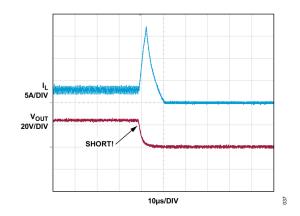

図 37. 出力短絡保護。図 1 を参照(V<sub>IN</sub> = 9V)

analog.com.jp Rev 0 | 17 of 36

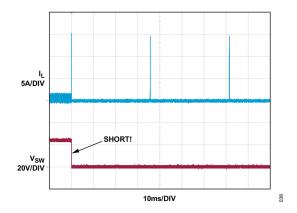

図 38. 出力短絡時のヒカップ。図 1 を参照(V<sub>IN</sub> = 9V)

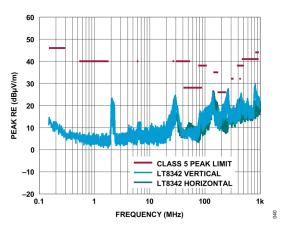

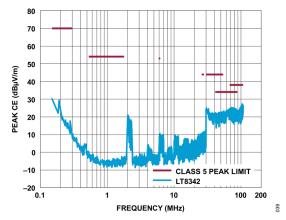

図 40. 放射 EMI 性能(CISPR 25 クラス 5 のピーク値) 図 45 の回路を参照。V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 24V、I<sub>LOAD</sub> = 3A SSFM オン。f<sub>SW</sub> = 2MHz~2.3MHz

図 39. 伝導 EMI 性能(CISPR 25 クラス 5 のピーク値) 図 45 の回路を参照。V<sub>IN</sub> = 12V、V<sub>OUT</sub> = 24V、I<sub>LOAD</sub> = 3A SSFM オン。f<sub>SW</sub> = 2MHz~2.3MHz

analog.com.jp Rev 0 | 18 of 36

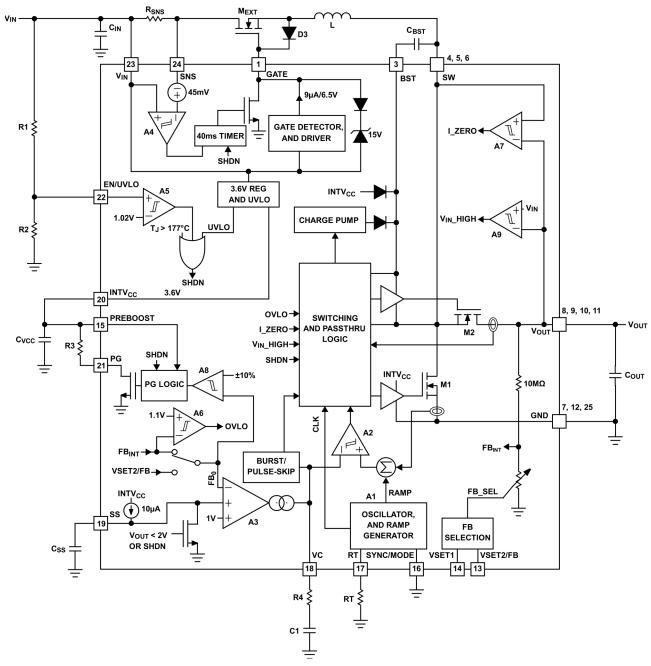

# ブロック図

図 41. ブロック図

041

analog.com.jp Rev 0 | 19 of 36

### 動作原理

LT8342 はモノリシック同期整流式昇圧 DC/DC コンバータであり、固定周波数のピーク電流モード制御を使用して、優れたライン・レギュレーションと負荷レギュレーションを実現します。このデバイスは EMI を大幅に減らす Silent Switcher アーキテクチャを採用しており、出力短絡保護と突入電流抑制のためにオプションの入力遮断 N チャンネル FET  $(M_{\rm EXT})$  を制御するように設定できます。

以下に示す LT8342 の動作説明については、ブロック図を参照してください。コンバータ入力と EN/UVLO ピンの間にあるオプションの抵抗分圧器は、立上がり閾値が 1.08V、立下がり閾値が正確に 1.02V であり、これを用いてコンバータ入力のターンオン/オフのレベルをプログラムすることができます。もしくは、EN/UVLO ピンをコンバータ入力に接続したり、外部のロジック・レベル信号から駆動したりすることも可能です。EN/UVLO ピンの電圧が 0.15V を下回るとすべての内部回路がシャットダウンされ、 $V_{\rm IN}$  ピンに流れる電流は  $1\mu$ A 未満になります。

EN/UVLO ピン電圧が十分に高い値になって  $V_{IN}$  ピン電圧が 2.8V 以上になると、内部回路がアクティブになります。LT8342 は、内部帰還 (FB<sub>INT</sub>) と外部帰還 (VSET2/FB ピン) のどちらが帰還ノード (FB<sub>0</sub>) として使われているかをチェックします。内部帰還が使われている場合は、それに応じて FB\_SEL が自動的に正しい内部帰還比を決定します。SS ピンからの  $10\mu$ A の電流によって外部ソフトスタート・コンデンサ (Css) が徐々に充電され、それによってレギュレーションのリファレンス電圧がゆっくりとランプ・アップします。発振器 (A1) は各クロック・サイクルの開始時に内部下側パワー・スイッチ (M1) をオンにしますが、この発振器の周波数は RT ピンとグラウンドの間の抵抗を使って設定します。

インダクタを流れる電流は下側スイッチの電流コンパレータ(A2)がトリップするまで増加を続け、トリップすると下側パワー・スイッチがオフになります。下側スイッチがオフになるピーク・インダクタ電流の値は、VC ピンの電圧によって制御されます。エラー・アンプ (A3) は、帰還ノード (FBo) の電圧と内部 1V リファレンスを比較することによって VC ピンをサーボ制御します。エラー・アンプは VC ピン電圧を駆動して、出力電圧のレギュレーションを維持するために適切なピーク・スイッチ電流レベルを設定します。負荷電流が増加すると、内部 1V リファレンスに対する帰還ノード (FBo) の相対的な電圧が低下します。これによりエラー・アンプが VC ピン電圧を上昇させ、出力電圧のレギュレーションを維持できるだけの十分な電力が出力に供給されるようになるまで、ピーク・インダクタ電流を増大させます。下側パワー・スイッチ (M1) がオフになると、次のクロック・サイクルが始まるまで、あるいはインダクタ電流がゼロに低下するまで、同期パワー・スイッチ (M2) がオンになります。

出力電圧を維持するための事前昇圧レギュレータが必要なアプリケーションでは(例えば自動車のコールド・クランク時やスタート/ストップ時)、いつ  $V_{\rm IN}$ が  $V_{\rm OUT}$ を超えるかを知るために、 $V_{\rm IN}$  ピンと  $V_{\rm OUT}$  ピンが常時モニタされます。 $V_{\rm IN}$ が  $V_{\rm OUT}$ を超え、なおかつ  $V_{\rm OUT}$ が その設定レギュレーション電圧より高い場合、LT8342 は Pass Thru モードになって上側同期スイッチをオンし、最大限の効率が得られるようにします。

オプションの入力短絡保護および突入電流抑制機能は、外部センス抵抗  $(R_{SNS})$  と N チャンネル FET  $(M_{EXT})$  を、コンバータ入力と直列に追加することによって実現できます。 $M_{EXT}$  を使わない場合、GATE ピンは GND に接続してください。LT8342 は、 $M_{EXT}$  が設定されているかどうかを自動的に検出できます。

スタートアップ時は、内蔵の  $9\mu$ A 電流源によって GATE ピン( $M_{EXT}$ のゲートに接続)の電圧が  $V_{IN}$ より 6.5V 高い値まで上昇します。出力短絡発生時に、センス抵抗  $R_{SNS}$  を流れるコンバータ入力電流がコンパレータ A4 の 45mV 閾値を超える程度まで増加した場合、LT8342 は GATE ピンを GND にプルダウンして  $M_{EXT}$  をオフにし、最大短絡インダクタ電流を制限します。 $M_{EXT}$  がオフになった後、LT8342 は 40ms 待機してから GATE ピンの電圧を上げ、再び  $M_{EXT}$  をオンにします。

LT8342 の SYNC/MODE ピンは外部クロックへの同期に使用できます。また、アプリケーションの要求に基づいてコンバータ性能を最適化するために、Burst Mode 動作とパルススキッピング・モード動作の選択に使用することもできます。SSFM は、これら 2 つのモードのどちらかでアクティブにして EMI を更に減らすことができます。

LT8342 の保護機能には、出力の過電圧保護と短絡保護、サーマル・シャットダウン、および低電圧ロックアウトが含まれています。この IC は、スイッチング周波数を調整してインダクタの電圧と時間のバランスを保つことによって、コンバータのデューティ・サイクルを極めて低い値にすることが求められる条件下での電流の暴走も防ぎます。

analog.com.jp Rev 0 | 20 of 36

# アプリケーション情報

# EN/UVLO ピンによる V<sub>IN</sub> オン/オフ閾値のプログラミング

システムの  $V_{IN}$  のターンオン/オフ閾値は、 $V_{IN}$  と GND の間に接続した抵抗分圧器で EN/UVLO ピンを駆動することによってプログラムできます(ブロック図を参照)。閾値電圧は式(1)と(2)によって決まります。

$$V_{(FALLING,TURN\ OFF)} = 1.02V \times \frac{R_1 + R_2}{R_2} \tag{1}$$

$$V_{(RISING,TURN\,ON)} = 1.082V \times \frac{R_1 + R_2}{R_2} \tag{2}$$

軽負荷電流での Burst Mode 動作時は、抵抗  $R_1$  と  $R_2$  に流れる電流が LT8342 の消費する電源電流を簡単に超えてしまう可能性があります。 したがって、 $R_1$  と  $R_2$  は、低負荷時の効率に与える影響をできるだけ小さくするために、十分大きな値とする必要があります。

シャットダウン機能を使わない場合は、EN/UVLO ピンを  $V_{\rm IN}$ に接続できます。また、シャットダウン制御が必要な場合は、このピンをロジック・レベルに接続することもできます。EN/UVLO ピンが 0.15V 未満になると、IC に流れる  $V_{\rm IN}$  静止電流が  $0.35\mu A$  (代表値)に減少します。

## INTVcc レギュレータ

内蔵の低ドロップアウト(LDO)レギュレータは VIN から 3.6V の電源を生成し、ゲート・ドライバと内部バイアス回路に電力を供給します。INTVCC ピンは、2.2µF 以上のセラミック・コンデンサを使って GND にバイパスする必要があります。パワーMOSFET のゲート・ドライバに必要な大過渡電流を供給するには、良好なバイパスが必要です。入力電圧もスイッチング周波数も高いアプリケーションでは、LDO で消費される電力が大きいのでダイ温度が上昇します。INTVCC ピンには外部負荷を接続しないでください。

### 出力電圧のプログラミング

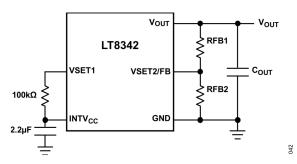

LT8342 は、安定化出力電圧レベルをプログラムする、調整可能な内部帰還分圧器を備えています。プリセット・レベルを選択するには、表 6 に従って VSET1 ピンと VSET2/FB ピンを設定します。 $10 M\Omega$ (代表値)を超える抵抗分圧器は、従来型の外部分圧器よりも  $V_{OUT}$  ピンからの静止電流を大幅に減らすことができます。

それでも外部帰還を必要とするいくつかのアプリケーションでは、 $100k\Omega$  の抵抗を介して VSET1 ピンを INTVCC に接続すれば、 VSET2/FB ピンを従来型の帰還ピンとしてプログラムすることができます。この場合、出力電圧は図 1 に示すように出力と VSET2/FB ピンの間にある抵抗分圧器でプログラムされます。抵抗値は式(3)に従って選択します。

$$R_{FB1} = R_{FB2} \times \left(\frac{V_{OUT}}{1V} - 1\right) \tag{3}$$

式 (3) の中の抵抗値は、図 42 に示す参照記号を表しています。出力電圧の精度を維持するには、1%抵抗を使用することを推奨します。 大きい帰還抵抗を使用する場合は、 $V_{OUT}$  と VSET2/FB の間に  $4.7pF\sim22pF$  の進相コンデンサが必要になることがあります。外部帰還の使用時に VSET2/FB がグラウンドに短絡するフォルトによって、表 6 に示すような十分に高い出力電圧が得られなかった場合、LT8342 は自動的に内部帰還に切り替えて、出力を 19V に安定化します。

analog.com.jp Rev 0 | 21 of 36

図 42. LT8342 を外部帰還構成にした場合の簡略図

# 軽負荷電流時の動作 - Burst Mode またはパルススキッピング・モード

LT8342 は、軽負荷時には自動的に Burst Mode に入って効率を維持するようにプログラムできます(SYNC/MODE ピンを使用)。この状態では、LT8342 はインダクタのピーク電流を 1.6A(代表値)以上に維持し、負荷の減少に合わせてスイッチング周波数を下げます。これにより、入力静止電流と出力電圧リップルを最小限に抑えながら、出力電圧を安定化します。軽負荷時の Burst Mode 動作では、LT8342 は単一の小電流パルスを出力コンデンサに送り、その後はスリープ期間とします。スリープ期間内の出力電力は出力コンデンサから供給されます。スリープ・モードの間に LT8342 が消費する電流は、外部入力遮断 N チャンネル FET(Mext、図 41 を参照)使用時でわずか  $28\mu A$ 、 $M_{EXT}$  不使用時は  $9\mu A$  に過ぎません。出力負荷が低下するにつれて単一電流パルスの繰り返し頻度は減少し、LT8342 がスリープ・モードになっている時間のパーセンテージは増加します。この結果、軽負荷時の効率は標準的なコンバータよりはるかに高くなります。

軽負荷時の効率を向上させるには、各パルス間でLT8342がより長くスリープ・モードに留まることができるように、Burst Mode 動作時におけるそれぞれの単一小パルスの間に、より多くのエネルギーを出力に供給する必要があります。これは、より大きい値のインダクタを使用することによって実現できます。例えば、スイッチング周波数の高いアプリケーションでは、普通、より低い値のインダクタを使用しますが、軽負荷時の効率を上げたい場合は高い値のインダクタを選ぶ必要があります。出力容量を大きくすると、それに比例して出力リップルが小さくなります。出力負荷がゼロからランプ・アップするとスイッチング周波数も増加し、RTピンの抵抗によって決まる固定周波数になるまで増加を続けます。LT8342が固定周波数に達する出力負荷は、入力電圧、出力電圧、およびインダクタの選択によって変わります。

パルススキッピング・モードには、Burst Mode と大きく異なる点が 2 つあります。1 つ目は、内部クロックが常時動作していて、すべてのスイッチング・サイクルがこのクロックにアラインされる点です。このモードでは内部回路が常時動作しているので  $V_{IN}$  ピンの静止電流が 1.9mA まで増加しますが、Burst Mode では 9 $\mu$ A に過ぎません。もう 1 つは、負荷がゼロからランプ・アップする際、RT ピンの抵抗によってプログラムされるスイッチング周波数に達するときの出力負荷が Burst Mode の場合より小さいことです。したがって、パルススキッピング・モードでは、より広い負荷範囲にわたって出力リップルが小さくなります。

#### スイッチング周波数のプログラミングと同期

動作周波数の選択は、効率と部品サイズのトレードオフです。低周波数動作は、パワー・スイッチのスイッチング損失とゲート・ドライバ電流を減らすことによって効率を向上させます。しかし、低周波数動作には物理的サイズの大きいインダクタが必要です。LT8342 は固定周波数アーキテクチャを使用しており、それにより、図 41 のブロック図に示すように RT ピンとグラウンドの間に外部抵抗を 1 つ取り付けることによって、周波数を 300kHz~3MHz の範囲にプログラムできます。所定のスイッチング周波数に対応する  $R_T$  の値を表 7 に示します。

LT8342 の動作周波数は、最小パルス幅 100ns の外部クロック・ソースに同期させることができます。SYNC/MODE ピンにデジタル・クロック信号を入力することによって、LT8342 は SYNC パルス周波数で動作し、軽負荷時には自動的にパルススキッピング・モード動作に入ります。この機能を使用するときは、できるだけ SYNC パルス周波数に近いスイッチング周波数をプログラムできる RT 抵抗を選ぶ必要があります。

analog.com.jp Rev 0 | 22 of 36

表 7. スイッチング周波数 (f<sub>sw</sub>) と R<sub>T</sub>値の関係

| f <sub>sw</sub> (MHz) | R <sub>T</sub> (kΩ) | f <sub>sw</sub> (MHz) | R <sub>τ</sub> (kΩ) |

|-----------------------|---------------------|-----------------------|---------------------|

| 0.3                   | 110                 | 1.7                   | 18.2                |

| 0.4                   | 84.5                | 1.8                   | 16.9                |

| 0.5                   | 68.1                | 1.9                   | 15.8                |

| 0.6                   | 56.2                | 2.0                   | 15                  |

| 0.7                   | 48.7                | 2.1                   | 14.3                |

| 0.8                   | 42.2                | 2.2                   | 13.7                |

| 0.9                   | 36.5                | 2.3                   | 13                  |

| 1.0                   | 31.6                | 2.4                   | 12.4                |

| 1.1                   | 28.7                | 2.5                   | 11.8                |

| 1.2                   | 26.1                | 2.6                   | 11.3                |

| 1.3                   | 24.3                | 2.7                   | 10.7                |

| 1.4                   | 22.1                | 2.8                   | 10.2                |

| 1.5                   | 20.5                | 2.9                   | 9.76                |

| 1.6                   | 19.1                | 3.0                   | 9.53                |

## スペクトラム拡散周波数変調

LT8342 は SSFM 方式を採用しており、電磁妨害波を更に減らすことができます。100k $\Omega$  の抵抗を介して SYNC/MODE ピンをグラウンド に接続すれば、Burst Mode 動作で SSFM を選択できます。また、SYNC/MODE ピンを INTV $_{\rm CC}$  に接続すれば、パルススキッピング動作で SSFM を選択できます。SSFM 選択時は、ステップ三角波周波数変調を使用して、 $R_{\rm T}$  抵抗によってプログラムされた値から、その値より 約 13%高い値までの範囲で、内部発振器周波数を変化させます。変調周波数はスイッチング周波数の約 0.45%です。例えば、LT8342 を 2MHz にプログラムしてスペクトラム拡散周波数変調を選択した場合、発振器周波数は 9kHz きざみで 2MHz から 2.3MHz まで変化します (代表的な性能特性のセクションの図 12 - スペクトラム拡散変調時の発振周波数を参照)。

#### V<sub>IN</sub>-V<sub>OUT</sub> PassThru モード動作

自動車用事前昇圧アプリケーションにおける昇圧コンバータの入力電圧は、通常、帰還抵抗回路でプログラムされる安定化出力電圧より高い値に設定されます。この条件下でのLT8342 は PassThru モード動作となり、同期パワー・スイッチ M2(ブロック図を参照)は常時オンに、パワー・スイッチ M1 は常時オフに保たれます。昇圧コンデンサ( $C_{BST}$ )の電圧は常時モニタされます。この電圧が 2.9V を下回ると内部チャージ・ポンプ回路がオンになり、昇圧コンデンサの電圧を 3.2V まで上げてからオフにすることで、M2 のゲート駆動電圧を十分な値に維持します。

PassThru モードでは、SYNC/MODE ピンの設定に関わらず、LT8342 は自動的に低静止電流状態になります。入力静止電流は入力遮断 FET  $(M_{EXT})$  使用時でわずか  $26.5\mu$ A、 $M_{EXT}$  不使用時は  $12\mu$ A に過ぎません。入力電圧が目標出力電圧の 110%を超えた場合は、PG ピンがローになって、 $V_{OUT}$  がレギュレーション範囲を外れたことを示します。PG が外部的にプルアップされた場合は、プルアップ抵抗を流れる電流が LT8342 の静止電流より大きくなる可能性があります。PREBOOST ピンを INTV $_{CC}$  に接続すると、PassThru 時の消費電力を更に減らすことができます。この場合は、PassThru 動作時に出力電圧がレギュレーション範囲を超えても、PG がローになることはありません。

analog.com.jp Rev 0 | 23 of 36

昇圧コンバータの出力コンデンサに保存された電圧未満のレベルまで入力電圧が急激に低下した場合は(ストップ/スタート時やコールド・クランク時)、逆方向インダクタ電流が-1.8A(代表値)を超えると M2 がオフになります。出力コンデンサは、負荷電流によって自然に放電します。LT8342の Pass Thru モードは、 $V_{\rm IN}$ のレベルに関わらず、プログラムされたレギュレーション・レベルより  $V_{\rm OUT}$ の方が高い限り維持されます。

LT8342 が PassThru モードを終了できるのは、プログラムされたレギュレーション・レベル未満に  $V_{OUT}$  が低下した場合に限られます。この場合は、M1 がオンになって M2 がオフになります。LT8342 はその後直ちに昇圧コンバータとして応答し、プログラムされたレベルに VOUT を維持します。

PassThru モードを正しく機能させるには、LT8342の V<sub>IN</sub>ピンを昇圧コンバータの入力に接続する必要があります。

### V<sub>IN</sub>が V<sub>OUT</sub>に近付いた場合のスイッチング周波数フォールドバック

昇圧アプリケーションによっては、入力電圧が Vour に非常に近い電圧まで増加することがあります。この状態では、出力電圧のレギュレーションを維持するために、非常に低いデューティ・サイクルでスイッチング・レギュレータを作動させる必要があります。しかし、パワー・スイッチの最小オン時間の制限により、プログラムされたスイッチング周波数では、スイッチャを十分低いデューティ・サイクルにできない可能性があります。結果として、標準的な昇圧コンバータの場合、このような条件下では大きな出力リップルが生じることになります。

LT8342 はスイッチング周波数フォールドバック機能を採用し、スイッチャのデューティ・サイクル減少が最小オン時間によって制限され始めた場合は、スイッチング周波数を下げることによってこの問題に対処します。

# 出力短絡保護

オプションの入力短絡保護は、外部センス抵抗( $R_{SNS}$ )と N チャンネル FET( $M_{EXT}$ )をコンバータ入力と直列に追加することによって実現できます。 $M_{EXT}$ (ブロック図を参照)のソースとゲートの間に低リーク電流の p-n クランプ・ダイオード(D3)を置く必要もあります。

スタートアップ時は、内蔵の  $9\mu$ A 電流源によって GATE ピン( $M_{EXT}$ のゲートに接続)の電圧が  $V_{IN}$ より 6.5V 高い値まで上昇します。出力短絡発生時に、センス抵抗  $R_{SNS}$  を流れるコンバータ入力電流がコンパレータ A4 の 45mV 関値を超える程度まで増加した場合、LT8342 は GATE ピンを GND にプルダウンして直ちに最大短絡インダクタ電流を制限し、最終的に  $M_{EXT}$ をオフにします。インダクタ電流がゼロ未満に低下すると、SW ノードの寄生容量がリンギングを発生させて大きな負のゲート・ソース間電圧( $V_{GS}$ )が生じ、そのために  $M_{EXT}$  が損傷する可能性があります。ダイオード D3 は、 $M_{EXT}$ の負の  $V_{GS}$ をクランピングすることによって  $M_{EXT}$ を保護します。 $M_{EXT}$ がオフになった後、LT8342 は 40ms 待機してから GATE ピンの電圧を上げ、再び  $M_{EXT}$ をオンにします。代表的な性能特性のセクションの図 37 と図 38 に、出力短絡時の代表的な波形を示します。

Mextを選択するときは、以下の要素を考慮する必要があります。

- ▶ ドレイン・ソース間電圧と電流定格は、意図するアプリケーションに十分な値とする必要があります。通常は、V<sub>DS\_MAX</sub> を 40V、 I<sub>DS\_MAX</sub> を過電流制限値(45mV/R<sub>SNS</sub>)より高い値とするのが安全です。

- ▶ ゲート・ソース間電圧の定格は 15V 以上とする必要があります。内部チャージ・ポンプは GATE ピンを V<sub>IN</sub>より 6.5V 高い値に駆動するよう動作するので、V<sub>GS\_MAX</sub>は+15V 以上とする必要があります。ソースとゲートの間にはクランプ・ダイオードがあるので、負の最大定格はこの値以下とすることができます。

- ▶ ゲート閾値電圧 (V<sub>GS\_TH</sub>) は 1.8V 未満とすることを推奨します。

- ▶ ゲート・ドレイン間電荷( $Q_{CD}$ )は、突入電流を減少させるのに十分な大きさとする必要があります。 $M_{EXT}$ のスタートアップ時に、 $V_{GS}$ が  $V_{GS\_TH}$ を超えると、 $9\mu$ Aの充電電流はすべてゲート・ドレイン間容量( $C_{RSS}$ )に流れ込みますが、 $V_{GS}$ はほぼ同じ値に止まります。ソース電圧  $V_{S}$ (インダクタの入力としても機能)は、すぐにドレイン電圧  $V_{IN}$ までランプ・アップします。 $V_{OUT}$ の初期値はグラウンドなので、突入電流が発生します。突入電流は、 $R_{SNS}$ によってプログラムされる出力短絡電流未満に抑えなければなりません。 $C_{OUT}$ や  $V_{IN}$ が大きくなった場合は、普通、それに合わせて  $Q_{GD}$ を大きくする必要があります。

- ▶ 低オン抵抗 (RDSON) とすることで最大限の効率を実現します。ほとんどのアプリケーションでは、MEXTの IDS\_MAXが短絡電流制限値より十分大きな値である限り、安全動作領域 (SOA) に関わる問題が生じるようなことはありません。これは、LT8342が MEXTの電流のレギュレーションを行わず、制限値に達した場合は MEXTをオフにするだけだからです。加えて、GATE ピンのプルダウン強度が高いので過大な電流が生じても持続時間が非常に短く、結果として MEXTに加わるストレスの大きさが制限されます。再試行前の40msのタイムアウト時間により、熱は十分に放出されます。

analog.com.jp Rev 0 | 24 of 36

### スタートアップ

スタートアップ時のピーク・スイッチ電流と  $V_{OUT}$ のオーバーシュートを制限するために、LT8342 は SS ピンを使ってソフトスタート動作を行います(ブロック図のエラー・アンプ A3 を参照)。ソフトスタート時は、 $10\mu A$ (代表値)の電流源が外部ソフトスタート・コンデンサ  $C_{SS}$ を徐々に充電します。SS ピンの電圧が FB 初期電圧から 1V までの範囲に低下すると、IC は、FB ピン電圧を 1V ではなく SS ピン電圧に安定化します。このように、スタートアップ時のピーク・スイッチ電流を制限しながら、出力コンデンサが徐々に最終値まで充電されます。

IC は、スタートアップ時にはスペクトラム拡散周波数変調なしのパルススキッピング・モードを選択し、SYNC/MODE ピン設定は無視されます。IC は、SS ピン電圧が 1.2V(代表値)を超えた後に SYNC/MODE ピン設定を読み出します。

外部遮断 FET  $(M_{\rm EXT})$  を使用する場合、パワーアップ時と EN/UVLO がハイのときは、ヒカップ・タイマーが 40ms (代表値) をカウントしてから、 $M_{\rm EXT}$  がオンされて SS ピンが動作を開始します。何らかのフォルトが発生して低電圧リセット・ループ中にシステムがスタックしてしまった場合は、IC が繰り返しリセットされるようなときでも、 $M_{\rm EXT}$  が過熱しないように、このメカニズムが再試行と再試行の間に十分なヒカップ時間を確保します。 $M_{\rm EXT}$  を使用しない (GATE をグラウンドに接続)場合、イネーブルとスタートアップの間にヒカップ遅延は挿入されません。異なる設定下でのスタートアップ動作の比較については、代表的な性能特性のセクションの図 20 と図 21 を参照してください。

# ループ補償

ループ補償は安定性と過渡応答性能を決定します。LT8342 はピーク電流モード制御を使用して出力を安定化するので、ループ補償が容易になります。

LT8342 の帰還ループを補償するには、通常は VC ピンと GND の間に抵抗コンデンサ回路を直列に接続します。代表的な VC 補償回路をブロック図に示します。ほとんどのアプリケーションでは、コンデンサを  $100pF\sim10nF$  の範囲とし、抵抗を  $5k\Omega\sim200k\Omega$  の範囲とします。多くの場合は、RC 補償回路と並列に小さいコンデンサを接続して、帰還抵抗回路から内部エラー・アンプまでの間を流れる出力電圧リップルによって生じる VC 電圧リップルを減衰させます。この並列コンデンサの値は通常  $2.2pF\sim22pF$  の範囲です。実用的な補償回路設計方法は、このデータシートの回路の中から目的のアプリケーションに近い回路を 1 つ選ぶことから始め、補償回路を調整して性能を最適化することです。その後に、負荷電流、入力電圧、温度などの全動作条件について安定性を確認します。詳細はアプリケーション・ノート 76 を参照してください。

### 熱に関する考慮事項

LT8342 の良好な温度管理を実現するには、PCB のレイアウトに注意を払う必要があります。電源グランド・プレーンは、サーマル・ビアを配置した広い銅層で構成する必要があります。これらの層は、LT8342 から発生する熱を放出します。ビアを追加すれば、熱抵抗を更に小さくすることができます。最大負荷電流は、周囲温度が最大ジャンクション温度定格値に近付くに従ってディレーティングする必要があります。LT8342 内の消費電力 ( $P_{DISS}$ ) は、効率測定時に計算された全電力損失から、インダクタとセンス抵抗の電力損失と NMOS (使用している場合) の電力損失を差し引くことによって推定できます。更に、式 (4) から LT8342 のジャンクション温度を予測することができます。

$$T_{IUNCTION} = T_{AMBIENT} + \theta_{IA} \times P_{DISS} \tag{4}$$

analog.com.jp Rev 0 | 25 of 36

### 過熱ロックアウト

LT8342 はダイの温度が 177℃ (代表値) に達すると、スイッチング動作を停止して過熱ロックアウト状態になります。ダイ温度が 170℃ (代表値) 未満に低下すると、デバイスはインダクタのピーク電流をソフトスタートして、スイッチング動作を再開します。

# インダクタの選択

連続導通モード (CCM) での動作時は、出力電圧 ( $V_{OUT}$ ) と入力電圧 ( $V_{IN}$ ) に基づいてデューティ・サイクルを計算できます。最大 デューティ・サイクル ( $D_{MAX}$ ) は、コンバータの入力電圧が式 (5) で与えられる最小値のときに得られます。

$$D_{MAX} = \frac{V_{OUT} - V_{IN,MIN}}{V_{OUT}} \tag{5}$$

不連続導通モード(DCM)では特定の周波数で変換率が向上しますが、効率は低下してスイッチング電流値も大きくなります。

インダクタのリップル電流 $\Delta I_L$  は、インダクタ値の選択、コンバータの最大出力電流能力、および Burst Mode 動作における軽負荷時の効率に直接影響します。 $\Delta I_L$  の値を小さくすれば出力電流能力と Burst Mode 動作における軽負荷時効率は向上しますが、より大きいインダクタンス値が必要となり、電流ループのゲインも低下します。 $\Delta I_L$  値を大きくすると、高速の過渡応答が得られてインダクタンス値も小さくできますが、入力電流リップルやコア損失の増加、Burst Mode 動作における軽負荷時効率の低下、出力電流能力の低下といった欠点が生じます。高デューティ・サイクル動作時に $\Delta I_L$  の値を大きくすると、低調波振動を起こす可能性があります。

動作入力電圧範囲が決まって、動作周波数とインダクタのリップル電流を選択したら、式(6)によって昇圧コンバータのインダクタ値を決定できます。

$$L = \frac{V_{IN,MIN}}{\Delta I_L \times f_{SW}} \times D_{MAX} \tag{6}$$

LT8342 は、スイッチとシステムを過負荷フォルトから保護するために、ピーク・スイッチング電流を制限します。下側スイッチの電流は、デューティ・サイクルに関わらず 10.3A(代表値)に制限されます。インダクタのピーク電流値は LT8342 の下側スイッチ電流制限値と同じです。インダクタは、インダクタのピーク電流に対処するために、十分な飽和定格と RMS 電流定格のものを選ぶ必要があります。

# 入力コンデンサの選択

昇圧コンバータの入力電流は連続的なものなので、入力リップル電流は(出力リップル電流に比べて)比較的低い値に止まります。入力コンデンサ  $C_{\rm IN}$  の定格電圧は、最大入力電圧より十分大きくする必要があります。入力コンデンサに過度のストレスを与え得るあらゆる過電圧トランジェントの可能性について、入力電圧の特性を評価するようにしてください。

$C_N$ の値はソース・インピーダンスの関数であり、一般にソース・インピーダンスが高いほど必要な入力容量も大きくなります。

analog.com.jp Rev 0 | 26 of 36

RMS C<sub>IN</sub> リップル電流は式(7)によって予測できます。

$$I_{RMS,CIN} = 0.3 \times \Delta I_L \tag{7}$$

### 出力コンデンサの選択

出力コンデンサには 2 つの重要な役割があります。1 つ目は、LT8342 の不連続上側スイッチ電流のフィルタリングを行って、DC 出力を生成することです。この動作によって出力リップルが決まるので、スイッチング周波数におけるインピーダンスを小さくすることが重要です。2 つ目は、トランジェント負荷に対応するためにエネルギーを保存し、LT8342 の制御ループを安定させることです。X5R や X7R タイプのセラミック・コンデンサは等価直列抵抗(ESR)が非常に小さいため、出力電圧リップルを小さくし、また、良好な過渡応答を実現します。過渡応答性能は、入力容量を大きくすると共に、VOUT と VSET2/FB の間にフィードフォワード・コンデンサを追加する(外部帰還を使用している場合)ことによって改善できます。フィードフォワード・コンデンサを使用したり出力容量を調整したりする場合は、十分な設計マージンを確保するために、システムの安定性を慎重に評価する必要があります。また、出力容量を大きくすると、出力電圧リップルが小さくなります。スペースとコストを節約するために出力容量を小さくすることもできますが、過渡応答性能が低下してループも不安定になります。

Silent Switcher 相殺ループを完成させるには、大容量の出力コンデンサに加えて、IC のできるだけ近くに 2 個の小さい出力セラミック・コンデンサ(共に  $0.1\mu$ F)を配置する必要があります。

詳細については基板レイアウトのセクションを参照してください。より低いスイッチング周波数を使用する場合は、それだけ大きい出力容量が必要となります。また、ワイヤやケーブルが長くて負荷に対するインダクタンスがかなり大きくなる場合は、更に大きい容量が必要になりますが、これは電界コンデンサを使用することによって実現できます。コンデンサを選ぶときは、そのコンデンサのデータシートを十分に吟味し、関係する電圧バイアスと温度での動作条件に基づいて実効容量を計算する必要があります。物理的に大きいコンデンサ、あるいはより高い電圧定格のコンデンサが必要となることもあります。妥当な開始値については、標準的応用例のセクションを参照してください。

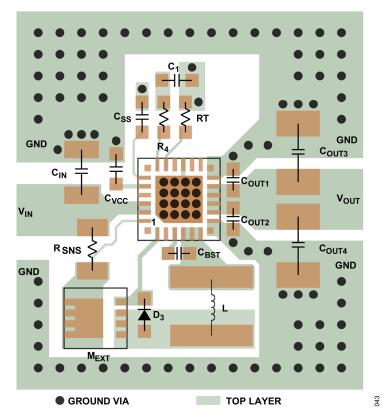

### 推奨 PCB レイアウトのガイドライン

LT8342 は電磁妨害波を最小限に抑えて、高周波数でのスイッチング時に最大限の効率が得られるよう特別に設計されています。図 43 に 推奨 PCB レイアウトを示します。PCB レイアウトに関する詳細と PCB 設計ファイルについては、LT8342 のデモ・ボード・ガイドを参照 してください。

LT8342 の性能を最大限に引き出すには、複数の出力バイパス・コンデンサを使用する必要があります。また、Silent Switcher EMI 相殺ループを完成させるには、 $0.1\mu F$  のコンデンサ 1 個をピン 8 の  $V_{OUT}$  とピン 7 の GND の間にのみ接続し、 $0.1\mu F$  のマッチング・コンデンサをピン 11 の VOUT とピン 12 の GND の間にのみ接続することを推奨します。これら 2 つのコンデンサは、できるだけ IC の近くに配置する必要があります。また、最大限の EMI 相殺性能を実現するには、これら 2 つのコンデンサによって形成されるループが互いに対称で、なおかつできるだけ小さくなければなりません。0402 や 0603 といったケース・サイズの小さいコンデンサは寄生インダクタンスが小さいので、この用途に最適です。更に、 $4.7\mu F$  以上のバルク・コンデンサを IC の近くに追加します。正端子を出力に、負端子をグランド・プレーンに接続してください。 $V_{IN}$ ピンと  $INTV_{CC}$ ピンのバイパス・コンデンサも、グランド・プレーンに接続する必要があります。

出力コンデンサは、インダクタや入力コンデンサと共に回路基板の同じ側に配置し、その接続も同じ層上で行います。局部的な、切れ目のない電源グランド・プレーンを、表面層に最も近い層にあるアプリケーション回路の下に配置してください。SW および BST ノードは、EMI を最小限に抑えるためにできるだけ小さくする必要があります。

また、VSET2/FB ノード(外部帰還使用時)と RT ノードを小さく保ち、SW ノードや BST ノードにより生じるノイズから FB ノードや RT ノードをグラウンド・パターンで遮蔽できるようにしてください。

analog.com.jp Rev 0 | 27 of 36

パッケージの熱抵抗を減らすために、パッケージ底面にある露出パッドはグランド・プレーンにハンダ付けする必要があります。更に、 熱抵抗を小さく保つためにグランド・プレーンをできるだけ広くし、回路基板内の広くなった電源グランド・プレーンに多数のサーマ ル・ビアを追加します。

図 43. LT8342 の推奨 PCB レイアウト

analog.com.jp Rev 0 | 28 of 36

# 標準的応用例

# 低 Iq、低 EMI の SSFM 機能付き 24V 昇圧コンバータ

図 44. 低 IQ、低 EMI の SSFM および Burst Mode 機能付き 24V 昇圧コンバータ

analog.com.jp Rev 0 | 29 of 36

# 2MHz、12V の昇圧コンバータ

図 45. 低 I<sub>Q</sub>、2MHz の 12V 昇圧コンバータ

図 46. 2MHz、12V の昇圧コンバータを Burst Mode で作動させた場合の効率と負荷電流の関係(SYNC/MODE = 0V)

analog.com.jp Rev 0 | 30 of 36

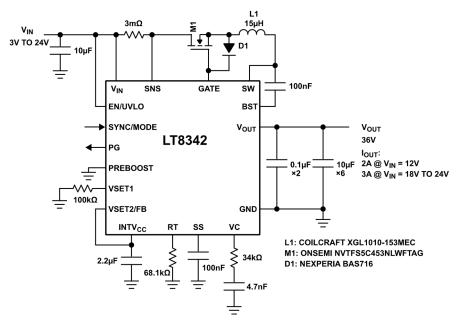

# 出力短絡保護機能を備えた 500kHz、36V、低 IQ の昇圧コンバータ

図 47. 出力短絡保護機能を備えた 500kHz、36V、低 IQの昇圧コンバータ

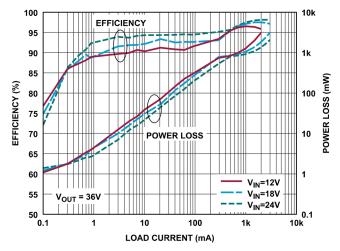

図 48. 500kHz、36V の昇圧コンバータをバースト・モードで作動させた場合の効率と負荷電流の関係(SYNC/MODE = 0V)

analog.com.jp Rev 0 | 31 of 36

# 10V 出力と短絡保護機能を備え、ストップ・スタートやコールド・クランクに適した自動車用 2MHz 事前 昇圧コンパータ

図 49. 10V 出力と短絡保護機能を備えた自動車用 2MHz 事前昇圧コンバータ

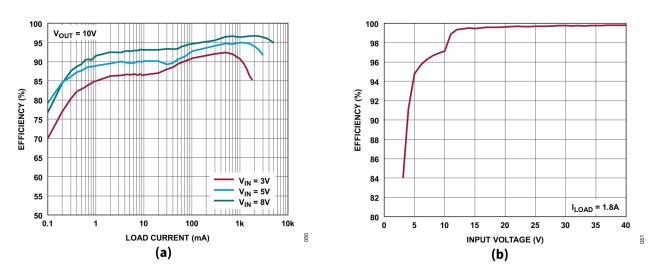

図 50. 2MHz、10V の自動車用事前昇圧コンバータを Burst Mode で作動させた場合の効率(SYNC/MODE = 0V) (a) 負荷電流との関係、(b) 1.8A 負荷電流時の入力電圧との関係

analog.com.jp Rev 0 | 32 of 36

# パッケージ情報

analog.com.jp Rev 0 | 33 of 36

# オーダー・ガイド

表 8. オーダー・ガイド

| TAPE AND REEL  | TAPE AND REEL   | PART     | PAD          | PACKAGE                                                | MSL    | TEMPERATURE    |

|----------------|-----------------|----------|--------------|--------------------------------------------------------|--------|----------------|

|                | (MINI)          | MARKING* | FINISH       | TYPE**                                                 | RATING | RANGE          |

| LT8342RV#TRPBF | LT8342RV#TRMPBF | 8342     | Au<br>(RoHS) | LQFN<br>(Laminate<br>Package<br>with QFN<br>Footprint) | 3      | −40°C to 150°C |

<sup>\*</sup>温度グレードは出荷容器のラベルに表示されています。

analog.com.jp Rev 0 | 34 of 36

<sup>\*\*</sup> LT8342 のパッケージ寸法は、標準の 4mm × 4mm QFN パッケージと同じです。

# 関連製品

表 9. オーダー・ガイド

| 製品番号            | 説明                                                                         | 注釈                                                                                                                                               |  |  |

|-----------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LT8336          | PassThruTM 機能を備えた 40V、2.5A、低 l <sub>a</sub> の同期整流式<br>昇圧 Silent Switcher   | V <sub>IN</sub> : 2.7V~40V、V <sub>OUT(MAX)</sub> = 40V、I <sub>Q</sub> = 4μA(Burst Mode<br>動作)、300kHz~3MHz にプログラム可能、16 ピン 3mm<br>× 3mm LQFN パッケージ |  |  |

| LT8337/LT8337-1 | パススルー機能(PassThru™)を備えた 28V、5A、低 I <sub>Q</sub><br>の同期整流式昇圧 Silent Switcher | V <sub>IN</sub> : 2.7V~28V、V <sub>OUT(MAX)</sub> = 28V、I <sub>Q</sub> = 4μA(バースト・モード動作)、300kHz~3MHz にプログラム可能、16 ピン 3mm×3mm LQFN パッケージ            |  |  |

| LT8338          | 40V、1.2A、低 I <sub>Q</sub> の同期整流式昇圧コンバータ                                    | V <sub>IN</sub> : 3V~40V、V <sub>OUT(MAX)</sub> = 40V、I <sub>Q</sub> = 6μA(バースト・モード動作)、300kHz~3MHz にプログラム可能、<br>MSOP-10E パッケージ                    |  |  |

| LT3957/LT3957A  | 5A/40V スイッチ内蔵の昇圧、フライバック、SEPIC、<br>および反転コンバータ                               | V <sub>IN</sub> : 3V~40V、電流モード制御、100kHz~1MHz のプロ<br>グラマブル動作周波数、5mm×6mm QFN-36 パッケージ                                                              |  |  |

| LT3958          | 3.5A/80V スイッチを内蔵した高入力電圧の昇圧、フライ<br>バック、SEPIC、および反転コンバータ                     | V <sub>IN</sub> :5V~80V、電流モード制御、100kHz~1MHz のプロ<br>グラマブル動作周波数、5mm×6mm QFN-36 パッケージ                                                               |  |  |

| LT8330          | 60V、1A、低 I <sub>Q</sub> の昇圧/SEPIC/反転 2MHz コンバータ                            | $V_{\text{IN}}$ = 3V~40V、 $V_{\text{OUT(MAX)}}$ = 60V、 $I_{\text{Q}}$ = 6 $\mu$ A(Burst Mode 動作)、6 ピン TSOT-23、3mm×2mm DFN パッケージ                  |  |  |

| LT8362          | 60V、2A、低 I <sub>Q</sub> の昇圧/SEPIC/反転コンバータ                                  | V <sub>IN</sub> = 2.8V~60V、V <sub>OUT(MAX)</sub> = 60V、I <sub>Q</sub> = 9μA(バースト・モード動作)、MSOP-16(12)E、3mm×3mm DFN-10 パッケージ                        |  |  |

| LT8364          | 60V、4A、低 I <sub>Q</sub> の昇圧/SEPIC/反転コンバータ                                  | V <sub>IN</sub> = 2.8V~60V、V <sub>OUT(MAX)</sub> = 60V、I <sub>Q</sub> = 9µA(バースト・モード動作)、MSOP-16(12)E、4mm×3mm DFN-12 パッケージ                        |  |  |

analog.com.jp Rev 0 | 35 of 36

ここに含まれるすべての情報は、現状のまま提供されるものであり、アナログ・デバイセズはそれに関するいかなる種類の保証または表明も行いません。アナログ・デバイセズは、その情報の利用に関して、また利用によって生じる第三者の特許またはその他の権利の侵害に関して、一切の責任を負いません。仕様は予告なく変更されることがあります。明示か黙示かを問わず、アナログ・デバイセズ製品またはサービスが使用される組み合わせ、機械、またはプロセスに関するアナログ・デバイセズの特許権、著作権、マスクワーク権、またはその他のアナログ・デバイセズの知的財産権に基づくライセンスは付与されません。商標および登録商標は、各社の所有に属します。