# 50~1000MHz⊘ 直交復調器

**AD8348**

### 特長

IF VGAアンプ内蔵のI/Q復調器 動作IF周波数:50~1000MHz

(R<sub>s</sub>=200Ωから駆動する500MHzの3dB IF BW)

復調帯域幅:75MHz

デシベル・リニアAGCレンジ:44dB

3次インターセプト

最小ゲインでIIP3+28dBm (F<sub>IE</sub>=380MHz) 最大ゲインでIIP3-8dBm (F<sub>IE</sub>=380MHz)

直交復調精度

位相精度: 0.5°

振幅バランス: 0.25dB

最大ゲインでのノイズ係数:11dB(F<sub>IF</sub>=380MHz)

LO入力:-10dBm 単電源: 2.7~5.5V パワーダウン・モード

小型の28ピンTSSOPパッケージ

### アプリケーション

QAM/QPSK復調器 W-CDMA/CDMA/GSM/NADC ワイヤレス・ローカル・ループ **LMDS**

### 概要

AD8348は、中間周波数 (IF) 可変ゲイン・アンプ (VGA) と ベースバンド・アンプを内蔵するブロードバンド直交復調器 (クワドラチャー・デモジュレータ)です。通信受信機での使 用に適しており、IFから直接ベースバンド周波数へ直交復調を 行います。ベースバンド・アンプをAD9201、AD9283、 AD9218などのデュアル・チャンネルA/Dコンバータ (ADC) に直接インターフェースして、デジタル化と後処理を行う設計 になっています。

X-AMP® VGAを通じて、IF入力信号を2つのギルバート・セ ル・ミキサーに入力します。IF VGAから44dBのゲイン制御が 得られます。高精度のゲイン制御回路によって、VGAに特有 のdB直線性ゲイン特性を設定し、温度補償を行います。LO直 交位相スプリッタが2分周の周波数分周器を使用して、動作周 波数範囲の全域にわたって高い直交精度と振幅バランスを実現 します。

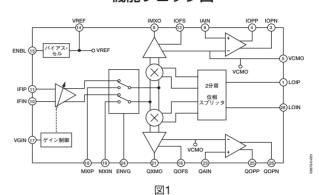

### 機能ブロック図

オプションで、IF VGAをディスエーブルにしてバイパスする ことも可能です。このモードでは、MXIPピンとMXINピンを 介してIF信号を直交ミキサー入力に直接印加します。

ミキサーのベースバンド出力の後に、独立したIチャンネルとQ チャンネルのベースバンド・アンプが続きます。VCMOピンに 印可する電圧によって、ベースバンド出力のDCコモン・モー ド電圧レベルが設定されます。VCMOは一般に内部VREF電圧 に接続しますが、外部電圧に接続することもできます。このよ うな柔軟性によって、ADCへの入力ダイナミック・レンジを最 大化することができます。各オフセット補償入力(IOFSと OOFS) でバイパス・コンデンサを接続すると、ミキサー内で 発生するDCオフセットがゼロになります。オフセット補償を 無効にするには、オフセット補償入力に外部電圧を印可しま

ミキサーの出力は、最終増幅の前にオプションのフィルタ処理 を行うためにオフチップにします。各ベースバンド・アンプの 前にチャンネル選択フィルタを挿入し、ベースバンド信号を I/Qベースバンド・アンプに入力する前に高レベルのチャンネ ル外干渉の振幅を減らすことによって、ベースバンド・アンプ の信号処理範囲が拡大します。シングルエンドのミキサー出力 が増幅され、ADCを駆動する差動信号に変換されます。

アナログ・デバイセズ社は、提供する情報が正確で信頼できるものであることを期していますが、その情報の プリーフ・アルー とんせん、北京パッと同様などのものというのからとしておりているようが、というによい。 利用に関して、あるいは利用によって生じる第三者の特許やその他の権利の侵害に関して一切の責任を負いません。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもので せん。また、アナログ・デバイセズ社の特許または特許の権利の使用を明示的または暗示的に許諾するもので もありません。本紙記載の商標および登録商標は、各社の所有に属します。 ※日本語データシートはREVISIONが古い場合があります。最新の内容については、英語版をご参照ください。

© 2003 Analog Devices, Inc. All rights reserved.

REV. 0

# 目次

| 基本的な接続               | 20                                                                                                                                           |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 電源                   | 20                                                                                                                                           |

| デバイス・イネーブル           | 20                                                                                                                                           |

| VGAイネーブル             | 20                                                                                                                                           |

| ゲイン制御                | 20                                                                                                                                           |

| LO入力                 | 20                                                                                                                                           |

| IF入力                 | 20                                                                                                                                           |

| MX入力                 | 20                                                                                                                                           |

| ベースバンド出力             | 21                                                                                                                                           |

| 出力のDCバイアス・レベル        | 21                                                                                                                                           |

| AGC動作用の検出器へのインターフェース | 21                                                                                                                                           |

| ベースバンド・フィルタ          | 22                                                                                                                                           |

| LOの生成                | 23                                                                                                                                           |

| 評価用ボード               | 23                                                                                                                                           |

| 外形寸法                 | 28                                                                                                                                           |

| ESDに関する注意            | 28                                                                                                                                           |

| オーダー・ガイド             | 28                                                                                                                                           |

|                      | 電源. デバイス・イネーブル. VGAイネーブル ゲイン制御. LO入力. IF入力. MX入力. ベースバンド出力. 出力のDCバイアス・レベル. AGC動作用の検出器へのインターフェース ベースパンド・フィルタ. LOの生成. 評価用ボード. 外形寸法. ESDに関する注意. |

## 改訂履歴

リビジョン0:初版

# 仕様

表1. (特に指定のない限り、 $V_s$ =5V、 $T_A$ =25 $^\circ$ C、 $F_{LO}$ =380MHz、 $F_{IF}$ =381MHz、 $P_{LO}$ =-10dBm、 $R_S$  (LO) =50 $\Omega$ 、 $R_S$  (IFIPおよびMXIP/MXIN) =200 $\Omega$ )

| パラメータ                 | 条件                                               | Min | Тур      | Max  | 単位            |

|-----------------------|--------------------------------------------------|-----|----------|------|---------------|

| 動作条件                  |                                                  |     |          |      |               |

| LO周波数レンジ              | 外部入力=2×LO周波数                                     | 100 |          | 2000 | MHz           |

| IF周波数レンジ              |                                                  | 50  |          | 1000 | MHz           |

| ベースバンド帯域幅             |                                                  |     | 75       |      | MHz           |

| LO入力レベル               | $50\Omega$ V $-$ Z                               | -12 | -10      | 0    | dBm           |

| $V_{SUPPLY}(V_S)$     |                                                  | 2.7 |          | 5.5  | V             |

| 温度範囲                  |                                                  | -40 |          | +85  | °C            |

| VGA付きのIFフロントエンド       | IFIP~IMXO (QMXO)                                 |     |          |      |               |

|                       | ENVG=5V                                          |     |          |      |               |

| 入力インピーダンス             |                                                  |     | 200  1.1 |      | $\Omega$ llpF |

| ゲイン制御範囲               |                                                  |     | 44       |      | dB            |

| 最大変換ゲイン               | VGIN=0.2V(最大電圧ゲイン)                               |     | 25.5     |      | dB            |

| 最小変換ゲイン               | VGIN=1.2V(最小電圧ゲイン)                               |     | -18.5    |      | dB            |

| 3dB帯域幅                |                                                  |     | 500      |      | MHz           |

| ゲイン制御直線性              | $VGIN=0.4V (+21dB) \sim 1.1V (-14dB)$            |     | ±0.5     |      | dB            |

| IFゲイン平坦性              | $F_{IF} = 380 MHz \pm 5\% \text{ (VGIN} = 1.2V)$ |     | 0.1      |      | dB p-p        |

|                       | $F_{IF} = 900MHz \pm 5\% \text{ (VGIN} = 1.2V)$  |     | 1.3      |      | dB p-p        |

| 入力P1dB                | VGIN=0.2V (最大ゲイン)                                |     | -22      |      | dBm           |

|                       | VGIN=1.2V(最大ゲイン)                                 |     | +13      |      | dBm           |

| 2次入力インターセプト (IIP2)    | IF1=385MHz, IF2=386MHz                           |     |          |      |               |

| ,                     | 200Ωソースからの各トーン+3dBm                              |     | 65       |      | dBm           |

|                       | VGIN=1.2V(最小ゲイン)                                 |     |          |      |               |

|                       | 200Ωソースからの各トーンー42dBm                             |     | 18       |      | dBm           |

|                       | VGIN=0.2V (最大ゲイン)                                |     |          |      |               |

| 3次入力インターセプト(IIP3)     | IF1=381MHz, IF2=381.02MHz                        |     |          |      |               |

|                       | 各トーンは200ΩソースからのPldBよりも10dB下                      |     | 28       |      | dBm           |

|                       | VGIN=1.2V (最小ゲイン)                                |     | -0       |      | 02111         |

|                       | 各トーンは200ΩソースからのP1dBよりも10dB下                      |     | -8       |      | dBm           |

|                       | VGIN=0.2V (最大ゲイン)                                |     |          |      | 42111         |

| LOリーク                 | IFIP、IFINで測定                                     |     | -80      |      | dBm           |

|                       | IMXO/QMXOで測定(LO=50MHz)                           |     | -60      |      | dBm           |

| 復調帯域幅                 | 小信号3dB带域幅                                        |     | 75       |      | MHz           |

| 直交位相誤差                | LO=380MHz (LOIP/LOIN 760MHz)                     | -2  | ±0.5     | +2   | 度             |

| I/Q振幅アンバランス           | EO 300MIE (EON/EON/700MIE)                       |     | 0.25     | ' -  | dB            |

| ノイズ係数                 | 最大ゲインで $200\Omega$ ソースから、 $F_{IF}$ = $380MHz$    |     | 10.75    |      | dB            |

| ミキサー出力インピーダンス         | % 1 F 300WIII                                    |     | 40       |      | Ω             |

| 容量性負荷                 | IMXO、QMXOからVCMOに分流                               | 0   | 1        | 10   | pF            |

| 抵抗性負荷                 | IMXO、QMXOからVCMOに分流<br>IMXO、QMXOからVCMOに分流         | 200 | 1.5k     | 10   | $\Omega$      |

| 私が注意何<br>ミキサーのピーク出力電流 | INIAO, QIVIAON O VCIVIO (C) I (III               | 200 | 2.5      |      | mA            |

| マモケ グロガ电弧             |                                                  |     | 2.5      |      | 111/1         |

REV. 0 — 3 —

| パラメータ                                                                                                                    | 条件                                                                                                                                                                                                                                                                                        | Min                                    | Тур                                                                                                                          | Max                                  | 単位                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| VGAなしのIFフロントエンド                                                                                                          | MXIP、MXINからIMXO(QMXO)まで<br>ENVG=0V、IMXO/QMXO負荷=1.5kΩ<br>MXIP/MXINの両端を差動で測定<br>F <sub>IF</sub> =380MHz±5%<br>F <sub>IF</sub> =900MHz±5%<br>IF1=381MHz、IF2=381.02MHz<br>各トーンは200ΩソースからのP1dBよりも10dB下<br>MXIP/MXINで測定<br>IMXO、QMXOで測定<br>小信号3dB帯域幅<br>LO=380MHz(LOIP/LOIN 760MHz、<br>シングルエンド) | -2                                     | $\begin{array}{c} 200    1.5 \\ 10.5 \\ 75 \\ 0.1 \\ 0.15 \\ -4 \\ 14 \\ -70 \\ -60 \\ 75 \\ \pm 0.5 \end{array}$            | +2                                   | ΩllpF<br>dB<br>MHz<br>dB p-p<br>dB p-p<br>dBm<br>dBm<br>dBm                                                                   |

| I/Q振幅アンバランス<br>ノイズ係数                                                                                                     | $200\Omega$ ソースから、 $F_{IF}$ =380MHz                                                                                                                                                                                                                                                       |                                        | 0.25<br>21                                                                                                                   |                                      | dB<br>dB                                                                                                                      |

| //Qベースバンド・アンプ ゲイン 帯域幅 出力DCオフセット (差動) 出力コモン・モード・オフセット 群遅延平坦性 入力換算ノイズ電圧 出力振幅限界 (上側) 出力振幅限界 (下側) ピーク出力電流 入力インピーダンス 入力バイアス電流 | IAIN~IOPP/IOPNおよびQAIN~QOPP/QOPN、 $R_{LOAD} = 2k\Omega$ 、グラウンドにシングルエンド接続 $10pF 差動負荷$ IOFS、QOFS( $V_{IOPP} - V_{IOPN}$ )で500 $pF$ コンデンサを使用して補正されたLOリーク・オフセット( $V_{IOPP} + V_{IOPN}$ )/2 $- VCMO$ 0~50MHz 周波数 $= 1$ MHz                                                                      | -50<br>-75<br>V <sub>s</sub> -1        | $ \begin{array}{c} 20 \\ 125 \\ \pm 12 \end{array} $ $ \pm 35 \\ 3 \\ 8 $ $ \begin{array}{c} 1 \\ 50 \\ 1 \\ 2 \end{array} $ | +50<br>+75<br>0.5                    | $\begin{array}{c} dB \\ MHz \\ mV \\ \\ mV \\ ns \ p-p \\ nV/\sqrt{Hz} \\ V \\ V \\ mA \\ k\Omega    pF \\ \mu A \end{array}$ |

| IFおよびMX入力から<br>ベースバンド・アンプ出力への応答<br>ゲイン                                                                                   | IMXOとQMXOはそれぞれIAINとQAINに直接接続 MXIP/MXINから IFIP/IFINから、VGIN=0.2V IFIP/IFINから、VGIN=1.2V                                                                                                                                                                                                      |                                        | 30.5<br>45.5<br>1.5                                                                                                          |                                      | dB<br>dB<br>dB                                                                                                                |

| コントロール入/出力<br>VCMO入力レンジ<br>VREF出力電圧<br>ゲイン制御電圧範囲<br>ゲイン・スロープ<br>ゲイン・インターセプト<br>ゲイン制御入力バイアス電流                             | $V_S$ =5V $V_S$ =2.7V $V$ GIN $V$ GIN=0Vでの理論上のゲインへの線形外挿                                                                                                                                                                                                                                   | 0.5<br>0.5<br>0.95<br>0.2<br>-55<br>55 | 1<br>1<br>1<br>-50<br>61                                                                                                     | 4<br>1.7<br>1.05<br>1.2<br>-45<br>67 | V<br>V<br>V<br>V<br>dB/V<br>dB<br>µA                                                                                          |

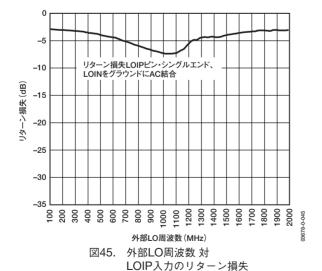

| LO入力<br>LOIP入力リターン損失                                                                                                     | LOINはグラウンドにAC結合<br>(LOIPに760MHzを印加)                                                                                                                                                                                                                                                       |                                        | -6                                                                                                                           |                                      | dB                                                                                                                            |

| パラメータ              | 条件                    | Min      | Тур     | Max      | 単位 |

|--------------------|-----------------------|----------|---------|----------|----|

| パワーアップ制御           |                       |          |         |          |    |

| ENBLスレッショールド・ローレベル | ローレベル=スタンバイ           | 0        | $V_s/2$ | 1        | V  |

| ENBLスレッショールド・ハイレベル | ハイレベル=イネーブル           | $+V_s-1$ | $V_s/2$ | $+V_{S}$ | V  |

| 入力バイアス電流           |                       |          | 2       |          | μΑ |

| パワーアップ時間           | 最終ベースバンド・アンプが         |          | 45      |          | μs |

|                    | 最終振幅の90%以内になるまでの時間    |          |         |          |    |

| パワーダウン時間           | 電源電流が有効値の<10%になるまでの時間 |          | 700     |          | ns |

| 電源                 | VPOS1, VPOS2, VPOS3   |          |         |          |    |

| 電圧                 |                       | 2.7      |         | 5.5      | V  |

| 電流 (イネーブル)         | $V_{POS} = 5V$        | 38       | 48      | 58       | mA |

| 電流 (スタンバイ)         | $V_{POS} = 5V$        |          | 75      |          | μΑ |

REV. 0 — 5 —

## 絶対最大定格\*

#### 表2. AD8348の絶対最大定格

| パラメータ            | 定格             |

|------------------|----------------|

| 電源電圧VPOS1、VPOS2、 | 5.5V           |

| VPOS3            |                |

| LO入力電力           | 10dBm(抵抗:50Ω)  |

| IF入力電力           | 18dBm(抵抗:200Ω) |

| 内部消費電力           | 450mW          |

| $	heta_{ m JA}$  | 68℃/W          |

| 最大ジャンクション温度      | 150℃           |

| 動作温度範囲           | -40~+85°C      |

| 保存温度範囲           | -65~+125°C     |

| ピン温度(ハンダ処理、60秒)  | 300℃           |

<sup>\*</sup> 上記の絶対最大定格を超えるストレスを加えると、デバイスに恒久的な損傷を与えることがあります。この規定はストレス定格のみを指定するものであり、この仕様の動作に関するセクションに記載されている規定値以上でのデバイス動作を定めたものではありません。長時間デバイスを絶対最大定格状態に置くと、デバイスの信頼性に影響を与えることがあります。

─6 ─ REV. 0

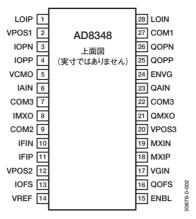

# ピン配置と機能の説明

図2. 28ピンTSSOP

表3. ピン機能の説明 - 28ピンTSSOP

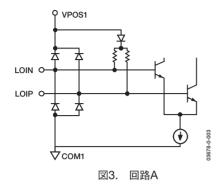

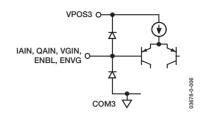

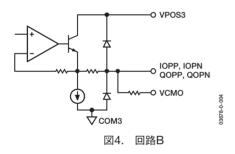

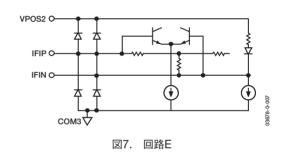

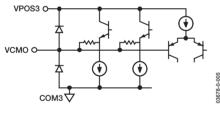

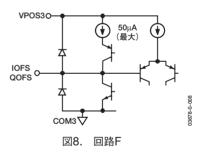

| ピン番号         | 記号                     | 説明                                                                                                                                                                                                                                                                                                                                                                                 | 等価回路 |

|--------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

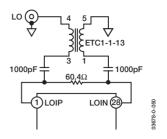

| 1、28         | LOIP, LOIN             | LO入力。最適な性能を得るには、これらの入力をAC結合して差動で駆動してください。シングルエンド信号源からの差動駆動はバラン回路によって実現できます。ブロードバンドの $50\Omega$ 入力インピーダンスを得るには、LOIPとLOINの間に $60.4\Omega$ のシャント抵抗を接続します。代表的な入力駆動レベルは $-10dB$ mです。                                                                                                                                                                                                    | A    |

| 2, 12, 20    | VPOS1, VPOS2, VPOS3    | それぞれ、LO、IF、バイアスとベースバンド・セクション用の正電源。これらのピンは、0.1μFと100pFのコンデンサでデカップリングしてください。                                                                                                                                                                                                                                                                                                         |      |

| 3, 4, 25, 26 | IOPN, IOPP, QOPP, QOPN | IチャンネルとQチャンネルの差動ベースバンド出力。代表的な出力振幅は 2Vp-p差動に等しくなります。これらのピンのDCコモン・モード電圧レベルは、VCMOの電圧で設定されます。                                                                                                                                                                                                                                                                                          | В    |

| 5            | VCMO                   | ベースバンドDCコモン・モード電圧。すべてのベースバンド出力と入力 (IMXO、QMXO、IOPP、IOPN、QOPP、QOPN、IAIN、QAIN) のDCコモン・モード・レベルはこのピンに印可される電圧によって設定されます。 このピンは、VREFに接続したり、他のデバイス(一般にはADC)のリファレンスに接続したりできます。                                                                                                                                                                                                              | С    |

| 6, 23        | IAIN, QAIN             | IチャンネルとQチャンネルのベースバンド・アンプ入力。これらのピンのシングルエンド信号はVCMOを基準としており、VCMOピンのDC電圧に等しいDCバイアスが必要です。IMXO(QMXO)がIAIN(QAIN)にDC結合されている場合、IMXO(QMXO)によってバイアスが与えられます。IMXOとIAINの間にAC結合されたフィルタを置く場合は、1kΩの抵抗でVCMOを駆動するソースからこれらのピンをバイアスできます。IAIN/QAINから差動出力(IOPP/IOPNとQOPP/QOPN)へのゲインは20dBです。                                                                                                               | D    |

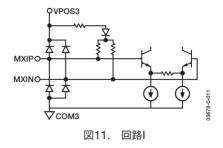

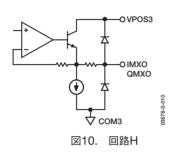

| 7、22<br>8、21 | COM3<br>IMXO、QMXO      | バイアスとベースバンド・セクション用のグラウンド $I$ チャンネル/ $Q$ チャンネル・ミキサーのベースバンド出力。これらは低インピーダンス( $40\Omega$ )出力で、そのバイアス・レベルは $VCMO$ ピンに印可される電圧によって設定されます。これらのピンはそれぞれ $I$ AINと $Q$ AINに接続するのが普通ですが、直接接続する場合と、フィルタを介して接続する場合があります。各出力は、 $2.5$ mAの最大電流を駆動できます。                                                                                                                                               | Н    |

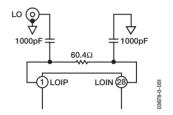

| 9<br>10、11   | COM2<br>IFIN、IFIP      | IFセクション・グラウンド IF入力。IFINはグラウンドにAC結合してください。シングルエンドIF入力 信号は、IFIPにAC結合してください。これらのピンの公称差動入力インピーダンスは200 $\Omega$ です。プロードバンドの50 $\Omega$ 入力インピーダンスを実現するには、損失が最小のLパッドを使用してください( $R_{SERIES}$ =174 $\Omega$ 、 $R_{SHUNT}$ =57.6 $\Omega$ )。これによって、IF入力に200 $\Omega$ のソース・インピーダンスが与えられます。ただし、AD8348には必ずしも200 $\Omega$ のソース・インピーダンスは必要ありません。IFIPとIFINの間にシングル・シャントの66.7 $\Omega$ 抵抗を置くこともできます。 | Е    |

| 13、16        | IOFS、QOFS              | Iチャンネル/Qチャンネル・オフセットのゼロ設定入力。Iチャンネル・ミキサー出力(IMXO)のDCオフセットは、IOFSからグラウンドに $0.1\mu$ Fのコンデンサを接続してゼロにすることができます。固定電圧でIOFSを駆動すれば(一般に、IOPP/IOPNでのオフセットがゼロになるようにキャリブレートされたD/Aコンバータ(DAC))、DCを含むように動作周波数レンジを拡張できます。同様に、QOFSピンを使用すれば、Qチャンネル・ミキサー出力(QMXO)でのオフセットをゼロにできます。                                                                                                                          | F    |

REV. 0 —7—

| ピン番号  | 記号        | 説明                                                                                                                                                                                                                                                          | 等価回路 |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

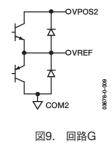

| 14    | VREF      | リファレンス出力。この出力電圧 (1V) は、デバイスのメイン・バイアス・レベルで、ベースバンド・アンプの入力と出力を外部的にバイアスすることができます。この出力の代表的な最大駆動電流は2mAです。                                                                                                                                                         | G    |

| 15    | ENBL      | チップ・イネーブル入力。アクティブ・ハイレベル。スレッショールドは $+V_s/2$ です。                                                                                                                                                                                                              | D    |

| 17    | VGIN      | ゲイン制御入力。このピンの電圧でIF VGAのゲインを制御します。ゲイン<br>制御電圧範囲は0.2~1.2Vであり、+25.5~-18.5dBの変換ゲイン・レンジ<br>に対応します。これはミキサーの出力(IMXOとQMXO)へのゲインです。<br>最終のベースバンド・アンプ(IAIN~IOPP/IOPNおよびQAIN~QOPP<br>/QOPN)には、さらに20dBの固定ゲインがあります。なお、ゲイン制御機<br>能は電圧と逆の制御になっています(電圧が増大するとゲインが減少しま<br>す)。 | D    |

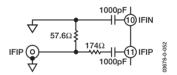

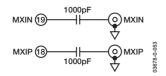

| 18、19 | MXIP、MXIN | 補助ミキサー入力。ENVGがローレベルの場合、IFIP入力とIFIN入力がディスエーブルになり、MXIP入力とMXIN入力がイネーブルになるため、VGAをバイパスすることができます。これらはフル差動入力であり、信号源にAC結合してください。                                                                                                                                    |      |

| 24    | ENVG      | アクティブ・ハイレベルVGAイネーブル。ENVGがハイレベルの場合、IFIP入力とIFIN入力がイネーブルになり、MXIP入力とMXIN入力がディスエーブルになります。ENVGがローレベルの場合、MXIP入力とMXIN入力がイネーブルになり、IFIP入力とIFIN入力がディスエーブルになります。                                                                                                        | D    |

| 27    | COM1      | LOセクション・グラウンド                                                                                                                                                                                                                                               |      |

\_8\_ REV. 0

# 等価回路

図6. 回路D

図5. 回路C

REV. 0 — 9 —

# 代表的な性能特性

### VGAと復調器

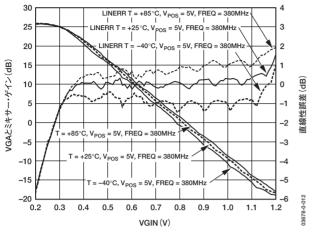

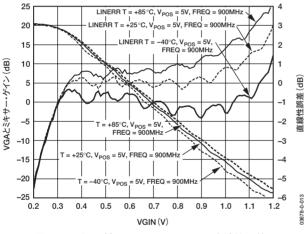

図12. VGIN 対 ミキサー・ゲインと直線性誤差 (V<sub>POS</sub>=5V、F<sub>IF</sub>=380MHz、F<sub>BB</sub>=1MHz、 温度=-40℃、+25℃、+85℃)

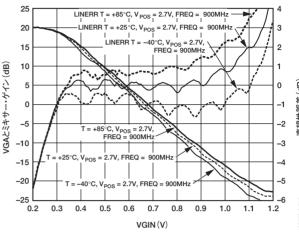

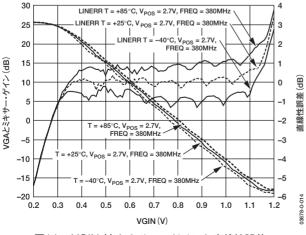

図15. VGIN 対 ミキサー・ゲインと直線性誤差 (V<sub>POS</sub>=2.7V、F<sub>IF</sub>=900MHz、F<sub>BB</sub>= 1MHz、温度=-40℃、+25℃、+85℃)

図13. VGIN 対 ミキサー・ゲインと直線性誤差  $(V_{POS}=5V, F_{IF}=900MHz, F_{BB}=1MHz,$  温度=-40 $^{\circ}$ 、+25 $^{\circ}$ C、+85 $^{\circ}$ C)

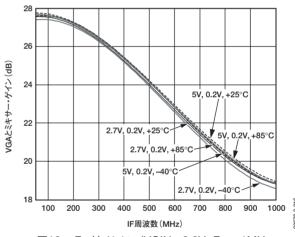

図16. F<sub>IF</sub> 対 ゲイン (VGIN=0.2V、F<sub>BB</sub>=1MHz、 温度=-40°C、+25°C、+85°C)

図14. VGIN 対 ミキサー・ゲインと直線性誤差 (V<sub>POS</sub>=2.7V、F<sub>IF</sub>=380MHz、F<sub>BB</sub>= 1MHz、温度=-40℃、+25℃、+85℃)

— 11 —

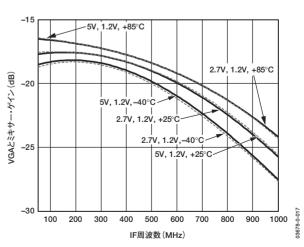

図17. F<sub>IF</sub>対 ゲイン(VGIN=1.2V、F<sub>BB</sub>= 1MHz、温度=-40℃、+25℃、+85℃)

REV. 0

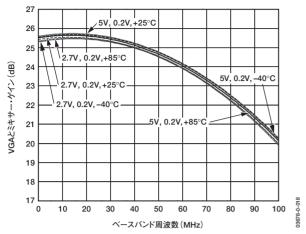

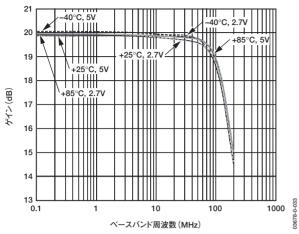

図18. F<sub>BB</sub> 対 ゲイン(VGIN=0.2V、 F<sub>IF</sub>=380MHz、V<sub>POS</sub>=2.7V、5V、 温度=-40℃、+25℃、+85℃)

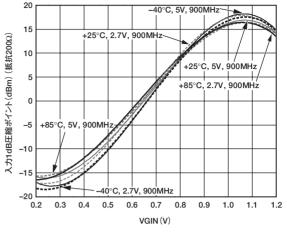

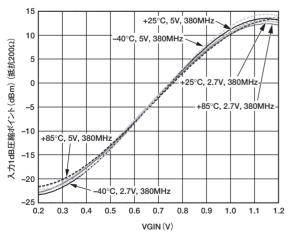

図21. VGIN 対 入力1dB圧縮ポイント (IP1dB) (F<sub>IF</sub>=900MHz、F<sub>BB</sub>=1MHz、V<sub>POS</sub>=2.7V、5V、温度=-40℃、+25℃、+85℃)

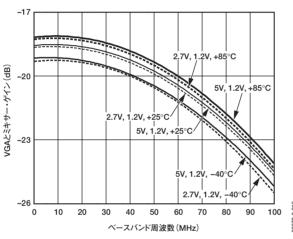

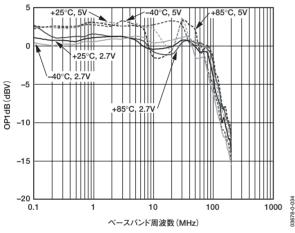

図19. F<sub>BB</sub> 対 ゲイン(VGIN=1.2V、 F<sub>IF</sub>=380MHz、V<sub>POS</sub>=2.7V、5V、 温度=-40°、+25°、+85°)

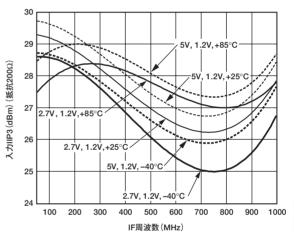

図22. F<sub>IF</sub> 対 IIP3 (VGIN=1.2V、F<sub>BB</sub>=1MHz、 V<sub>POS</sub>=2.7V、5V、温度=-40°C、 +25°C、+85°C、トーン間隔=20kHz)

図20. VGIN 対 入力1dB圧縮ポイント (IP1dB) (F<sub>IF</sub>=380MHz、F<sub>BB</sub>=1MHz、 V<sub>POS</sub>=2.7V、5V、温度=-40℃、 +25℃、+85℃)

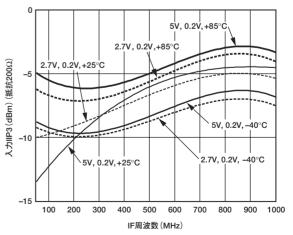

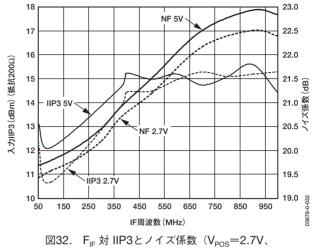

図23.  $F_{\rm IF}$  対 IIP3(VGIN=0.2V、 $F_{\rm BB}$ =1MHz、 $V_{\rm POS}$ =2.7V、5V、温度= $-40^{\circ}$ C、 $+25^{\circ}$ C、 $+85^{\circ}$ C)

— 12 — REV. 0

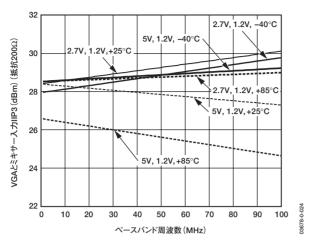

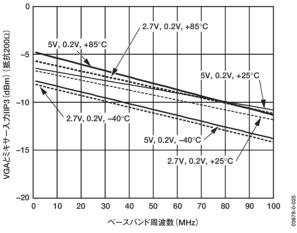

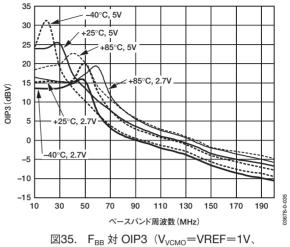

図24.  $F_{BB}$  対 IIP3(VGIN=1.2V、 $F_{IF}$ = 380MHz、 $V_{POS}$ =2.7V、5V、 温度= $-40^{\circ}$ C、 $+25^{\circ}$ C、 $+85^{\circ}$ C)

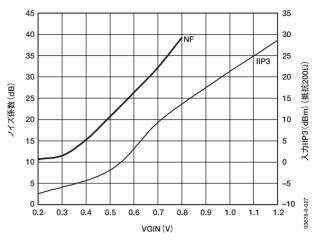

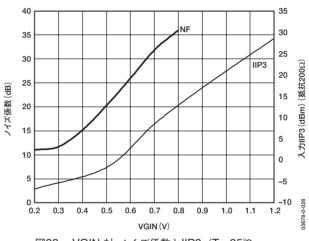

図27. VGIN 対 ノイズ係数とIIP3(T=25℃、 F<sub>IF</sub>=380MHz、F<sub>BB</sub>=1MHz、V<sub>POS</sub>=2.7V)

図25.  $F_{BB}$  対 IIP3(VGIN=0.2V、 $F_{IF}$ = 380MHz、 $V_{POS}$ =2.7V、5V、 温度=-40 $^{\circ}$ 、+25 $^{\circ}$ C、+85 $^{\circ}$ C)

図28. VGIN 対 ノイズ係数とIIP3(T=25 $^{\circ}$ 、  $F_{\text{IF}}$ =380MHz、 $F_{\text{BB}}$ =1MHz、 $V_{\text{POS}}$ =5V)

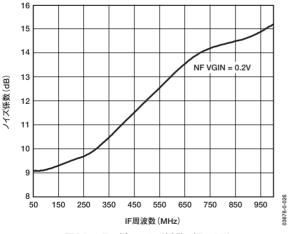

図26. F<sub>IF</sub> 対 ノイズ係数(T=25℃、 VGIN=0.2V、F<sub>BB</sub>=1MHz)

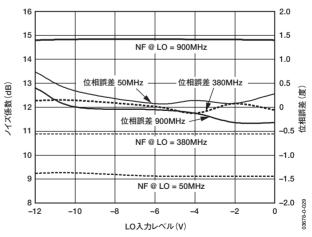

図29. LO入力レベル 対 ノイズ係数と直交位相 誤差IMXO-QMXO(T=25℃、 VGIN=0.2V、F<sub>IF</sub>=50MHz、380MHz、 900MHzに対してV<sub>POS</sub>=5V)

REV. 0 — 13 —

### MXIPとMXINを使用する復調器

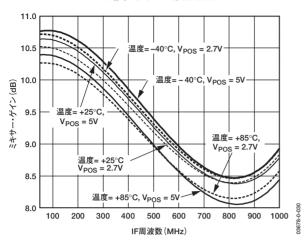

図30.  $F_{IF}$  対 ミキサー・ゲイン( $V_{POS}$ =2.7V、 5V、 $F_{BB}$ =1MHz、温度= $-40^{\circ}$ C、 +25℃、+85℃)

5V、温度25℃)

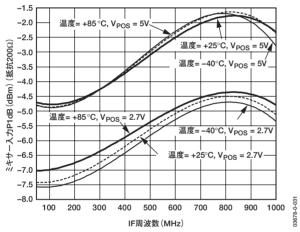

図31.  $F_{IF}$  対 入力1dB圧縮ポイント (F<sub>BB</sub>=1MHz、V<sub>POS</sub>=2.7V、5V、 温度=-40℃、+25℃、+85℃)

### 最終ベースバンド・アンプ

図33. F<sub>BB</sub> 対 ゲイン(V<sub>VCMO</sub>=VREF=1V、 V<sub>POS</sub>=2.7V、5V、温度=-40°C、 +25°C、+85°C)

図35. F<sub>BB</sub> 対 OIP3(V<sub>VCMO</sub>=VREF=1V、 V<sub>POS</sub>=2.7V、5V、温度=-40℃、 +25℃、+85℃)

図34.  $F_{BB}$  対 OP1dB圧縮( $V_{VCMO}$ =VREF=1V、 $V_{POS}$ =2.7V、5V、温度= $-40^{\circ}$ C、 $+25^{\circ}$ C、 $+85^{\circ}$ C)

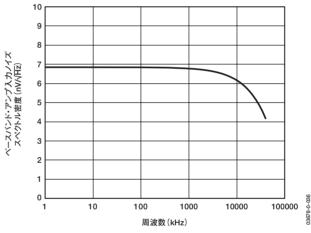

図36. ノイズ・スペクトル密度

REV. 0 — 15 —

### VGA/復調器とベースバンド・アンプ

図37.  $F_F$  対 直交位相誤差 (VGIN=0.7V、  $V_{POS}$ =2.7V、5V、温度= $-40^{\circ}$ C、  $+25^{\circ}$ C、  $+85^{\circ}$ C)

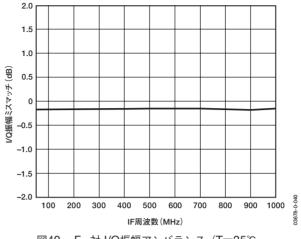

図40. F<sub>IF</sub>対 I/Q振幅アンバランス(T=25℃、 V<sub>POS</sub>=5V)

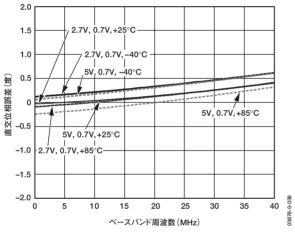

図38.  $F_{BB}$  対 直交位相誤差(VGIN=0.7V、 $V_{POS}$ =2.7V、5V、温度= $-40^{\circ}$ C、 $+25^{\circ}$ C、 $+85^{\circ}$ C、 $F_{IF}$ =380MHz)

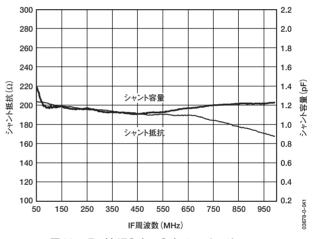

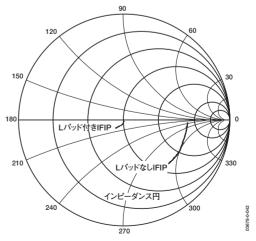

図41. F<sub>IF</sub>対 IF入力の入力インピーダンス (VGIN=0.7V、V<sub>POS</sub>=5V)

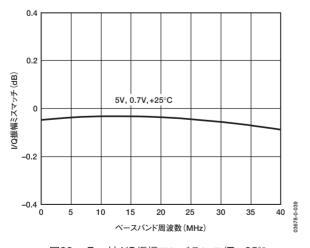

図39.  $F_{BB}$  対 I/Q振幅アンバランス (T=25  $^{\circ}$   $V_{POS}=5V)$

図42.  $F_{IF}$  対 IF入力のS11( $F_{IF}$ =50MHz~1GHz、VGIN=0.7V、 $V_{POS}$ =5V(Lパッド付き、パッドなし、50 $\Omega$ に正規化))

— 16 — REV. 0

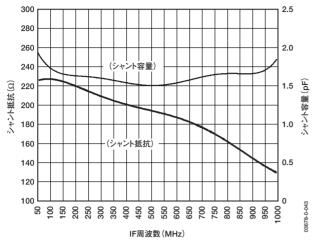

図43.  $F_{\text{IF}}$  対 ミキサー入力の入力インピーダンス  $(VGIN=0.7V,\ V_{POS}=5V)$

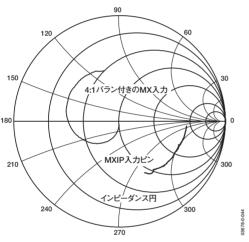

図44.  $F_{\text{IF}}$  対 ミキサー入力のS11 ( $F_{\text{IF}}$ =50MHz  $\sim$  1GHz、VGIN=0.7V、 $V_{\text{POS}}$ =5V(バランがある場合とない場合))

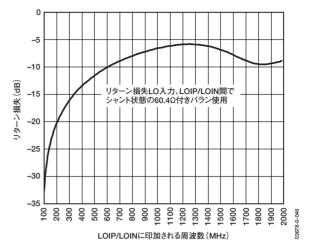

図46. バランを通じての外部LO周波数 対 LO 入力のリターン損失(終端抵抗付き)

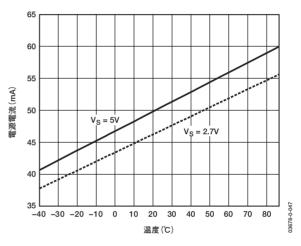

図47. 温度 対 電源電流

REV. 0 — 17 —

#### 動作原理

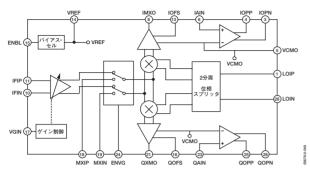

図48. 機能ブロック図

#### **VGA**

VGAは、特許取得済みのX-AMPアーキテクチャを使用して実 装されています。シングルエンドIF信号は、R-2Rラダーに よって6dBずつ8ステップで減衰されます。段階的に減衰され た各IF信号をトランスコンダクタンス段の入力に印加します。 すべてのトランスコンダクタンス段の電流出力を加算し、 VGAの出力で抵抗性負荷を駆動します。温度補償したイン ターポレーション回路によって、関連するトランスコンダクタ ンス段をスムーズにオン/オフしてゲイン制御を行います。こ の方式によって、デシベル・リニア・ゲイン制御で44dBの範 囲にわたってゲインを連続的に変化させることが可能になりま す。また、この構成では、ゲイン設定できる範囲内で相対ダイ ナミック・レンジを一定(たとえばIIP3-NF、dB単位)に保 ちます。ただし、絶対的な相互変調インターセプトとノイズ係 数は、ゲインに正比例して変化します。アナログ電圧VGINで ゲインを設定します。VGIN=0.2Vが最大、VGIN=1.2Vが最 小の電圧ゲイン設定値になります。

#### ダウンコンバージョン・ミキサー

VGAの出力で、2つのダブル・バランス型ギルバート・セル・ダウンコンバージョン・ミキサー(IとQ)を駆動します。またはENVGピンをローレベルに駆動して、VGAをディスエーブルにし、MXIPおよびMXINポートを介してミキサーを外部から直接駆動することもできます。ミキサーの入力では、差動ペアが直線的に電圧から電流に変換されます。差動出力電流をミキサー・コアに入力し、そこでギルバート・セルのミキシング・アクションによってダウンコンバートします。位相スプリッタが直交LO信号を提供し、これが同相ミキサーと直交ミキサーのLOポートを駆動します。

各ミキサーの出力にあるバッファがIMXOピンとQMXOピンを駆動します。これらの直線的な低出力インピーダンスをもったバッファは、それぞれの出力ピン(IMXOとQMXO)に直列に接続した、温度安定性に優れた $40\Omega$ の抵抗を駆動します。IMXO(QMXO)とIAIN(QAIN)の間に外付けフィルタを挿入している場合は、逆終端を計算するときにこの $40\Omega$ を考慮に入れてください。VCMOピンがバッファのDC出力レベルを設定します。これは外部から設定したり、1.0Vのオンチップ・リファレンスVREFに接続することができます。

#### 位相スプリッタ

2分周の周波数分周器を使用して、直交を発生させます。限られた周波数レンジで直交を作る多相フィルタとは異なり、2分周方式は広い周波数レンジで直交を維持し、LOを減衰させることもありません。ただし、ユーザーは、希望するLO周波数の2倍の周波数になる外部信号XLOを供給する必要があります。XLOは、周波数を1/2にする2つのフリップフロップのクロック入力を駆動します。2つのフリップフロップの出力は、XLOの1/2周期だけ位相がずれています。つまり、これらの出力は希望するLO周波数の1/4周期( $90^\circ$ )だけ位相がずれていることになります。出力での位相差がXLOでの遷移によって規定されるため、50%デューティ・サイクルからの偏差で直交位相誤差が生じます。

ユーザーが $1 \times$ 周波数  $(f_{REF})$  と周波数2倍回路  $(XLO=2 \times f_{REF})$  からXLOを生成する場合は、基本的に、 $f_{REF}$ とAD8348内部の直交LOとの間に $180^\circ$  の位相不確定性があります。しかし、I とOLOとの位相関係は常に $90^\circ$  になります。

#### I/Qベースバンド・アンプ

オフチップ・フィルタ処理後の復調信号を増幅するために、固定ゲイン(20dB)の2つのシングルエンド/差動アンプ(IとQ)があります。これらのアンプは電圧帰還を使用して、復調帯域幅でゲインを直線化します。アンプを使用すれば、AD8348の後に続くADCの入力でダイナミック・レンジを最大化できます。

ベースバンド・アンプIAIN(QAIN)への入力は、およそ  $50k\Omega$ の入力インピーダンスがあるバイポーラ・トランジスタ のベースに供給されます。ベースバンド・アンプは、IAIN (QAIN) とVCMOの間のシングルエンド差を感知します。IAIN(QAIN)をDCバイアスするには、IMXO(QMXO)とIAIN(QAIN)の間に外付けフィルタを挿入する場合のように、VCMOへのシャント抵抗によって終端します。あるいは、IMXO(QXMO)へのDC接続で、オフセット・ゼロ設定ループによって適切なバイアスを提供することもできます。

#### イネーブル

ENBLピンを使用してディスエーブルできるマスター・バイアス・セルが、チップのバイアスを制御します。ENBLピンがローレベルに保持されている場合、チップ全体が低消費電力のスリープ・モードにパワーダウンして、一般に5Vで $75\mu A$ の消費になります。

### ベースバンド・オフセット・キャンセル

低出力電流の積分器が、IOPP、IOPN(QOPP、QOPN)で出力電圧オフセットを感知し、信号パスにゼロ設定電流を発生させます。IOFS(QOFS)からVCMOへのコンデンサCOFSによって、オフセット・ゼロ設定ループの積分時定数を設定します。

この積分時定数を用いて、次式からベースバンド信号の高域側の-3dB応答周波数が得られます。

# $f_{PASS} = \frac{1}{2\pi \times 2650\Omega \times COFS}$

ユーザーは、D/Aコンバータやその他の電圧源でIOFS(QOFS)を駆動することによって、DCオフセットを外部から調整することもできます。この場合、ベースバンド回路がDC( $f_{PASS}$ = 0Hz)になるまで動作します。積分器の出力電流はわずか $50\mu$ Aで、外部電圧源で簡単に無効にできます。ベースバンド出力において0Vの差動オフセットを生成するためにIOFS(QOFS)に印可する公称電圧レベルは、900mVです。

帰還ループの発振を防止するには、IOFS(QOFS)ピンをバイパス・コンデンサ( $>0.1\mu F$ )または外部電圧源に接続する必要があります。

ミキサー出力とベースバンド・アンプ入力の間にAC結合されたベースバンド・フィルタが置かれている場合、帰還ループはDCにおいて終了します。AC結合されたフィルタが実装されている場合、ユーザーは何らかの外的手段によってオフセット補償を行う必要があります。

REV. 0 — 19 —

## アプリケーション

#### 基本的な接続

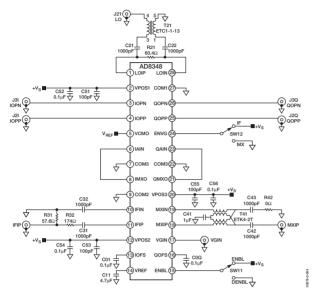

図49に、AD8348の基本的な接続回路図を示します。

図49. 基本的な接続回路図

#### 雷源

AD8348の電源電圧( $2.7 \sim 5V$ )を+VPOSxピンに供給し、グラウンドをCOMxピンに接続してください。コンデンサを2つ使用して、各電源ピンを個別にデカップリングしてください。コンデンサの推奨値は100pFと $0.1\mu$ Fです(これに近い値も使用できます)。

#### デバイス・イネーブル

デバイスをイネーブルにするには、ENBLピンを $+V_s$ に駆動します。ENBLピンを接地すると、デバイスはディスエーブルになります。

#### VGAイネーブル

ENVGピンの電圧を $+V_s$ に駆動すると、VGAがイネーブルになります。このモードでは、MX入力がディスエーブルになり、IF入力を使用することになります。ENVGピンを接地すると、VGAとIF入力がディスエーブルになります。VGAがディスエーブルの場合、MX入力を使用します。

#### ゲイン制御

VGAがイネーブルになると、VGINピンに印可された電圧によってゲインが設定されます。ゲイン制御の電圧範囲は $0.2 \sim 1.2V$ です。これは、 $+25.5 \sim -18.5 dB$ のゲイン・レンジに対応します。

#### LO入力

最適な性能を得るには、バランを通じて局部発振器のポートを差動で駆動してください。推奨バランは、M/A-COM ETC1-1-13です。AC結合されたトランスを使用する場合を除き、デバイスへのLO入力をAC結合してください。 $50\Omega$ ソースへの広帯域整合を得るには、LOIPピンとLIONピンの間に $60.4\Omega$ の抵抗を挿入してください。

図50. バラン付きの差動LO駆動

バランなしで、LOポートをシングルエンドで駆動することもできます(図51)。ACカップリング・コンデンサによって、LO信号を直接LOIPピンにAC結合します。LOINピンはグラウンドにAC結合します。LOポートをシングルエンドで駆動すると、直交位相誤差とLOリークの両方が増大します。

図51. シングルエンドのLO駆動

推奨するLO駆動レベルは $-12\sim 0dBm$ です。デバイスへの入力のLO周波数は、ミキサー・コアでの希望するLO周波数の2倍にしてください。使用するLO周波数の範囲は、 $100MHz\sim 2GHz$ です。

#### IF入力

IF入力には、 $200\Omega$ の入力インピーダンスがあります。損失が最小のLパッドを使用すれば、広帯域の $50\Omega$ 整合を実現できます。図42に、Lパッドがある場合とない場合のIF入力のS11を示します。

図52. 50ΩIF入力に対する最小損失のLパッド

#### MX 1 +

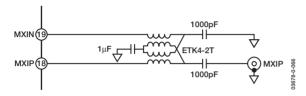

ミキサー入力MXIPとMXINには200Ωの公称インピーダンスがあり、差動で駆動する必要があります。差動ソースから駆動する場合は、図53に示すように、コンデンサを使って入力をソースにAC結合してください。

図53. MX入力の差動駆動

MX入力をシングルエンドの $50\Omega$ ソースから駆動する場合は、4:1のバランを使用すれば、必要なシングルエンド/差動変換を実行しながら、入力の $200\Omega$ インピーダンスを $50\Omega$ に変換できます。推奨トランスはM/A-COM ETK4-2Tです。

図54. シングルエンドの $50\Omega$ ソースからMX入力を駆動

#### ベースバンド出力

ベースバンド・アンプの出力IOPP、IOPN、QOPP、QOPNには、少なくとも $2k\Omega$ の負荷(グラウンドにシングルエンド接続)を与えてください。これらの出力は、直接 $50\Omega$ の負荷を駆動するように設計されていません。これらの出力の代表的な振幅は2Vp-p差動(1Vp-pシングルエンド)ですが、信号が出力振幅の限界内( $V_s$ -1Vと0.5V)に収まるように配慮すれば、大きな振幅も可能です。大きな振幅を得るには、ベースバンド出力信号のコモン・モード・バイアスを調整する必要があります。振幅を増大させると、ベースバンド・アンプ出力のS/N比が改善するというメリットがあります。

ベースバンド出力を他のデバイスに接続するときは、出力の容量性負荷が大きく(約20pF以上)ならないように注意してください。注意しないと、出力が過負荷になったり、発振を誘発する可能性があります。直列抵抗(約 $200\Omega$ )を挿入すれば、容量性負荷によるベースバンド・アンプ出力への影響を緩和することができます。

#### 出力のDCバイアス・レベル

ミキサー出力とベースバンド・アンプ入/出力のDCバイアスは、VCMOピンに駆動される電圧によって決まります。5V電源で動作するとき、この電圧の範囲は一般に500mV~4Vです。

ベースバンド・アンプから最大の電圧振幅を得るには、VCMO を2.25Vで駆動してください。これによって、7Vp-p差動 (3.5Vp-pシングルエンド) までのスイングが可能になります。

### AGC動作用の検出器へのインターフェース

AD8348は、AD8362 RMS/DCコンバータなどの検出器とインターフェースをとることで、ベースバンド出力用の自動信号レベル設定機能を提供できます。

図55. AGC動作用のAD8362の設定

IチャンネルとQチャンネルに同じRMS電力があるとすると、1つのチャンネルのミキサー出力(またはベースバンド・フィルタの出力)をAD8362の入力として使用できます。直線性誤差が小さい領域でAD8362を動作させてください。また、AD8362の入力の200 $\Omega$ 入力インピーダンスと直列に外付け抵抗を接続して分圧器を実装します。これによって、AD8348のミキサー出力を減衰して、AD8362の入力がオーバードライブされないようにします。ミキサー出力とAD8362入力の間の抵抗の大きさを選択するときは、AD8362の入力のピーク信号レベルがAD8362のダイナミック・レンジの最上部(約10dBmで発生)から約10dB下回るようにしてください。

AD8348のベースバンド出力の反対側には、AD8362の200Ω入力インピーダンスと直列で接続する減衰抵抗の直列抵抗に等しい抵抗を加えてください。この抵抗は、ミキサー出力からDC電流が生じないように、VCMOを駆動するソースに接続してください。

REV. 0 — 21 —

ミキサー出力(またはベースバンド・フィルタの出力)のレベルを設定するには、AD8362のピン11(VSET)に入力するセットポイント電圧を変化させます。

ブロッカ(所望の信号と共に復調される対象帯域内の不要信号)がAD8362の入力のRMS電力で優勢にならないように注意してください。ブロッカが支配的になると、ミキサー出力のレベルが不必要に低下します。これを解決するために、ベースバンド・フィルタ処理を実装して不要信号を取り除くことができます。フィルタの後でAD8362への信号を取得します。

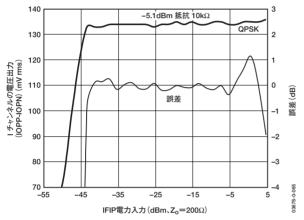

図56に、QPSK変調信号を380MHzで復調しながら、40dBのIF 入力レンジでベースバンド・アンプの出力振幅を0.5dB未満の誤差におさめた場合のAGCループの結果を示します。AD8362 にはクレスト・ファクタ変動の影響を受けないという長所があるため、着信信号の変調にかかわらず類似の性能が得られます。

図56. AD8362 AGCループによるIF入力電力 対 AD8348のベースバンド・アンプ出力

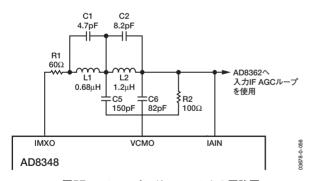

#### ベースバンド・フィルタ

ミキサー出力(IMXO/QMXO)とベースバンド・アンプへの 入力との間で、ベースバンドのローパス・フィルタ処理やバン ドパス・フィルタ処理を実行できます。ミキサーの出力イン ピーダンス( $40\Omega$ )に配慮してください。

図57. ベースバンド・フィルタの回路図

図57に、20MHzの3dBカットオフ周波数がある $100\Omega$ の4次楕円 ローパス・フィルタの回路図を示します。約 $100\Omega$ のソース・インピーダンスと負荷インピーダンスによって、フィルタのソースと負荷がマッチングします。これによって、ミキサー出力が $200\Omega$ の負荷全体を駆動することになります。なお、シャント終端抵抗はグラウンドではなく、VCMOを駆動するソースに接続します。これによって、ベースバンド・アンプへの入力が、適切なリファレンス・レベルまでバイアスされます。VCMOは出力ピンではなく、低インピーダンス・ソースによってバイアスする必要があります。

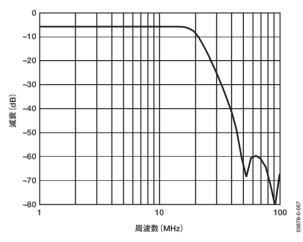

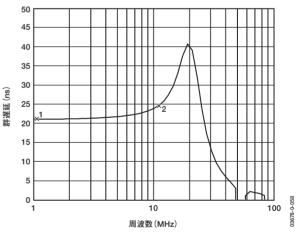

図58と図59に、このフィルタの周波数応答と群遅延を示します。

図58. ベースバンド・フィルタの応答

図59. ベースバンド・フィルタの群遅延

— 22 — REV. 0

#### LOの生成

アナログ・デバイセズが提供するPLLシリーズは、LO信号の 生成に使用できます。表4に、PLLとその最大周波数および位 相ノイズ性能を示します。

表4. アナログ・デバイセズのPLLセレクション・テーブル

| アナログ・<br>デバイセズのモデル                                                                                                                                                   | 周波数F <sub>IN</sub> (MHz)                                                        | @1KHz ΦN<br>dBc/Hz、200kHz PFD                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| ADF4001BRU<br>ADF4001BCP<br>ADF4110BRU<br>ADF4110BCP<br>ADF4111BRU<br>ADF4111BCP<br>ADF4112BRU<br>ADF4112BCP<br>ADF4116BRU<br>ADF4117BRU<br>ADF4117BRU<br>ADF4118BRU | 165<br>165<br>550<br>550<br>1200<br>1200<br>3000<br>3000<br>550<br>1200<br>3000 | -99<br>-99<br>-91<br>-91<br>-78<br>-78<br>-86<br>-86<br>-89<br>-87<br>-90 |

アナログ・デバイセズでは、シンセサイザとVCOをシングル・チップに完全統合したADF4360も提供しています。ADF4360は、AD8348の局部発振器入力を駆動するための差動出力を提供します。つまり、ユーザーはシングルエンド/差動変換に必要だったバランを使用せずに済むことになります。ADF4360は6つの動作周波数レンジを持つチップ・ファミリーの製品で、必要な局部発振器周波数に基づいて動作周波数レンジを選択できます。表5に、オプションを示します。

表5. ADF4360ファミリーの動作周波数

| アナログ・デバイセズのモデル                                                             | 出力周波数レンジ(MHz)                                                              |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------|

| ADF4360-1<br>ADF4360-2<br>ADF4360-3<br>ADF4360-4<br>ADF4360-5<br>ADF4360-6 | 2150/2450<br>1800/2150<br>1550/1950<br>1400/1800<br>1150/1400<br>1000/1250 |

| ADF4360-7                                                                  | 外付けLによって設定される<br>低周波数                                                      |

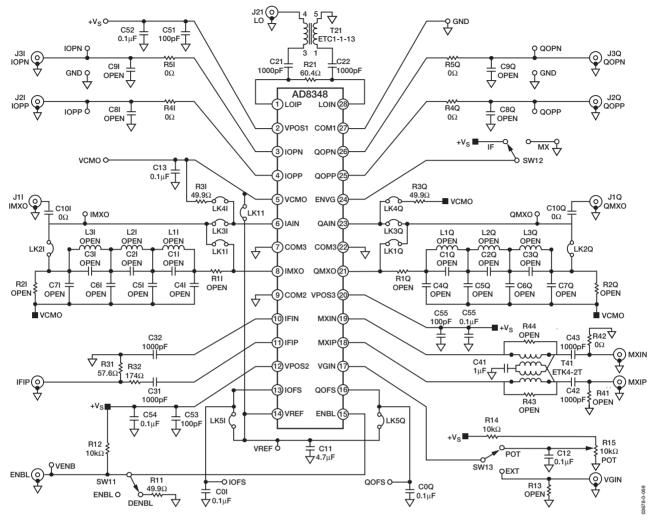

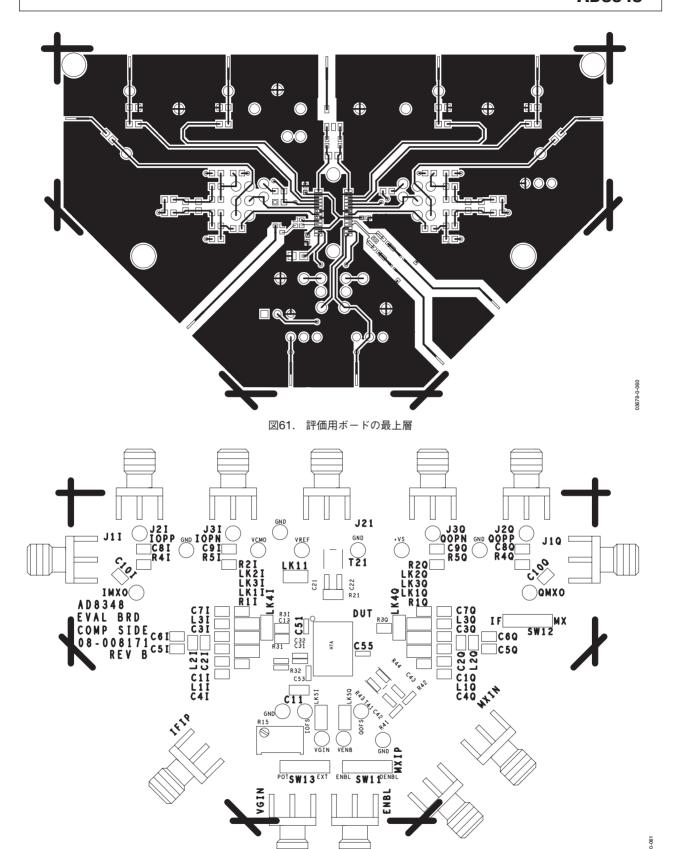

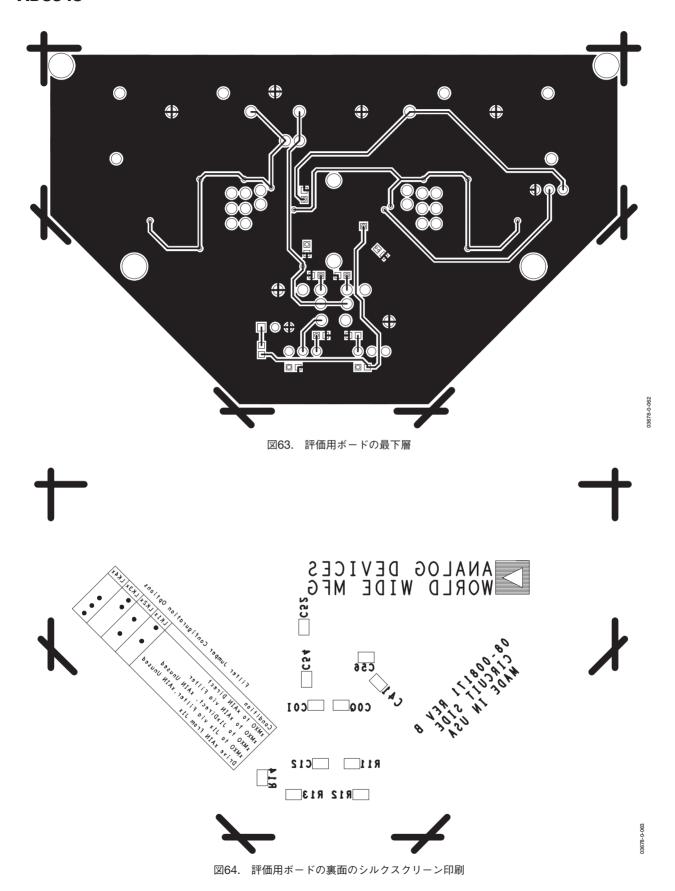

#### 評価用ボード

図60に、AD8348の評価用ボードの回路図を示します。未実装部品は「OPEN」としてあります。このボードは $2.7\sim5.5$ Vの範囲の単電源で動作します。表6に、評価用ボードのさまざまな設定オプションを示します。表7には、評価用ボードをさまざまな信号パスで動作させるためのジャンパ設定を示します。

ボードを動作させるための電力は、評価用ボードの最上部の LO入力ポートの近くにある単一の $+V_s$ テスト・ポイントに供給できます。リターン・パス用に、 $+V_s$ テスト・ポイントの横にGNDテスト・ポイントがあります。

デバイスをイネーブルにするには、スイッチSW11(評価用ボードの左下)をENBLの位置に設定します。デバイスをディスエーブルにするには、SW11をDENBLの位置に設定します。必要なら、ENBL SMAコネクタやVENBテスト・ポイントに接続可能な外部ソースからデバイスをイネーブル/ディスエーブルにできます。その場合、SW11をDENBLの位置に置いてください。

IF入力とMX入力は、SW12によって選択します。このスイッチは、希望する入力の方向に移動してください。

便宜上、DC電圧源を追加しなくてもゲインを変更できるようにポテンショメータR15が備わっています。このポテンショメータを使用するには、スイッチSW13をPOTの位置に設定する必要があります。テスト・ポイントまたはVGINというラベルの付いたSMAコネクタに外部電圧を印可することによって、ゲインを設定することもできます。外部のゲイン制御電圧を使用する場合には、SW13をEXTの位置に設定する必要があります。

局部発振器信号をSMAコネクタJ21に入力してください。このポートは $50\Omega$ で終端します。LO電力の入力レンジは $-12\sim 0$ dBmで、周波数はIF/MX周波数の2倍になります。

IF入力をSMAコネクタIFIPに接続してください。このポートを使用するとき、VGAをイネーブルにしておく必要があります(SW12がIFの位置)。

評価用ボードはデフォルトで、MXIP SMAコネクタに入力するシングルエンド信号源からバラン(T41)を通じて差動MX 駆動用に設定されています。差動駆動源に変更するには、T41 と抵抗R42を取り除いてください。T41の代わりに $0\Omega$ の抵抗R43とR44を取り付け、入力パターンのギャップを埋めます。これによって、 $200\Omega$ (両側に $100\Omega$ )の公称差動インピーダンスが発生します。次に、SMAコネクタMXIPとMXINに差動入力を接続してください。

ベースバンド出力は、IOPP、IOPN、QOPP、QOPNのテスト・ポイントとSMAコネクタから得られます。これらの出力は、 $50\Omega$ 負荷に直接接続するように設計されていません。約  $2k\Omega$ 以上の負荷を与えるようにしてください。

ベースバンド・アンプ出力のDCバイアス・レベルは、デフォルトでLK11を通じてVREFに接続されています。必要なら、LK11を取り除き、VCMOテスト・ポイントにDC電圧を駆動することによって、DCバイアス・レベルを変更できます。

図60. 評価用ボードの回路図

図62. 評価用ボードの表面のシルクスクリーン印刷

REV. 0 — 25 —

— 26 — REV. 0

### 表6. 評価用ボードの設定オプション

| 部品                                 | 機能                                                                                                                                                                                                                                     | デフォルト状態                                 |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| +V <sub>s</sub> , GND              | 電源とグラウンド・ベクター・ピン                                                                                                                                                                                                                       | 該当せず                                    |

| SW11, ENBL                         | デバイス・イネーブル: SW11をENBLの位置にすると、ENBLピンが $+V_s$ に接続されます。 SW11をDENBLの位置にすると、 $50\Omega$ のプルダウン抵抗を通じてENBLピンが接地されて、 デバイスがディスエーブルになります。ENBLやVENBに外部電圧を印可して、デバイスを イネーブルにすることもできます。                                                              | SW11=ENBL                               |

| SW13、R15、<br>VGIN                  | ゲイン制御選択:SW13がPOTの位置にあるとき、R15ポテンショメータを使用してVGAのゲインを設定できます。SW13がEXTの位置にあるとき、SMAコネクタVGINへの外部電圧によってVGAのゲインを設定できます。VGAを動作するには、まずSW12をIFの位置に設定し、VGAをイネーブルにする必要があります。                                                                          | SW2=POT                                 |

| SW12                               | $VGA$ イネーブル選択: $SW12$ が $IF$ の位置にあるとき、 $ENVG$ ピンが $+V_S$ に接続され、 $VGA$ がイネーブルになります。 $SW12$ が $IF$ の位置にあるときは、 $IF$ 入力を使用してください。 $SW12$ が $IF$ の位置にあるとき、 $ENVG$ ピンが接地され、 $VGA$ がディスエーブルになります。 $SW12$ が $IF$ 0位置にあるときは、 $IF$ 1人力を使用してください。 | SW12=IF                                 |

| IFIP, R31, R32                     | IF入力:このSMAコネクタにはシングルエンドIF信号を接続してください。R31とR32で<br>形成するLパッドが、入力に対する50Ωの終端になります。                                                                                                                                                          | $R31 = 57.6\Omega$<br>$R32 = 174\Omega$ |

| MXIP, MXIN                         | ミキサー入力:これらの入力は、差動動作またはシングルエンド動作に設定できます。                                                                                                                                                                                                | T41 = M/A-COM                           |

| T41、                               | 評価用ボードはデフォルトで、MXIP SMAコネクタに入力するシングルエンド信号源から                                                                                                                                                                                            | ETK4-2T                                 |

| R41, R42,                          | バラン (T41) を通じて差動MXドライブに設定されています。差動駆動源に変更するには、                                                                                                                                                                                          | R41、C42、                                |

| C42、C43                            | $ T41$ と抵抗 $R42$ を取り除きます。 $T41$ の代わりに $\Omega$ の抵抗 $R43$ と $R44$ を取り付け、入力パターン                                                                                                                                                          | C43=OPEN                                |

|                                    | のギャップを埋めてください。これによって、 $200\Omega$ (両側に $100\Omega$ )の公称差動インピーダンスが発生します。次に、SMAコネクタMXIPとMXINに差動入力を接続してください。                                                                                                                              | $R42=0\Omega$                           |

| LK11, VCMO                         | ベースバンド・アンプの出力バイアス:LK11を取り付けると、VREFがVCMOに接続されます。これによって、ベースバンド・アンプでのバイアス・レベルがVREF(約1V)に設定されます。LK11を取り除き、VCMOテスト・ポイントに外部電圧を印加することによって、ベースバンド・アンプのバイアス・レベルを設定することもできます。                                                                    | LK11取り付け済み                              |

| C8、C9、R4、<br>R5(IおよびQ)             | ベースバンド・アンプの出力と出力フィルタ:これらのフィルタによって、ベースバンド<br>出力にローパス・フィルタ処理を追加できます。                                                                                                                                                                     | R4, R5= $0\Omega$                       |

| C10(IおよびQ)                         |                                                                                                                                                                                                                                        | C10=0Ω                                  |

| C1~C7<br>R1、R2<br>L1~L3<br>(IおよびQ) | ベースバンド・フィルタ: ミキサー出力とベースバンド・アンプ入力の間でベースバンド・フィルタ処理を行うための部品です。ベースバンド・アンプの入力インピーダンスはハイレベルで、フィルタ終端インピーダンスはR2で設定されます。ジャンパ設定については、表7を参照してください。                                                                                                | すべて=OPEN                                |

| LK5(IおよびQ)                         | オフセット補償ループのディスエーブル:これらのジャンパを取り付けると、対応するチャン<br>ネルのオフセット補償ループがディスエーブルになります。                                                                                                                                                              | LK5x=OPEN                               |

### 表7. フィルタのジャンパ設定オプション

| 条件                                                                     | LK1x | LK2x | LK3x | LK4x |

|------------------------------------------------------------------------|------|------|------|------|

| xMXO~xAIN(直接)<br>xMXO~xAIN(フィルタ経由)                                     | •    | •    | •    |      |

| xMXO〜J1x (直接)、xAINは使用せず<br>xMXO〜J1x (フィルタ経由)、xAINは使用せず<br>J1xからxAINを駆動 | •    | •    |      | •    |

REV. 0 — 27 —

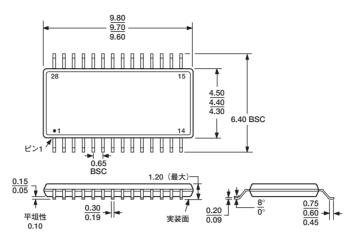

## 外形寸法

JEDEC規格MO-153AEに準拠

図65. 28ピン薄型シュリンク・スモール・アウトライン・パッケージ [TSSOP] (RU-28)

単位:mm

#### 注意

ESD(静電放電)の影響を受けやすいデバイスです。人体や試験機器には4000Vもの高圧の静電気が容易に蓄積され、検知されないまま放電されることがあります。本製品は当社独自のESD保護回路を内蔵してはいますが、デバイスが高エネルギーの静電放電を被った場合、回復不能の損傷を生じる可能性があります。したがって、性能劣化や機能低下を防止するため、ESDに対する適切な予防措置を講じることをお勧めします。

### オーダー・ガイド

| AD8348製品                       | 温度範囲     | パッケージ                                      | パッケージ・オプション |

|--------------------------------|----------|--------------------------------------------|-------------|

| AD8348ARU                      | -40~+85℃ | 薄型シュリンク・スモール・アウトライン・                       | RU-28       |

| AD8348ARU-REEL7<br>AD8348-EVAL | -40~+85℃ | パッケージ(28ピンTSSOP)<br>7インチのテープ&リール<br>評価用ボード | RU-28       |

REV. 0 — 29 —

C03678-0-8/03(0)

PRINTED IN JAPAN

— 30 — REV. 0