# Evaluation Board for Filterless Class-D Audio Amplifier

# EVAL-SSM2311

#### FEATURES

Single-ended and differential input capability Multiple input interface connection options (jack or header) Optimized EMI suppression filter assembled on board PCB footprint for dc power supply jack (accepts 2.5 V to 5.5 V)

#### **GENERAL DESCRIPTION**

The SSM2311 is a fully integrated, single-chip, mono Class-D audio amplifier. It is designed to maximize performance for mobile phone applications. The application circuit requires a minimum of external components and operates from a single 2.5 V to 5.5 V supply. It is capable of delivering 3 W of continuous output power with less than 1% THD + N driving an 3  $\Omega$  load from a single 5.0 V supply.

The SSM2311 comes with a differential mode input port and a high efficiency H-bridge at the output. When compared to a halfbridge output stage, a full H-bridge enables direct coupling of the audio power signal to the loudspeaker, doubling the output voltage swing and eliminating the need for a large output coupling capacitor. Another benefit of a full H-bridge is an increase of the maximum output power by 4× when compared to a half bridge under the same load impedance. These benefits are particularly useful for low voltage, battery-powered portable electronics where energy and space are limited. The differential mode input stage

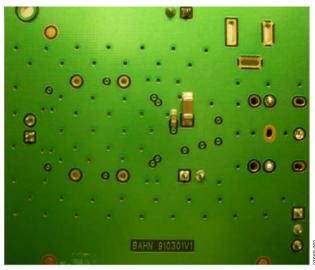

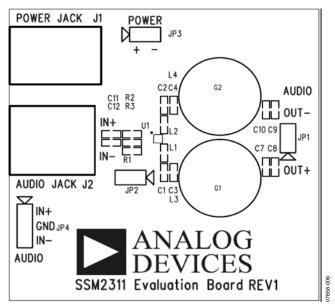

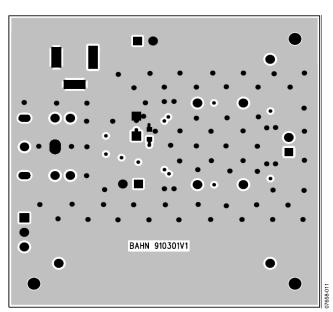

Figure 1. SSM2311 Evaluation Board Top View

#### Rev. 0

Evaluation boards are only intended for device evaluation and not for production purposes. Evaluation boards are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability or fitness for a particular purpose. No license is granted by implication or otherwise under any patents or other intellectual property by application or use of evaluation boards. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Analog Devices reserves the right to change devices or specifications at any time without notice. Trademarks and registered trademarks are the property of their respective owners. Evaluation boards are not authorized to be used in life support devices or systems. allows for cancelling of common-mode noise leading to a superior CMRR.

Moreover, the part features a high efficiency, low noise output modulation scheme that does not require external LC output filters when attached to an inductive load. The modulation provides high efficiency even at low output power. Filterless operation also helps to decrease distortion due to nonlinearities of output LC filters, thereby providing a better sound quality and leading to savings in board space and overall cost.

This data sheet describes how to configure and use the SSM2311 evaluation board. It is recommended that this data sheet be read in conjunction with the SSM2311 data sheet, which provides more detailed information about the specifications, internal block diagrams, and application guidance for the amplifier IC.

#### **EVALUATION BOARD DESCRIPTION**

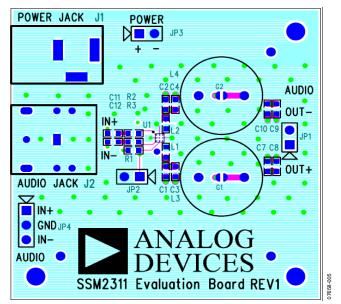

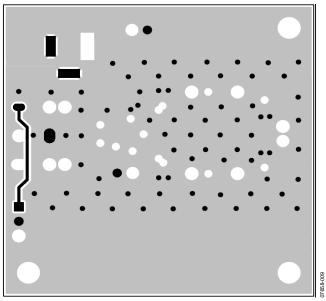

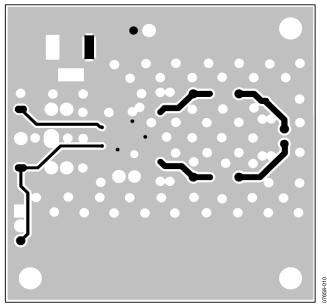

The SSM2311 evaluation board carries a complete application circuit for driving a loudspeaker. Figure 1 shows the top view of the evaluation board and Figure 2 shows the bottom view. The top layer with its silkscreen of the evaluation board is shown in Figure 5. Figure 6 and Figure 7 show the top silkscreen and bottom silkscreen, respectively. The top layer, Layer 2 (ground plane), Layer 3 (power plane), and bottom layer are shown in Figure 8, Figure 9, Figure 10, and Figure 11, respectively.

Figure 2. SSM2311 Evaluation Board Bottom View

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2008 Analog Devices, Inc. All rights reserved.

### TABLE OF CONTENTS

| Features                     | 1 |

|------------------------------|---|

| General Description          | 1 |

| Evaluation Board Description | 1 |

| Revision History             | 2 |

| Evaluation Board Hardware    | 3 |

| Power Supply                 | 3 |

| Headers                      | 3 |

| Getting Started              | 3 |

| What to Test                           | 3 |

|----------------------------------------|---|

| Component Selections                   | 3 |

| PCB Layout Guidelines                  | 5 |

| Evaluation Board Schematic and Artwork | 6 |

| Ordering Information                   | 9 |

| Bill of Materials                      | 9 |

| Ordering Guide                         | 9 |

| ESD Caution                            | 9 |

### **REVISION HISTORY**

9/08—Revision 0: Initial Version

### EVALUATION BOARD HARDWARE POWER SUPPLY

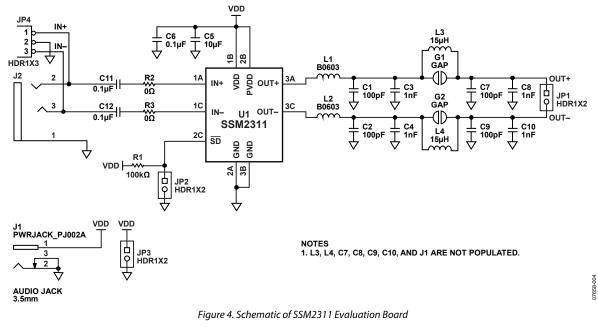

The schematic is shown in Figure 4.

On the upper left corner, there is a PCB footprint to populate a standard power jack (J1), which accepts a 2.5 V ~ 5.5 V dc power supply. The user can also use the two-pin header (JP3) to power the board. In either case, care must be taken to connect the dc power with correct polarity and voltage. The J1 jack is not populated during PCB assembly.

#### Warning

The wrong power supply polarity or overvoltage may damage the board permanently

The maximum peak current is approximately 0.33 A when driving an 8  $\Omega$  load and when the input voltage is 5 V.

### HEADERS

On the left side and below the power jack, there is a standard 3.5 mm audio stereo jack connector (J2). Below J2 is a three-pin header (JP4). These are used to feed the audio signal into the board.

If the input audio signal is differential (IN+ and IN–), the user can use either J2 or JP4. In this case, all three pins of J2 or JP4 are used for IN+, IN–, and the ground.

For a single-ended audio input, using JP4 as the input connector is recommended. In this case, only two pins of JP4 are used. One is for the ground and the other is for either IN+ or IN-. If IN+ is used, the user should place a jumper between Pin 2 and Pin 3 of JP4, shorting IN- to ground. If IN- is used, the jumper should be placed between Pin 1 and Pin 2 of JP4, connecting IN+ to the ground.

The two-pin header, JP2, is used to turn on/off the SSM2311 amplifier. Putting a jumper on JP2 shuts down the SSM2311 so that only a minimum current (about 20 nA) is drawn from the power supply. Removing the jumper puts the SSM2311 in normal operation.

The output connector, JP1, is located on the right side of the board. JP1 drives a loudspeaker whose impedance should be no less than 3  $\Omega$ .

While the SSM2311 does not require any external LC output filters due to a low noise modulation scheme, if the speaker length is >10 cm, it is recommended to put a ferrite bead (L1 and L2) near each output pin of the SSM2311 to reduce electromagnetic interference (EMI), as shown in the schematic in Figure 4. On the board, there are two inductors, L3 and L4, that are not loaded and not required for normal operation (they are shorted by the solder gaps, G1 and G2), but some users may add these inductors to evaluate their certain applications with tighter EMI constraints. If L3 and L4 are loaded, the solder on G1 and G2 must be removed by a soldering iron. As a courtesy to the end user, a properly tuned ferrite bead based EMI filter is assembled at the output terminals of the device. For optimal performance, as specified in the SSM2311 data sheet (in particular THD and SNR), the entire EMI filter should be removed. Short across the ferrite bead terminals and open the capacitor terminals.

### **GETTING STARTED**

To ensure proper operation, carefully follow Step 1 through Step 4.

- 1. If a jumper is on JP2, remove the jumper to turn on the amplifier.

- 2. Connect the load to the audio output connector, JP1.

- 3. Connect the audio input to the board, either in differential mode or single-ended mode, depending on the application.

- 4. Connect the power supply with the proper polarity and voltage.

### WHAT TO TEST

- EMI. Connect wires for the speakers of the same length as for the actual application environment and complete the EMI test.

- Signal-to-noise ratio.

- Output noise. Make sure to use an A-weighted filter to filter the output before reading the measurement meter.

- Maximum output power.

- Distortion.

- Efficiency.

### **COMPONENT SELECTION**

Selecting the proper components is the key to achieving the performance required at the cost budgeted.

#### Input Coupling Capacitor Selection—C11 and C12

These capacitors, C11 and C12, should be large enough to couple the low frequency signal components in the incoming signal and should be small enough to filter out unnecessary low frequency signals. For music signals, the cutoff frequency chosen is often between 20 Hz to 30 Hz. The value of the input capacitor is calculated by

$C=1/(2\pi Rf_c)$

where:  $R = 150 \text{ k}\Omega$ .  $f_c$  is the cutoff frequency.

#### Output Ferrite Beads—L1 and L2

The output beads, L1 and L2, are necessary components for filtering out the EMI caused at the switching output nodes when the length of the speaker wire is greater than 10 cm. The penalty for using ferrite beads for EMI filtering is slightly worse noise and distortion performance at the system level due to the nonlinearity of the beads.

Ensure that these beads have enough current conducting capability while providing sufficient EMI attenuation. The current rating needed for an 8  $\Omega$  load is approximately 420 mA, and impedance at 100 MHz must be  $\geq$ 220  $\Omega$ . In addition, the lower the dc resis-

tance (DCR) of these beads, the better for minimizing their power consumption. Table 1 describes the recommended bead.

#### **Output Shunting Capacitors**

There are two groups of output shunting capacitors: C1, C2, C3, and C4 work with the ferrite beads, L1 and L2; C7, C8, C9, and C10 work with L3 and L4 if they are used. Use small size (0603 or 0402) multilayer ceramic capacitors that are made of X7R or COG (NPO) materials. Note that the capacitors are used in pairs: a capacitor with small capacitance (up to 100 pF) plus a capacitor with a bigger capacitance (1 nF). This configuration provides better EMI reduction for the entire frequency spectrum.

#### Output Inductors—L3 and L4

Some users do not allow high frequency EMIs in the system and prefer using inductors to filter out the high frequency components at the output nodes. Choose inductance that is >2.2  $\mu$ H for these inductors. The higher the inductance, the lower the EMI is at the output. However, the cost and power consumption by the inductors are higher. Using 2.2  $\mu$ H to 10  $\mu$ H inductors is recommended and the current rating needs >600mA (saturation current) for an 8  $\Omega$  load. Table 2 shows the recommended inductors. Note that these inductors are not populated on the evaluation board.

#### Table 1. Recommended Output Bead

| Part No.       | Manufacturer | Ζ (Ω) | I <sub>MAX</sub> (mA) | DCR (Ω) | Size (mm)               |

|----------------|--------------|-------|-----------------------|---------|-------------------------|

| 445-1565-2-ND  | TDK          | 220   | 2000                  | 0.05    | 1.6 	imes 0.8 	imes 0.8 |

| BLM18EG221SN1D | Murata       | 220   | 2000                  | 0.05    | 1.6 	imes 0.8 	imes 0.8 |

#### Table 2. Recommended Output Inductors

| Part No.      | Manufacturer    | L (µH) | I <sub>MAX</sub> (mA) | DCR (Ω) | Size (mm)                    |

|---------------|-----------------|--------|-----------------------|---------|------------------------------|

| LQH32CN4R7M53 | Murata          | 4.7    | 650                   | 0.15    | 3.2 × 2.5 × 1.55             |

| LQH32CN3R3M53 | Murata          | 3.3    | 710                   | 0.12    | $3.2 \times 2.5 \times 1.55$ |

| LQH32CN2R2M53 | Murata          | 2.2    | 790                   | 0.1     | 3.2 × 2.5 × 1.55             |

| SD3118-100-R  | Cooper Bussmann | 10     | 900                   | 0.3     | 3.1 × 3.1 × 1.8              |

| ELL4LM100M    | Panasonic       | 10     | 690                   | 0.18    | 3.8 × 3.8 × 1.8              |

| LBC2518T2R2M  | Taiyo Yuden     | 2.2    | 630                   | 0.13    | 2.5 	imes 1.8 	imes 2        |

| 1033AS-4R7M   | Toko            | 4.7    | 680                   | 0.31    | 3.8 × 3.8 × 1                |

#### PCB LAYOUT GUIDELINES

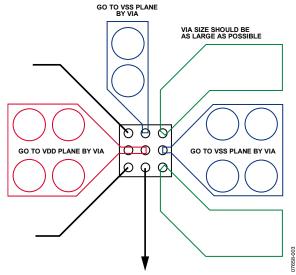

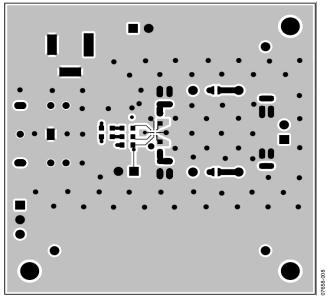

To keep the EMI under the allowable limit and to ensure that the amplifier chip operates under the temperature limit, PCB layout is critical in application designs. Figure 3 shows the preferred layout for the SSM2311.

Figure 3. Preferred PCB Layout for SSM2311

#### Layer Stacks and Grounding

The stack-up for the evaluation board is a 4-layer structure.

- Top layer—component layer with power and output copper land and ground copper pouring.

- 2<sup>nd</sup> layer—dedicated ground plane.

- 3<sup>rd</sup> layer—dedicated power plane.

- Bottom layer—bottom layer with ground copper pouring.

#### **Components Placement and Clearance**

Place all related components except decoupling capacitors on the same side as the SSM2311 and as close as possible to the chip to avoid vias (see Figure 5).

Place decoupling capacitors on the bottom side and close to the GND pin (see Figure 7).

#### Top Layer Copper Land and Ground Pouring

The output peak current of this amplifier is more than 1 A, so PCB traces should be wide (>2 mm) to handle the high current. For the best performance, use symmetrical copper lands as large as space allows, instead of traces for the output pins (see Figure 3).

Pour ground copper on the top side and use many vias to connect the top layer ground copper to the dedicated ground plane. The copper pouring on the top layer serves as both the EMI shielding ground plane and the heat sink for the SSM2311.

The SSM2311 works well only if these techniques are implemented in the PCB design to keep EMI and the amplifier temperature low.

### **EVALUATION BOARD SCHEMATIC AND ARTWORK**

Figure 5. Top Layer with Top Silkscreen

Figure 6. Top Silkscreen

Figure 7. Bottom Silkscreen

Figure 8. Top Layer

Figure 9. Layer 2 (Ground Plane)

Figure 11. Bottom Layer

Figure 10. Layer 3 (Power Plane)

### **ORDERING INFORMATION**

### **BILL OF MATERIALS**

#### Table 3.

| Qty | Reference Designator | Description                          | Supplier/Part No.        |

|-----|----------------------|--------------------------------------|--------------------------|

| 4   | C1, C2, C7, C9       | 100 pF capacitor, 10%, 50 V          | Digi-Key 478-3717-1-ND   |

| 4   | C3, C4, C8, C10      | 1 nF capacitor, 50 V                 | Digi-Key 399-3293-1-ND   |

| 1   | C5                   | 10 μF capacitor, 10 V                | Digi-Key 90-1843-1-ND    |

| 3   | C6, C11, C12         | 0.1 μF capacitor, 16 V               | Digi-Key 399-1096-1-ND   |

| 3   | JP1, JP2, JP3        | HDR1X2, connector header, 2-position | Digi-Key A26508-02-ND    |

| 1   | JP4                  | HDR1X3, connector header, 3-position | Digi-Key A26508-03-ND    |

| 1   | J1                   | PWRJACK_PJ002A, connector            | Digi-Key CP1-021-ND      |

| 1   | J2                   | Audio jack, 3.5 mm, 3-pin            | Digi-Key CP1-3523N-ND    |

| 2   | L1, L2               | B0603, ferrite chip, 220 Ω, 2 A      | Digi-Key 445-1565-2-ND   |

| 2   | L3, L4               | 15 μH                                | Not populated            |

| 1   | R1                   | 100 kΩ resistor, 1/10 W, 1%          | Digi-Key 311-100KHRCT-ND |

| 2   | R2, R3               | 0 Ω resistor, 1/10 W, 5%             | Digi-Key 311-0.0GRCT-ND  |

| 1   | U1                   | SSM2311                              | Analog Devices SSM2311   |

#### **ORDERING GUIDE**

| Model                      | Description      |

|----------------------------|------------------|

| SSM2311-EVALZ <sup>1</sup> | Evaluation Board |

$^{1}$  Z = RoHS Compliant Part.

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### NOTES

### NOTES

### NOTES

©2008 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. EB07658-0-9/08(0)

www.analog.com

Rev. 0 | Page 12 of 12