# IEEE 802.3bt PD with Telemetry and Power Priority

### **FEATURES**

- IEEE 802.3bt Powered Device (PD) Controller

- ▶ 400kHz I<sup>2</sup>C Interface

- ► Continuous Voltage, Current, and Power Telemetry

- Dedicated 14-Bit Delta-Sigma Current and Voltage ADCs

- Automatic Maintain Power Signature (MPS)

- ▶ Supports Up to 90W PDs with Extended Power

- 5-Event Classification Sensing with PSE Allocated Power Readback

- Seamless Switchover between Dual PD or PD/AUX Inputs

- Superior Surge Robustness (100V Absolute Maximum)

- ▶ Wide Junction Temperature Range (-40°C to 125°C)

- External Hot Swap N-Channel MOSFET for Lowest Power Dissipation and Highest System Efficiency

- 50mΩ Current Sense Resistor

- Auxiliary Input Sense with Standby Modes

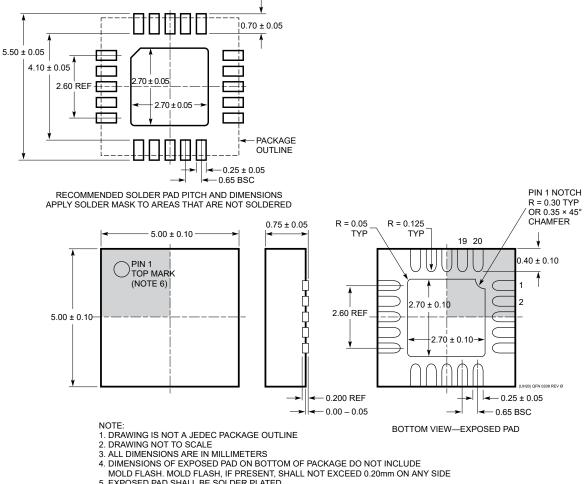

- > 20-Pin 5mm x 5mm QFN Package

## **APPLICATIONS**

- ▶ IEEE 802.3bt PDs with Power Telemetry

- ▶ Wireless Access Points/Pico Cells

- Internet Protocol (IP) Security Cameras

- Power over Ethernet (PoE) Lighting

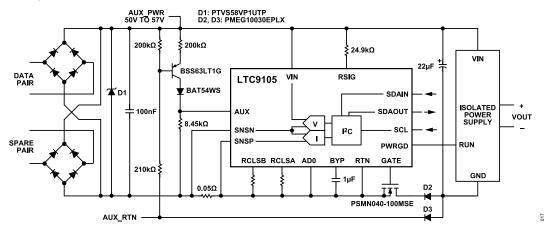

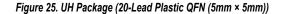

## **TYPICAL APPLICATION**

## DESCRIPTION

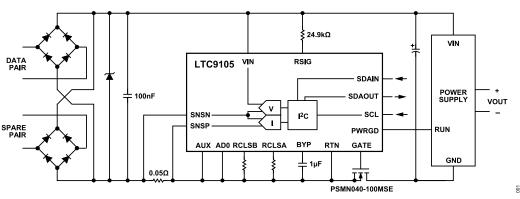

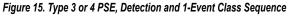

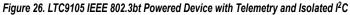

The LTC9105 is an IEEE 802.3af/at/bt ("PoE 2") Power over Ethernet (PoE) powered device (PD) controller with input current, voltage, and power telemetry. The LTC9105 includes an I<sup>2</sup>C interface to read telemetry, power sourcing equipment (PSE) allocated power, and auxiliary input status, and to write power input priority. The LTC9105 also features a configurable downstream power-up disable with under-power indication when the PSE allocated power is less than the PD requested power.

The LTC9105 utilizes an external, low  $R_{DS(ON)}$ , N-Channel, Hot Swap MOSFET, and a 50m $\Omega$  current sense resistor, and supports the LT4321 ideal bridge to extend the end-to-end power delivery efficiency. Also included are a power good output, external signature resistor, resistor programmable classification and pin-configurable PD requested Class. The presence of an auxiliary power supply is sensed at the AUX pin and reported through the  $I^2C$  interface. Automatic maintain power signature (MPS) circuitry keeps the PD interface powered when downstream current draw falls below an internal MPS threshold.

Two dedicated Delta-Sigma ADCs continuously measure PD controller input voltage and current with a typical conversion time of 100ms and with 14-bit resolution. Simultaneous conversion of current and voltage measurements enables high-accuracy power calculations.

Figure 1. LTC9105 IEEE 802.3bt Powered Device with Telemetry and I<sup>2</sup>C

19-101904; Rev A; 2/25

DOCUMENT FEEDBACK

TECHNICAL SUPPORT

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.All Analog Devices products contained herein are subject to release and availability.

## TABLE OF CONTENTS

| Features                            | 1  |

|-------------------------------------|----|

| Applications                        | 1  |

| Description                         | 1  |

| Typical Application                 | 1  |

| Absolute Maximum Ratings            | 3  |

| ESD Caution                         | 3  |

| Thermal Resistance                  | 3  |

| Order Information                   | 4  |

| Electrical Characteristics          | 5  |

| Pin Configuration and Function      | 7  |

| Typical Performance Characteristics | 8  |

| Theory of Operation                 | 10 |

|                                     |    |

| Auxiliary Input                    | 11 |

|------------------------------------|----|

| Dual-Input Prioritization          | 13 |

| Automatic Maintain Power Signature | 14 |

| Analog-to-Digital Converters (ADC) | 14 |

| I <sup>2</sup> C Interface         | 15 |

| Register Map                       | 17 |

| Applications Information           |    |

| External Component Selection       | 19 |

| Layout Considerations              | 19 |

| Outline Dimensions                 | 21 |

| Typical Application                | 22 |

| Related Parts                      | 22 |

|                                    |    |

## **REVISION HISTORY**

| 2/2025—Rev. 0 to Rev. A: Initial public release |     |

|-------------------------------------------------|-----|

| Changes to Features Section                     | . 1 |

| Changes to Applications Section                 | . 1 |

| Changes to Dual-Input Prioritization Section    | 13  |

|                                                 |     |

## 6/2024—Revision 0: Initial release

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 1. Absolute Maximum Ratings

| Parameter                                                    | Rating        |

|--------------------------------------------------------------|---------------|

| VIN, RSIG, SDAOUT, SDAIN, SCL, AD0, PWRGD,<br>SDAIN Voltages | -0.3V to 100V |

| RCLSA, RCLSB Voltages                                        | -0.3V to 2V   |

| RCLSA, RCLSB Current                                         | -50mA         |

| GATE, SNSP Voltages                                          | -0.3V to 80V  |

| AUX, BYP, M1, M0 Voltage                                     | -0.3V to 5.5V |

| SNSN Voltage                                                 | -2V to 0.3V   |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability. Absolute Maximum Voltages are specified with respect to RTN (pins 7, 19, and exposed pad 21) connected together.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.

#### Table 2. Thermal Resistance

| Package Type <sup>1</sup> | θ <sub>JA</sub> <sup>2</sup> | θ <sub>JC</sub> <sup>3</sup> | Unit |

|---------------------------|------------------------------|------------------------------|------|

| UH-20-1                   | 34                           | 3                            | °C/W |

<sup>1</sup> Test Condition 1: thermal impedance simulated values are based upon use of 2S2P JEDEC PCB. See the Order Information.

- $^2~\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.

- $^3~\theta_{JC}$  is the junction-to-case thermal resistance.

## **ORDER INFORMATION**

#### Table 3.

| LEAD FREE FINISH                                                                                                                                                                | TAPE AND REEL | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|---------------------------------|-------------------|--|

| LTC9105ATP+                                                                                                                                                                     | LTC9105ATP+T  | 9105         | 20-Lead (5mm × 5mm) Plastic QFN | -40°C to 125°C    |  |

| Contact the factory for parts specified with wider operating temperature ranges. Tape and reel specifications. Some packages are available in 500 unit reels through designated |               |              |                                 |                   |  |

sales channels with #TRMPBF suffix.

## **ELECTRICAL CHARACTERISTICS**

The \* denotes the specifications that apply over the full operating temperature range. Otherwise, specifications are at  $T_A = 25^{\circ}$ C. VIN – RTN = 55V, unless otherwise noted.

| SYMBOL              | PARAMETER                               | CONDITIONS                                                                                           |   | MIN       | TYP   | MAX   | UNITS    |

|---------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------|---|-----------|-------|-------|----------|

|                     | VIN Operating Input Voltage             | VIN-RTN                                                                                              | * |           |       | 60    | V        |

| OFFSET              | Input Offset Current                    | VIN-RTN in range of V <sub>SIG</sub>                                                                 | * |           |       | 10    | μA       |

| / <sub>SIG</sub>    | VIN Signature Range                     | VIN-RTN                                                                                              | * | 1.5       |       | 10    | V        |

| / <sub>CLASS</sub>  | VIN Classification Range                | VIN-RTN                                                                                              | * | 12.5      |       | 21    | V        |

| / <sub>MARK</sub>   | VIN Mark Range                          | VIN-RTN                                                                                              | * | 5.6       |       | 10    | V        |

|                     | Class/Mark Hysteresis                   | VIN-RTN                                                                                              |   |           | 1.2   |       | V        |

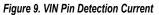

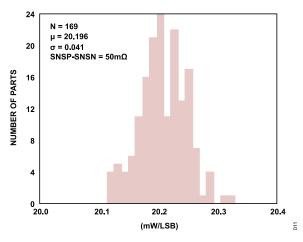

| / <sub>ON</sub>     | VIN Gate Turn On                        | VIN-RTN                                                                                              | * | 33        |       | 37    | V        |

| / <sub>OFF</sub>    | VIN Gate Turn Off                       | VIN-RTN                                                                                              | * | 30        |       |       | V        |

| -                   | Hot Swap On/Off Hysteresis              | VIN-RTN                                                                                              |   |           | 3.3   |       | V        |

| / <sub>RESET</sub>  | Reset Threshold                         | VIN-RTN, Preceded by V <sub>CLASS</sub>                                                              | * | 2.6       |       | 5.6   | V        |

| V <sub>BYP</sub>    | Bypass Pin Voltage                      | VIN > V <sub>ON</sub>                                                                                |   |           | 4.3   |       | V        |

| Supply Curr         | ent                                     |                                                                                                      |   |           |       |       |          |

|                     | Supply Current                          | VIN > V <sub>ON</sub>                                                                                | * |           | 2.2   | 3.0   | mA       |

|                     | Supply Current During Classification    | VIN = 17.5V, RCLSA and RCLSB open                                                                    | * | 330       |       | 600   | μA       |

|                     | Supply Current During Mark Event        | VIN = V <sub>MARK</sub> After 1st Classification Event                                               | * | 0.85      |       | 1.6   | mA       |

| Detection an        | d Classification Signature              |                                                                                                      |   |           |       |       |          |

|                     | RSIG Pin Resistance                     | VIN = V <sub>SIG</sub> , I <sub>RSIG</sub> = 1mA                                                     | * |           |       | 270   | Ω        |

|                     | Resistance During Mark Event            | R <sub>VIN-RTN</sub> , VIN = V <sub>MARK</sub> After 1st Classification Event                        | * |           | 8     | 12    | kΩ       |

|                     | RCLSA, RCLSB Operating Voltage          | $-1\text{mA} \ge I_{\text{RCLSA}}, I_{\text{RCLSB}} \le -44\text{mA}, \text{VIN} = V_{\text{CLASS}}$ | * | 0.95<br>3 | 0.983 | 1.013 | V        |

|                     | Classification Signature Stability Time |                                                                                                      | * | 0.25      |       | 2     | ms       |

| Gate Driver         |                                         |                                                                                                      |   |           |       |       |          |

|                     | Active Current Limit During Inrush      | SNSP-SNSN, VIN > V <sub>ON</sub> , t <sub>ON</sub> < t <sub>PWRGD</sub>                              |   |           | 5     |       | mV       |

|                     | GATE Pin On Voltage                     | GATE-RTN, I <sub>GATE</sub> = 1µA                                                                    | * | 11        | 12    | 14    | V        |

|                     | GATE Pin Pull Down Current              | VIN < V <sub>OFF</sub> , GATE-RTN = 1V                                                               | * |           |       | 0.5   | mA       |

| Auxiliary Su        | pply Input Sense                        |                                                                                                      |   |           |       |       |          |

| V <sub>AUX</sub> th | Auxiliary Pin Threshold                 | AUX-RTN, VIN > V <sub>ON</sub> , aux_thresh = 0                                                      | * | 1.0       | 1.05  | 1.1   | V        |

| Digital Input       | Output                                  |                                                                                                      |   |           |       |       | <u> </u> |

| V <sub>IH</sub>     | Digital Input High Voltage              | AD0, M1, M0                                                                                          | * | 2.5       |       |       | V        |

|                     |                                         | SCL, SDAIN                                                                                           | * | 2.2       |       |       | V        |

| V <sub>IL</sub>     | Digital Input Low Voltage               | AD0, M1, M0                                                                                          | * |           |       | 1.9   | V        |

|                     |                                         | SCL, SDAIN                                                                                           | * |           |       | 1.7   | V        |

|                     | SDAOUT Pin Output Low Voltage           | I <sub>SDAOUT</sub> = 3mA                                                                            | * |           |       | 0.4   | V        |

|                     |                                         | I <sub>SDAOUT</sub> = 5mA                                                                            | * |           |       | 0.7   | V        |

|                     | Internal Pull-Down to RTN               | AD0, M1, M0                                                                                          |   |           | 50    |       | kΩ       |

|                     | Internal Pull-Up to BYP                 | SCL, SDAIN                                                                                           |   |           | 50    |       | kΩ       |

| Power Good          | · ·                                     |                                                                                                      |   |           |       |       |          |

| PWRGD               | PWRGD Delay Timer                       | From V <sub>ON</sub> Threshold to PWRGD HI-Z (Note 1)                                                |   |           | 93.75 |       | ms       |

| PWRGD               | PWRGD Current During t <sub>PWRGD</sub> | PWRGD = 1V, VIN > V <sub>ON</sub> , t <sub>ON</sub> < t <sub>PWRGD</sub>                             | * | 195       | 250   | 305   | μA       |

|                     | ver Signature                           |                                                                                                      |   | 1         | 1     |       | · · · ·  |

|                     | DC Integration Time                     |                                                                                                      |   |           | 100   |       | ms       |

|                     | MPS Pulse Time                          |                                                                                                      |   |           | 100   |       | ms       |

|                     | MPS Backoff time                        |                                                                                                      |   |           | 200   |       | ms       |

|                     | DC MPS Threshold                        | SNSP-SNSN (Note 1)                                                                                   | * | 900       | 1000  |       | μV       |

# **ELECTRICAL CHARACTERISTICS**

### Table 4. Electrical Characteristics (Continued)

| SYMBOL                    | PARAMETER              | CONDITIONS                                                                                |   | MIN  | TYP   | MAX | UNITS  |

|---------------------------|------------------------|-------------------------------------------------------------------------------------------|---|------|-------|-----|--------|

|                           | MPS Pulse Current      | I <sub>VIN</sub> , In Addition To Supply Current                                          | * | 20   |       |     | mA     |

| Voltage Rea               | dback (Note 1)         |                                                                                           |   |      |       |     |        |

|                           | Full Scale Range       | VIN-RTN                                                                                   |   |      | 81.55 |     | V      |

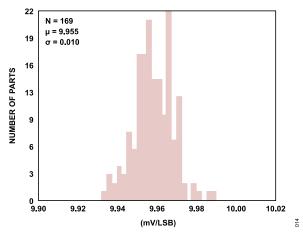

|                           | LSB Weight             | VIN-RTN                                                                                   |   |      | 9.955 |     | mV/LSB |

|                           | Conversion Period      | VIN > V <sub>ON</sub>                                                                     |   |      | 100   |     | ms     |

|                           | Full Scale Count       |                                                                                           |   |      | 16384 |     | bits   |

| Current Rea               | dback (Note 1)         |                                                                                           |   |      |       |     |        |

|                           | Full Scale Range       | SNSP-SNSN                                                                                 |   |      | 101.1 |     | mV     |

|                           | LSB Weight             | SNSP-SNSN                                                                                 |   |      | 12.34 |     | µV/LSB |

|                           | Conversion Period      | VIN > V <sub>ON</sub>                                                                     |   |      | 100   |     | ms     |

|                           | Full Scale Count       |                                                                                           |   |      | 16384 |     | bits   |

| Power Read                | back (Note 1)          | · · · · · ·                                                                               |   |      | 1     |     |        |

|                           | Full Scale Range       | VIN-RTN, SNSP-SNSN = 50mΩ                                                                 |   |      | 165.5 |     | W      |

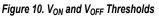

|                           | LSB Weight             | VIN-RTN, SNSP-SNSN = 50mΩ                                                                 |   |      | 20.20 |     | mW/LSE |

|                           | Conversion Period      | VIN > V <sub>ON</sub>                                                                     |   |      | 100   |     | ms     |

| I <sup>2</sup> C Timing ( | Note 1, Figure 22)     | · · · · · · · · · · · · · · · · · · ·                                                     |   |      |       |     |        |

| f <sub>SCLK</sub>         | Clock Frequency        |                                                                                           | * |      |       | 400 | kHz    |

| t <sub>1</sub>            | Bus Free Time          |                                                                                           | * | 1300 |       |     | ns     |

| t <sub>2</sub>            | Start Hold Time        |                                                                                           | * | 600  |       |     | ns     |

| t <sub>3</sub>            | SCL Low Time           |                                                                                           | * | 1300 |       |     | ns     |

| t <sub>4</sub>            | SCL High Time          |                                                                                           | * | 600  |       |     | ns     |

| t <sub>5</sub>            | SDAIN Data Hold Time   |                                                                                           | * | 0    |       |     | ns     |

|                           | SDAOUT Data Valid Time | $R_{BYP-SCL}$ , $R_{BYP-SDAOUT}$ = 10k $\Omega$ , $C_{BYP-SCL}$ , $C_{BYP-SDAOUT}$ = 10pF |   |      | 470   |     | ns     |

| t <sub>6</sub>            | Data Setup Time        |                                                                                           | * | 100  |       |     | ns     |

| t <sub>7</sub>            | Start Setup Time       |                                                                                           | * | 600  |       |     | ns     |

| t <sub>8</sub>            | Stop Setup Time        |                                                                                           | * | 600  |       |     | ns     |

| t <sub>r</sub>            | SCL, SDAIN Rise Time   |                                                                                           | * |      |       | 300 | ns     |

| t <sub>f</sub>            | SCL, SDAIN Fall Time   |                                                                                           | * |      |       | 300 | ns     |

|                           | SCL Fall to ACK Low    | $R_{BYP-SCL}$ , $R_{BYP-SDAOUT}$ = 10kΩ, $C_{BYP-SCL}$ , $C_{BYP-SDAOUT}$ = 10pF          |   |      | 470   |     | ns     |

Note 1: Guaranteed by design, not subject to test.

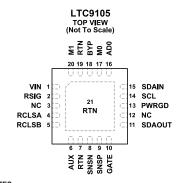

### **PIN CONFIGURATION AND FUNCTION**

NOTES 1. NC = NO CONNECTION. NOT INTERNALLY CONNECTED.

#### Figure 2. Pin Configuration

#### Table 5. Pin Function

| Pin No.                 | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                       | VIN      | PD Interface Supply Voltage. Positive input voltage for IEEE state machine and PD input voltage are referenced to this pin.                                                                                                                                                                                                                                                                                                |

| 2                       | RSIG     | External Signature Resistor Connection. Connect a 24.9kΩ resistor between RSIG and VIN.                                                                                                                                                                                                                                                                                                                                    |

| 4                       | RCLSA    | Class Select Input. Connect a resistor between RCLSA and RTN per Table 6.                                                                                                                                                                                                                                                                                                                                                  |

| 5                       | RCLSB    | Class Select Input. Connect a resistor between RCLSB and RTN per Table 6.                                                                                                                                                                                                                                                                                                                                                  |

| 6                       | AUX      | Auxiliary Power Supply Input Sensing. This pin senses the presence of another power supply input. The AUX pin status is reflected in the aux_status bit. The AUX pin threshold can be configured by the aux_thresh bit. See Dual-Input Prioritization for a description of AUX pin behavior with respect to port or auxiliary priority.                                                                                    |

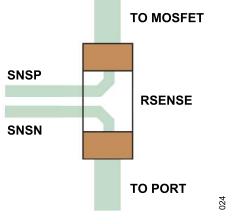

| 8                       | SNSN     | Current Sense Negative Input. System current is monitored using a $50m\Omega$ sense resistor between SNSP and SNSN. See <b>Sense Resistor</b> for kelvin sense requirements.                                                                                                                                                                                                                                               |

| 9                       | SNSP     | Current Sense Positive Input. System current is monitored using a $50m\Omega$ sense resistor between SNSP and SNSN. See <b>Sense Resistor</b> for kelvin sense requirements.                                                                                                                                                                                                                                               |

| 10                      | GATE     | External Hot Swap MOSFET Gate Control. Connect to gate of the external MOSFET.                                                                                                                                                                                                                                                                                                                                             |

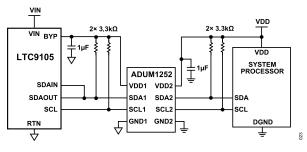

| 11                      | SDAOUT   | Serial Data Output. Open Drain Data Output for the I <sup>2</sup> C Serial Interface Bus. The LTC9105 uses two pins to implement the bidirectional SDA function to simplify isolation of the I <sup>2</sup> C bus. To implement a standard bidirectional SDA pin, tie SDAOUT and SDAIN together. See I2C Interface for more information.                                                                                   |

| 13                      | PWRGD    | Power Good Open Drain Output. During inrush this pin sinks 250 $\mu$ A (typ.) to prevent the power supply from starting up. Current draw begins when VIN-RTN exceeds the V <sub>ON</sub> threshold and continues for t <sub>PWRGD</sub> (93.75ms typ.). The PWRGD pin is high impedance before and after inrush.                                                                                                           |

| 14                      | SCL      | Serial Clock Input. High impedance clock input for the I <sup>2</sup> C serial interface bus. Internally pulled up to BYP through a $50k\Omega$ (typ.) resistor. See I2C Interface for more information.                                                                                                                                                                                                                   |

| 15                      | SDAIN    | Serial Data Input. High impedance data input for the I <sup>2</sup> C serial interface bus. The LTC9105 uses two pins to implement the bidirectional SDA function to simplify isolation of the I <sup>2</sup> C bus. To implement a standard bidirectional SDA pin, tie SDAOUT and SDAIN together. Internally pulled up to BYP through a $50k\Omega$ (typ.) resistor. See I <sub>2</sub> C Interface for more information. |

| 16                      | AD0      | I <sup>2</sup> C Chip Address Bit 0 Select. Use this pin to change the I <sup>2</sup> C chip address. Tie this pin to RTN to set I <sup>2</sup> C address bit AD0 to 0.<br>Tie this pin to BYP to set bit AD0 of the I <sup>2</sup> C chip address to 1. Internally pulled down to RTN through a 50kΩ (typ.) resistor.<br>See I <sup>2</sup> C Interface for more information.                                             |

| 17, 20                  | M[1:0]   | PoE Minimum Power Select. Use these pins to set the minimum number of Mark events required to enable the external MOSFET and power up the load. Tie high by connecting to BYP. Tie low by connecting to RTN. Internally pulled down to RTN through a 50kΩ (typ.) resistor.                                                                                                                                                 |

| 18                      | BYP      | Internal Power Supply Bypass. Connect a 1µF ceramic capacitor between this pin and RTN.                                                                                                                                                                                                                                                                                                                                    |

| 7, 19, 21 (Exposed Pad) | RTN      | PD Interface Return Rail. Pin 21 (Exposed Pad) must be connected to pin 7, pin 19, and PCB heat sink.                                                                                                                                                                                                                                                                                                                      |

| 3, 12                   | NC       | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                   |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

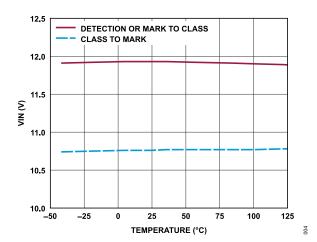

Figure 4. V<sub>CLASS</sub> and V<sub>MARK</sub> Thresholds

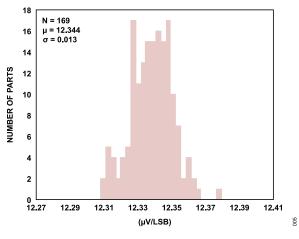

Figure 5. Current Readback LSB Weight

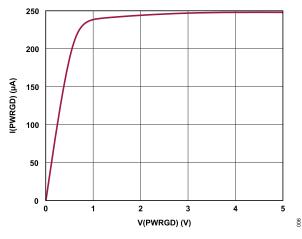

Figure 6. PWRGD Pin Pull-down Current

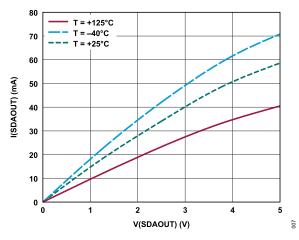

Figure 7. SDAOUT Pin Pull-down Current

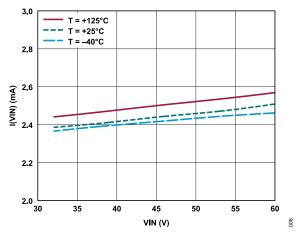

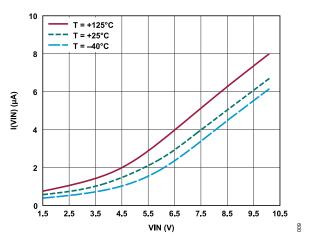

Figure 8. VIN Pin Power On Operating Current

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 11. Power Readback LSB Weight

Figure 12. VIN Pin Reset Threshold

Figure 13. RSIG Pin Pull-down Resistance

Figure 14. Voltage Readback LSB Weight

### OVERVIEW

The LTC9105 is an IEEE 802.3af/at/bt-compliant powered device (PD) interface controller, allowing up to 90W operation while maintaining backwards compatibility with existing power sourcing equipment (PSE). The I<sup>2</sup>C interface on the LTC9105 provides a simple and standard interface for the read back of the PD interface controller's input state, including PSE allocated power, auxiliary power supply presence, input voltage, and system current. Further, the LTC9105 can be configured through I<sup>2</sup>C. Two LTC9105s, or a single LTC9105 and an optional auxiliary supply, can provide hot backup applications with automatic, seamless fail-over. An LTC9105 can also be configured not to apply power to downstream circuitry when the attached PSE provides insufficient power for the PD application.

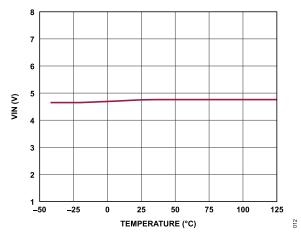

The LTC9105 controls a low  $R_{DS(ON)}$  N-channel MOSFET to maximize efficiency and delivered power. System current is sensed across a 50m $\Omega$  resistor. Analog Devices also provides a complete family of PSE, PD, and ideal bridge solutions. See <u>Related Parts</u> section at the end of this data sheet for more information.

### MODES OF OPERATION

### **Detection Signature**

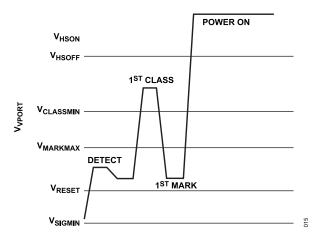

During detection, the PSE looks for a  $25k\Omega$  signature resistor, which identifies the device as a PD. The PSE applies two voltages in the range of 2.7V to 10.1V and measures the corresponding currents. Figure 15 shows the detection voltages. The PSE calculates the signature resistance using a  $\Delta V/\Delta I$  measurement technique.

The LTC9105 presents the external signature resistor by connecting the RSIG pin to RTN, allowing the PSE to recognize that the PD is present and requesting power to be applied. A value of  $24.9k\Omega$  is recommended for the external signature resistor.

### IEEE 802.3bt Single-Signature vs Dual-Signature PDs

IEEE 802.3bt defines two PD topologies: single-signature and dual-signature. The LTC9105 primarily targets single-signature PD topologies, eliminating the need for a second PD controller. All PD descriptions and IEEE 802.3 standard references in this data sheet are limited in scope to single-signature PDs. The LTC9105 may also be deployed in dual-signature PD applications. For more information, contact Analog Devices.

### IEEE 802.3bt Physical Classification, Mark, and Demotion

IEEE 802.3af/at/bt defines physical layer classification to allow a PD to request a power allocation from the connected PSE and to allow the PSE to inform the PD of the PSE's available power. A PSE, after a successful detection, may apply a classification probe voltage of 14.5V to 20.5V and measure the PD classification signature current. Once the PSE applies a classification probe voltage, the PSE may return the PD voltage to the mark voltage range before applying another classification probe voltage, or powering up the PD. An IEEE 802.3bt PSE may apply as many as five events before powering up the PD.

IEEE 802.3af/at/bt defines nine PD classes and four PD types. The LTC9105 requested class is configured by connecting RCLSA and RCLSB to RTN with 1% resistors, as shown in Table 6.

Table 6. IEEE 802.3bt Single-Signature Classification, Power Levels, and Resistor Selection

| PD Re-<br>quested<br>Class | PD Re-<br>quested<br>Power (W) | PD Type     | Nominal<br>Class Cur-<br>rent (mA) | RCLSA (Ω) | RCLSB (Ω) |

|----------------------------|--------------------------------|-------------|------------------------------------|-----------|-----------|

| 0                          | 13                             | Type 1      | 2.5                                | 487       | Open      |

| 1                          | 3.84                           | Type 1 or 3 | 10.5                               | 97.6      | Open      |

| 2                          | 6.49                           | Type 1 or 3 | 18.5                               | 54.9      | Open      |

| 3                          | 13                             | Type 1 or 3 | 28                                 | 35.7      | Open      |

| 4                          | 25.5                           | Type 2 or 3 | 40                                 | 24.9      | Open      |

| 5                          | 40                             | Туре 3      | 40 / 2.5                           | 487       | 26.1      |

| 6                          | 51                             | Туре 3      | 40 / 10.5                          | 97.6      | 33.2      |

| 7                          | 62                             | Type 4      | 40 / 18.5                          | 54.9      | 45.3      |

| 8                          | 71.3                           | Type 4      | 40 / 28                            | 35.7      | 78.7      |

A PD is demoted when the requested power level is not available from the PSE. If demoted, the PD must operate in a lower power state. The PSE allocated power is determined by the PD requested Class and the pse mark field, as shown in Table 7.

| PD Requested Class | pse_mark      | PSE Allocated Power |

|--------------------|---------------|---------------------|

| 0                  | Any           | 13W                 |

| 1                  | Any           | 3.84W               |

| 2                  | Any           | 6.49W               |

| 3                  | Any           | 13W                 |

| 4                  | 00b           | 13W                 |

|                    | 01b, 10b, 11b | 25.5W               |

| 5                  | 00b           | 13W                 |

|                    | 01b           | 25.5W               |

|                    | 10b, 11b      | 40W                 |

| 6                  | 00b           | 13W                 |

|                    | 01b           | 25.5W               |

|                    | 10b, 11b      | 51W                 |

| 7                  | 00b           | 13W                 |

|                    | 01b           | 25.5W               |

|                    | 10b           | 51W                 |

|                    | 11b           | 62W                 |

| 8                  | 00b           | 13W                 |

|                    | 01b           | 25.5W               |

| _                  | 10b           | 51W                 |

|                    | 11b           | 71.3W               |

### Table 7. PSE Allocated Power

#### **Minimum Initial Required Power**

IEEE compliance requires PDs to provide an active indication to the user when a PSE allocates insufficient power through a PSE behavior known as demotion. For PD applications that do not support demotion, the LTC9105 can be configured to block the PD application from powering up and to provide an indication.

To determine if the LTC9105 should apply power, the LTC9105 compares the number of mark events provided by the PSE to the M1 and M0 pin settings. Connect pins M1 and M0 to BYP or RTN according to Table 8 to configure the minimum initial required power.

| Initial Power |        |        |               |              |

|---------------|--------|--------|---------------|--------------|

| Requirement   | M1 PIN | M0 PIN | pse_mark      | MOSFET State |

| 13W or less   | RTN    | RTN    | Any           | ON           |

| 13W thru      | RTN    | BYP    | 00b           | OFF          |

| 25.5W         |        |        | 01b, 10b, 11b | ON           |

| 25.5W thru    | BYP    | RTN    | 00b, 01b      | OFF          |

| 51W           |        |        | 10b, 11b      | ON           |

| Greater than  | BYP    | BYP    | 00b, 01b, 10b | OFF          |

| 51W           |        |        | 11b           | ON           |

When insufficient power is allocated and the AUX pin is low, the PWRGD pin sinks  $I_{PWRGD}$ , the Hot Swap MOSFET is turned off,

analog.com

and the LTC9105 draws minimal current (see Automatic Maintain Power Signature) to keep the PoE input powered. The PWRGD pin and MOSFET state can be combined as an indication of insufficient power allocation.

### Link Layer Discovery Protocol (LLDP) Power Negotiation

In PoE systems, after initial power-on, power may be renegotiated through LLDP. The LTC9105 does not have access to Ethernet data and does not react automatically to LLDP power negotiation, including PWRGD pin state, MOSFET state, and seamless switchover settings.

For seamless switchover applications, the application processor may need to update the LTC9105's power priority mode when renegotiating power through LLDP. See Dual-Input Prioritization.

### Inrush and Power On

Once the PSE detects and classifies the PD, the PSE applies power to the PD depending on the rules described in Dual-Input Prioritization. When the port voltage rises above the V<sub>ON</sub> threshold, and the LTC9105 determines if the PSE allocated power is equal or higher than the PD requested power, and if an auxiliary power source is not present (through the aux\_status bit), the LTC9105 drives the external MOSFET GATE pin so as to allow a 100mA (typ) current to charge the external bulk capacitor. When the bulk capacitor is fully charged and the MOSFET current drops below 100mA, the external MOSFET is fully enhanced. In the event the external MOSFET does not enhance within 93.75ms (typ), inrush times out.

When inrush times out, the MOSFET turns off and the Automatic MPS feature is disabled. The PD remains in this state until the port voltage drops below  $V_{OFF}$ . See Automatic Maintain Power Signature for further description of the Automatic MPS feature.

### Power Good

The PWRGD pin is used to hold off the downstream circuitry until inrush is complete and the external MOSFET is fully enhanced.

The PWRGD pin first sinks  $I_{PWRGD}$  (250uA, typ.) starting when the port voltage rises above  $V_{ON}$  and continuing for up to  $t_{PWRGD}$ (93.75ms, typ.), then enters a high impedance state to allow an external PWRGD pull-up to assert the power good indication.

### AUXILIARY INPUT

The AUX pin is used to detect when an auxiliary power supply is attached. Figure 16 shows an example of an AUX sensing circuit.

When an auxiliary power supply is detected, aux\_status is set to 1. The LTC9105 MOSFET state (ON or OFF) is configurable, based on stdby\_dis and priority bit settings; see Dual-Input Prioritization for seamless switchover options, example AUX sensing circuit, and register configuration.

Figure 16. LTC9105 with Auxiliary Power Supply Input

## **DUAL-INPUT PRIORITIZATION**

The LTC9105 supports dual-input power path prioritized solutions. The first input is a primary LTC9105 and the second input may be either an auxiliary supply (see Figure 17) or a secondary LTC9105. The LTC9105 targets seamless switchover topologies, which only draw power from one input at a time, switching over to the secondary input when power is removed from the primary input.

Details on PD/auxiliary seamless switchover are provided in this data sheet. Contact Analog Devices for information and support regarding dual PD seamless switchover, to enable hitless failover between dual-port PoE supplies.

LTC9105 systems enable three power priority modes, as shown in Table 9. An LTC9105 configured in Primary mode provides power to the load. An LTC9105 configured in Hot Secondary mode enables seamless switchover, providing power to the load when power is removed from the first input. An LTC9105 may be ineligible to provide seamless switchover due to insufficient power allocation; in this case, an LTC9105 may be configured in Cold Secondary mode to prevent seamless switchover when power is removed from the first input, forcing a system reboot and power allocation refresh.

If the AUX pin is low (AUX < V<sub>AUX\_TH</sub>) at LTC9105 power on, the LTC9105 sets its priority bit and clears its stdby\_dis bit, entering Primary mode.

If the AUX pin is high (AUX >  $V_{AUX_TH}$ ) at LTC9105 power on, the LTC9105 automatically clears its priority and stdby\_dis bits, entering Hot Secondary mode.

In Hot Secondary mode, the LTC9105 will automatically transition to Primary mode when AUX pin goes low. This seamless switchover ensures power is maintained at the load.

In Cold Secondary mode, the LTC9105 automatically removes MPS when the AUX pin goes low. This behavior enables a port power cycle through the IEEE DC MPS feature to force a system reboot and power allocation refresh. Cold Secondary mode is used to ensure a higher power primary input does not fail-over to a lower power secondary input. Applications implementing Cold Secondary mode must take care to reduce total current below the minimum IEEE DC MPS threshold (4mA) to meet IEEE requirements for power removal.

Current is limited by the PSE during a seamless switchover event.

The switchover threshold from primary to secondary is set using an external AUX circuit. The switchover threshold should be set just under the V<sub>PORT\_PD-2P,MIN</sub> threshold for the application's requested PoE Class as specified in IEEE 802.3bt standard. The IEEE standard specifies V<sub>PORT\_PD-2P</sub> at the RJ-45 interface. Remember to consider any extra voltage drops due to diode forward voltage or resistance between the RJ-45 connector and the AUX circuit.

Figure 17. LTC9105 with Dual-Input Auxiliary Circuit

#### Table 9. Power Priority Modes and Behaviors

| Mode          | priority | stdby_dis | MOSFET State | Description                                                                                                                                                                                                                                              |

|---------------|----------|-----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Primary       | 1        | 0         | ON           | MPS current is drawn automatically if load current drops below MPS.                                                                                                                                                                                      |

| Hot Secondary | 0        | 0         | OFF          | MPS current is drawn automatically, to keep the PoE input powered.<br>If the primary input drops, as sensed at AUX pin, the secondary input<br>automatically becomes the primary input by enabling the LTC9105's<br>MOSFET and setting the priority bit. |

#### Table 9. Power Priority Modes and Behaviors (Continued)

| Mode           | priority | stdby_dis | MOSFET State | Description                                                                                                                                                                                                             |

|----------------|----------|-----------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cold Secondary | 0        | 1         | OFF          | MPS current is drawn automatically, to keep the PoE input powered. If the primary input drops, as sensed at AUX pin, the MPS current is removed and the LTC9105's MOSFET remains disabled, enabling a port power cycle. |

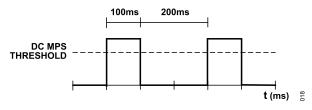

### **AUTOMATIC MAINTAIN POWER SIGNATURE**

A PSE removes power when a connected PD no longer draws a minimum amount of current, known as the maintain power signature (MPS) current. The LTC9105 implements an Automatic MPS feature, which detects when the current falls below the DC MPS threshold (20mA typ.,  $R_{SNSP-SNSN} = 50m\Omega$ ) and automatically generates a current pulse to maintain PoE power. This feature is enabled by default at power-up.

Figure 18 shows an example of Automatic MPS timing. The LTC9105's MPS state machine works on a 100ms (typ.) time base. An MPS pulse is issued when the average current over a 100ms (typ.) period drops below the DC MPS threshold. The MPS pulse current has an amplitude greater than 20mA and a duration of 100ms (typ.). No pulses are issued in the following 200ms (typ.). The LTC9105 stops drawing MPS pulse current once the average current is above the DC MPS threshold.

Automatic MPS is disabled in one of two conditions. First is when the inrush timer expires, that is, if power up of the load does not complete within 93.75ms (typ.). And second, when  $stdby_dis$  is set to 1 and an auxiliary supply is not present (when  $aux_status$  reports 0; when AUX <  $V_{AUX_TH}$ ).

Figure 18. MPS Timing

## ANALOG-TO-DIGITAL CONVERTERS (ADC)

The LTC9105 has two first order delta sigma analog-to-digital converters (ADCs) that simultaneously measure application current and supply voltage. The converters operate at an over sample rate (OSR) of 2.5MHz (typ.) and complete a full conversion every 100ms (typ.). First order delta sigma converters provide superior performance for power monitoring applications because the measured signals are averaged with even weight across the conversion period. Delta-sigma converters produce a mean average by integrating

the area under the signal curve across the conversion period. Furthermore, simultaneous conversion of voltage and current allows high accuracy power calculations, ensuring the voltage and current factors are sampled during the same period.

Measuring application power at the PD controller input captures the DC/DC conversion losses missed by traditional power monitors after the converter. Analog Devices recommends using the LT4321 ideal diode bridge for minimal bridge voltage drop and increased telemetry accuracy with respect to the RJ45 input (see **PoE Input Bridge** in External Component Selection).

### VIN Readback

When configured to report voltage telemetry by clearing the <code>padc\_en</code> bit, the LTC9105 continuously measures the VIN voltage with a dedicated A/D converter. This measurement is fully synchronized to the current measurement and can continue to monitor until VIN drops below V<sub>OFF</sub>. This telemetry is updated every 100ms.

When the padc\_data bit reports '0', the voltage\_power field contains voltage readings.

### **Power Readback**

When configured to report power telemetry by setting the <code>padc\_en</code> bit, the LTC9105 continuously measures the PD power by internally multiplying port voltage and current, and reports the power telemetry to the <code>voltage\_power</code> field. This measurement is fully synchronized to the current and voltage measurements and can continue to monitor until VIN drops below V<sub>OFF</sub>. This telemetry is updated every 100ms.

When the padc\_data bit reports '1', the voltage\_power field contains power readings.

### **Current Readback**

The LTC9105 measures the voltage across the SNSP and SNSN pins through a 50m $\Omega$  sense resistor. This measurement is fully synchronized to the power/voltage measurements and can continue to monitor until VIN drops below V\_OFF. Current telemetry is reported to the <code>current</code> field. This telemetry is updated every 100ms.

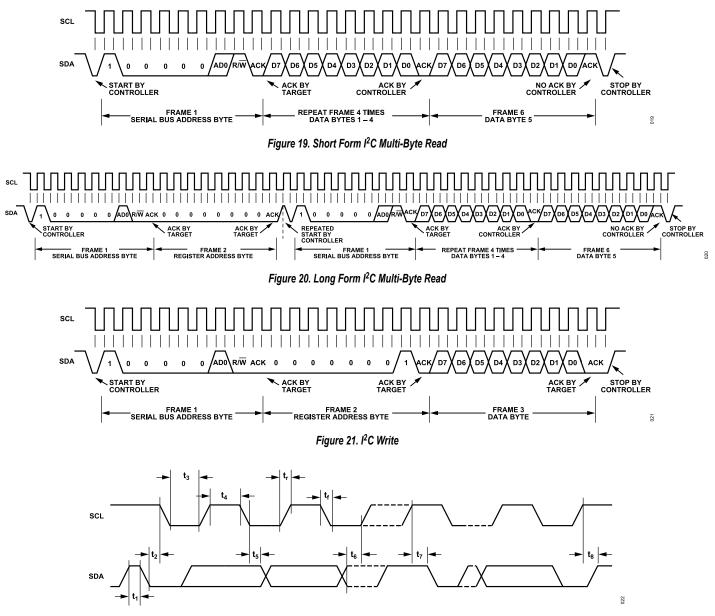

# I<sup>2</sup>C INTERFACE

Figure 22. I<sup>2</sup>C Interface Timing

### I<sup>2</sup>C Interface Overview

The LTC9105 includes an  $I^2C$  serial interface, enabling the PD's application processor to read parametric telemetry, PSE allocated power, and auxiliary input status; and to write power input priority. See Table 10 for register details and descriptions.

Figure 22 presents the I<sup>2</sup>C interface timing parameters. These parameters are defined for the LTC9105 in Electrical Characteristics.

### I<sup>2</sup>C Serial Address Byte

The LTC9105 chip address (bits [7:1] of the serial address byte) is settable to 0x40 or 0x41, based on the AD0 pin setting. Tie AD0 to RTN to set the chip address to 0x40, or tie AD0 to BYP to set the chip address to 0x41.

### I<sup>2</sup>C Read

There are two ways to read data from the  $l^2C$  port on the LTC9105. The LTC9105 responds to either a short form multi-byte read (Figure 19) or a long form multi-byte read (Figure 20). When reading from the LTC9105 with a long form multi-byte read, always read from register address 0x00.

I<sup>2</sup>C data is gathered from the LTC9105 in a single 5-byte read. Reading multiple bytes in the same transaction ensures that parametric data is from the same ADC conversion. For example, the current LSB and current MSB must be read concurrently to ensure that the upper byte and lower byte values are from the same conversion. Similarly, voltage (or power) and current read back must

# I<sup>2</sup>C INTERFACE

be done concurrently to ensure that data for power (or voltage) calculations are from the same period in time.

### I<sup>2</sup>C Write

The LTC9105 can be configured using an  $I^2C$  write, as shown in Figure 21. When writing to the LTC9105, always write to register address 0x01, and only write a single byte of data; only the first byte in the register map is writable.

## **REGISTER MAP**

### Table 10. I<sup>2</sup>C Register Map

| Byte | BIT 7                                    | BIT 6         | BIT 5                  | BIT 4      | BIT3        | BIT 2     | BIT 1    | BIT 0    |

|------|------------------------------------------|---------------|------------------------|------------|-------------|-----------|----------|----------|

| 1    | aux_status                               | pse_mark[1:0] |                        | aux_thresh | padc_enable | stdby_dis | priority | brownout |

| 2    | old_data                                 | ioverflow     | overflow current[13:8] |            |             |           |          |          |

| 3    | current[7:0]                             |               |                        |            |             |           |          |          |

| 4    | padc_data vpoverflow voltage_power[13:8] |               |                        |            |             |           |          |          |

| 5    | voltage_power[7:0]                       |               |                        |            |             |           |          |          |

### Table 11. I<sup>2</sup>C Register Details

| _    |     | _             |        | Reset              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-----|---------------|--------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Byte | Bit | Data          | Access | Value              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1    | 7   | aux_status    | RO     | See<br>description | Auxiliary Status. Returns 1 if an auxiliary supply is detected. Returns 0 if an auxiliary supply is absent.<br>See Auxiliary Input and Dual-Input Prioritization.<br>The reset value is determined by the AUX pin state.                                                                                                                                                                                                                                                                                                                      |

| 1    | 6:5 | pse_mark      | RO     | See<br>description | <ul> <li>PSE Mark Response. Combine this field with PD requested Class to determine PSE allocated power.</li> <li>See Table 7.</li> <li>0: 0-1 Mark Events, PSE allocated power is Min(PD Requested Class, 13W)</li> <li>1: 2-3 Mark Events, PSE allocated power is 25.5W</li> <li>2: 4 Mark Events, PSE allocated power is Min(PD Requested Class, 51W)</li> <li>3: 5+ Mark Events, PSE allocated power is Min(PD Requested Class, 71.3W)</li> <li>The reset value is a function of the preceding physical classification result.</li> </ul> |

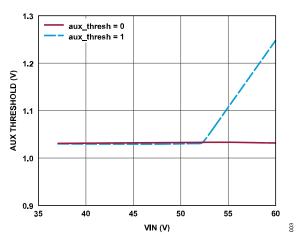

| 1    | 4   | aux_thresh    | R/W    | 0                  | Auxiliary Threshold Configuration. When set, the LTC9105 AUX pin uses a variable threshold (see Figure 3). When cleared, the LTC9105 AUX pin uses a 1.05V (typ.) threshold.                                                                                                                                                                                                                                                                                                                                                                   |

| 1    | 3   | padc_enable   | R/W    | 0                  | Power ADC Enable. When set, the LTC9105 reports input average power in the <code>voltage_power</code> field and the <code>padc_data</code> bit is set.<br>When clear, the LTC9105 reports the input average voltage in the <code>voltage_power</code> field and the <code>padc_data</code> bit is cleared.                                                                                                                                                                                                                                    |

| 1    | 2   | stdby_dis     | R/W    | 0                  | Standby Disable. Controls MOSFET state and Automatic MPS feature based on AUX pin state and priority setting. See Dual-Input Prioritization.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1    | 1   | priority      | R/W    | See<br>description | Port Priority. Controls MOSFET state and Automatic MPS feature based on AUX pin state and stdby_dis setting. See Dual-Input Prioritization.<br>The reset value is the inverse of the AUX pin state, and is latched on reset exit.                                                                                                                                                                                                                                                                                                             |

| 1    | 0   | brownout      | R/W1C  | 0                  | Brownout Indication. Indicates that the input voltage has fallen below $V_{OFF}$ threshold, then returned to $V_{ON}$ without crossing the $V_{RESET}$ threshold. Remains set until cleared by user. Clear by writing a 1 to this bit.                                                                                                                                                                                                                                                                                                        |

| 2    | 7   | old_data      | RO     | 0                  | Old Data Indication. This bit is set when an ADC conversion is read over the I <sup>2</sup> C interface and cleared when a new ADC conversion is available.                                                                                                                                                                                                                                                                                                                                                                                   |

| 2    | 6   | ioverflow     | RO     | 0                  | Current Overflow Status. If set, the current readback is an overflow (the measurement was outside the full scale range of the ADC). Disregard the value in current[13:0] when ioverflow is set. This field is updated with every ADC conversion.                                                                                                                                                                                                                                                                                              |

| 2    | 5:0 | current[13:8] | RO     | 0                  | Current Telemetry MSB. Upper bits of the current telemetry. Combine with current[7:0] for a complete current telemetry reading.<br>This field is updated with every ADC conversion.                                                                                                                                                                                                                                                                                                                                                           |

| 3    | 7:0 | current[7:0]  | RO     | 0                  | Current Telemetry LSB. Lower bits of the current telemetry. Combine with current [13:8] for a complete current telemetry reading.<br>Representing 246.8 $\mu$ A/LSb (14-bit) with an offset of 0x2000. Full scale range ±2.022A. All values are typical and assume R <sub>SNSP-SNSN</sub> = 50m $\Omega$ .<br>This field is updated with every ADC conversion.                                                                                                                                                                                |

| 4    | 7   | padc_data     | RO     | 0                  | Power Telemetry Indicator. Returns 1 if <pre>voltage_power[13:0]</pre> contains power data. Returns 0 if <pre>voltage_power[13:0]</pre> contains voltage data. This field is updated with every ADC conversion.                                                                                                                                                                                                                                                                                                                               |

# **REGISTER MAP**

### Table 11. I<sup>2</sup>C Register Details (Continued)

| Byte | Bit | Data                | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-----|---------------------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4    | 6   | vpoverflow          | RO     | 0              | Voltage/Power Overflow Status. If set, the voltage or power readback is an overflow<br>(the measurement was outside the full scale range of the ADC). Disregard the value in<br>voltage_power[13:0] when vpoverflow is set.<br>This field is updated with every ADC conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4    | 5:0 | voltage_power[13:8] | RO     | 0              | Voltage/Power Telemetry MSB. Upper bits of the voltage or power telemetry. Combine with voltage_power[7:0] for a complete voltage/power telemetry reading.<br>This field is updated with every ADC conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5    | 7:0 | voltage_power[7:0]  | RO     | 0              | $\label{eq:loss} \begin{array}{l} \mbox{Voltage/Power Telemetry LSB. Lower bits of the voltage or power telemetry. Combine with $voltage_power[13:8]$ for a complete voltage or power telemetry reading. $$ When padc_data is cleared, $voltage_power contains a voltage reading, representing $$ 9.955mV/LSB (14-bit) with an offset of 0x2000. Full scale range ±81.55V. $$ When padc_data is set, $voltage_power contains a power reading, representing 20.20mW/LSB (14-bit) with an offset of 0x2000. Full scale range ±165.5W. $$ All values are typical and assume $$ R_{SNSP-SNSN} = 50m\Omega. This field is updated with every ADC conversion. $$ Conversion. $$ Down and the provide the set of the s$ |

## Access Key:

R/W = Read/Write. Field can be read and written normally.

RO = Read Only. Field can be read normally. Writes to a "Read Only" field are ignored.

R/W1C = Read/Write-1-to-Clear. Field can be read normally. Bits that have '1' written to them are cleared. Bits that have '0' written to them are unchanged.

## **APPLICATIONS INFORMATION**

## EXTERNAL COMPONENT SELECTION

### **PoE Input Bridge**

A PD is required to polarity-correct its input voltage. There are several different options available for bridge rectifiers; silicon diodes, Schottky diodes, and ideal diodes. When silicon or Schottky diode bridges are used, the diode forward voltage drops affect the voltage at the VIN pin. The LTC9105 is designed to tolerate these voltage drops. Note, the parameters shown in Electrical Characteristics are specified at the LTC9105 package pins.

A silicon diode bridge consumes up to 4% of the available power. In addition, silicon diode bridges exhibit poor pairset-to-pairset unbalance performance. Each branch of a silicon diode bridge shares source/return current, and thermal runaway can cause large, noncompliant current unbalances between pairsets.

While using Schottky diodes can help reduce the power loss with a lower forward voltage, the Schottky bridge may not be suitable for high temperature PD applications. Schottky diode bridges exhibit temperature induced leakage currents. The leakage current has a voltage dependency that can invalidate the measured detection signature. In addition, these leakage currents can back-feed through the unpowered branch and the unused bridge, violating IEEE 802.3 specifications.

For high efficiency applications, the LT9105 supports an LT4321based PoE ideal diode bridge that reduces the forward voltage drop from 0.7V to 20mV per diode while maintaining IEEE 802.3 compliance. The LT4321 simplifies thermal design, eliminates costly heat sinks, and can operate in space-constrained applications. In addition, with the very low voltage drop of the LT4321 ideal diode bridge, the LTC9105's voltage readback is closer to the PD's true input voltage.

### **Input Capacitor**

A 0.1 $\mu$ F capacitor is needed from VIN to SNSN to meet the input impedance requirement in IEEE 802.3 and to properly bypass the LTC9105. When operating with the LT4321, locally bypass each with a 0.047 $\mu$ F capacitor, thus keeping the total port capacitance within specification. Place each capacitor as close as possible to both the LTC9105 and LT4321. See Figure 26.

### **Transient Voltage Suppressor**

The LTC9105 specifies an absolute maximum voltage of 100V and is designed to tolerate brief over voltage events due to Ethernet cable surges. To protect the LTC9105 from an overvoltage event, install a unidirectional transient voltage suppressor (TVS) such as an SMAJ58A or PTVS58VP1UTP between the VIN and SNSN pins. Place the TVS as close as possible to the LTC9105.

### **Exposed Pad**

The LTC9105 package has an exposed pad internally connected to RTN. The exposed pad may only be connected to RTN on the

printed circuit board. Ensure the Exposed Pad has access to a printed circuit board plane as a heat sink.

### Signature Resistor (RSIG)

A 24.9k $\Omega$ , 1% resistor must be connected between VIN and RSIG for IEEE compliant detection. The RSIG pin is low impedance when the input voltage is in the V<sub>SIG</sub> range, then switches to high impedance as the input voltage crosses into the V<sub>CLASS</sub> range to save power. The RSIG pin becomes low impedance again when the input voltage falls below V<sub>RESET</sub>.

### **External MOSFET**