# 24-/48-Port IEEE 802.3bt PoE PSE Controller

#### **FEATURES**

- ► Fully Compliant IEEE 802.3bt Type 3 2-Pair PSE

- ▶ Up to 48 PSE Ports with One Power Channel per Port

- ▶ +80V/–20V Tolerant Port-Facing Pins

- ► ECC-Protected eFlash and Data RAMs

- ▶ Industry-Leading Power Path Efficiency

- 100mΩ Sense Resistance

- 30mΩ or Lower MOSFET R<sub>DS(ON)</sub>

- ▶ Chipset Provides Electrical Isolation

- ► Eliminates Optos and Isolated 3.3V Supply

- ▶ Very High Reliability Multipoint PD Detection

- ► Continuous Voltage, Temperature, and Current Monitoring

- ▶ 1MHz I<sup>2</sup>C Compatible Serial Control Interface

- ▶ Pin or I<sup>2</sup>C Programmable PD Power

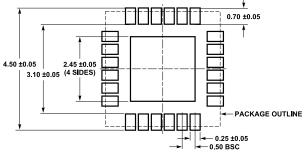

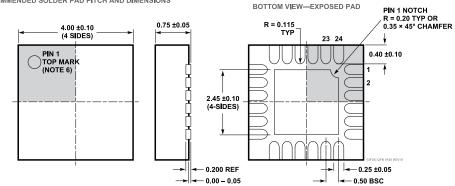

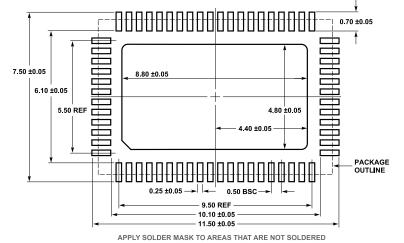

- Available in a 24-Lead 4mm × 4mm (LTC9101-2B) and 64-Lead 7mm × 11mm (LTC9102) QFN Packages

## **APPLICATIONS**

▶ PoE PSE Switches/Routers and Midspans

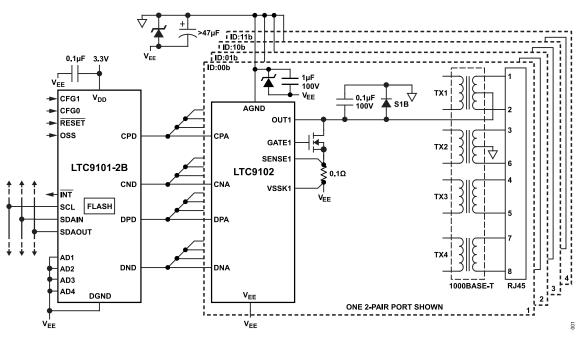

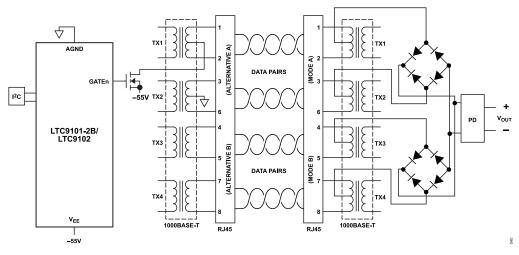

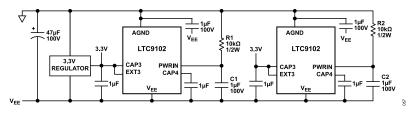

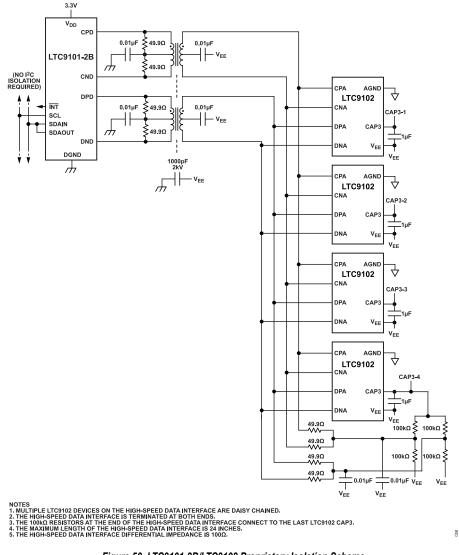

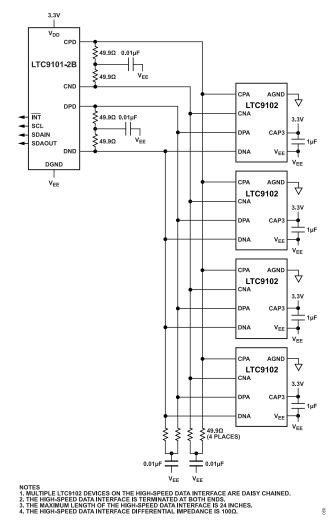

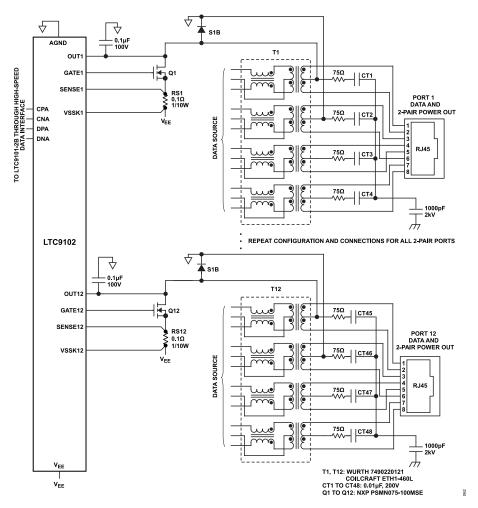

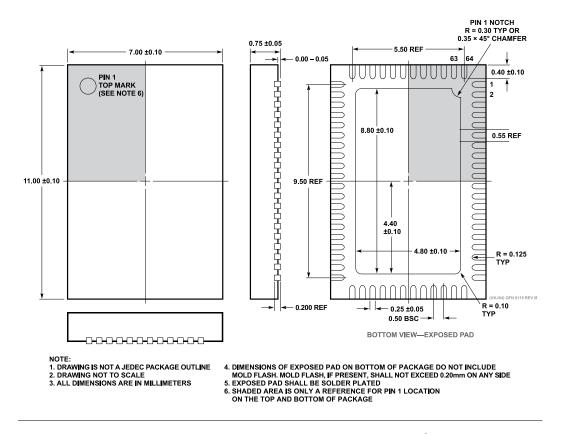

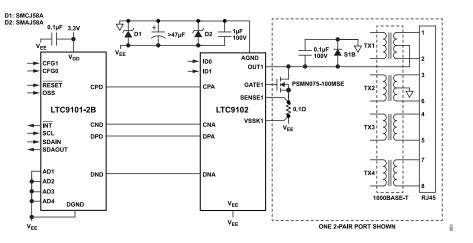

#### **TYPICAL APPLICATION**

## DESCRIPTION

The LTC<sup>®</sup>9101-2B/LTC9102 chipset is a 12-/24-/48-port power sourcing equipment (PSE) controller designed for use in IEEE 802.3bt-compliant Type 3 2-pair Power over Ethernet (PoE) systems. The LTC9101-2B/LTC9102 is designed to power compliant 802.3af, 802.3at, and 802.3bt PDs. The LTC9101-2B/LTC9102 chipset delivers lowest-in-industry heat dissipation by utilizing low  $R_{DS(ON)}$  external MOSFETs and 0.1 $\Omega$  sense resistance per power channel. A transformer-isolated communication protocol replaces expensive opto-couplers and a complex isolated 3.3V supply, resulting in significant BOM cost savings.

Advanced power management features include per-port 14-bit current/voltage monitoring, programmable power limits, and versatile fast shut down of preselected ports. PD detection uses a proprietary multipoint detection mechanism ensuring excellent immunity from false PD identification. Autoclass and 2-event physical classification are supported. The LTC9101-2B/LTC9102 includes an I<sup>2</sup>C serial interface operable up to 1MHz. The LTC9101-2B/LTC9102 is pin or I<sup>2</sup>C programmable to negotiate PD delivered power up to 25.5W.

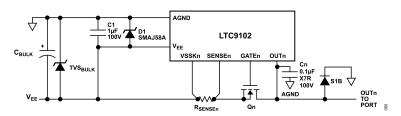

Figure 1. 802.3bt 2-Pair Application, 1 Port Shown

Analog Devices, Inc., is in the process of updating documentation to provide terminology and language that is culturally appropriate, which is a process with a wide scope and will be phased in as quickly as possible. Thank you for your patience.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features                             | 1   |

|--------------------------------------|-----|

| Applications                         | . 1 |

| Description                          | .1  |

| Typical Application                  | .1  |

| Absolute Maximum Ratings             | .3  |

| LTC9101-2B                           | 3   |

| LTC9102                              | .3  |

| ESD Caution                          | .3  |

| Pin Configurations                   | 4   |

| Order Information                    | 5   |

| Electrical Characteristics           | 6   |

| Typical Performance Characteristics1 | 10  |

| Test Timing Diagrams1                | 14  |

| I <sup>2</sup> C Timing Diagrams1    | 15  |

| Pin Functions1                       | 16  |

| Applications Information1            |     |

| Overview1                            |     |

## **REVISION HISTORY**

11/2024—Revision 0: Initial Version

| 802.3bt 2-Pair Operation     |    |

|------------------------------|----|

| PoE Basics                   | 20 |

| Device Configuration         | 21 |

| Operating Modes              |    |

| Connection Check             |    |

| Detection                    |    |

| Classification               | 24 |

| Power Control                | 26 |

| Serial Digital Interface     | 30 |

| Isolation Requirements       | 30 |

| External Component Selection | 31 |

| Layout Requirements          | 35 |

| Typical Applications         |    |

| Package Description          | 37 |

| Typical Application          |    |

| Related Parts                |    |

|                              |    |

## **ABSOLUTE MAXIMUM RATINGS**

#### LTC9101-2B

| PARAMETER                                      | RATING                          |

|------------------------------------------------|---------------------------------|

| Supply Voltages (with respect to DGND)         |                                 |

| V <sub>DD</sub>                                | –0.3V to 3.6V                   |

| CAP1, CAP2                                     | -0.3V to 1.32V                  |

| Digital Pins                                   |                                 |

| ADn, CFGn, OSS, SDAIN, SDAOUT, SCL, RESET, INT | –0.3V to V <sub>DD</sub> + 0.3V |

| Analog Pins                                    |                                 |

| CPD, CND, DPD, DND                             | –0.3V to V <sub>DD</sub> + 0.3V |

| Operating Ambient Temperature Range            | -40°C to 85°C                   |

| Operating Junction Temperature Range (Note 2)  | -40°C to 125°C                  |

| Storage Temperature Range                      | –65°C to 150°C                  |

#### LTC9102

Table 2. (Note 1)

| PARAMETER                                          | RATING               |

|----------------------------------------------------|----------------------|

| Supply Voltages (with respect to V <sub>EE</sub> ) |                      |

| AGND                                               | -0.3V to 80V         |

| PWRIN                                              | -0.3V to 80V         |

| CAP3, CAP4                                         | –0.3V to 5V          |

| VSSKn                                              | -0.3V to 0.3V        |

| Analog Pins                                        |                      |

| SENSEn, OUTn                                       | –20V to 80V          |

| GATEn, IDn, PWRMDn                                 | -0.3V to 80V         |

| CPA, CNA, DPA, DNA                                 | -0.3V to CAP3 + 0.3V |

| EXT3                                               | -0.3V to 30V         |

| Operating Ambient Temperature Range                | –40°C to 85°C        |

| Operating Junction Temperature Range (Note 2)      | -40°C to 125°C       |

| Storage Temperature                                | –65°C to 150°C       |

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

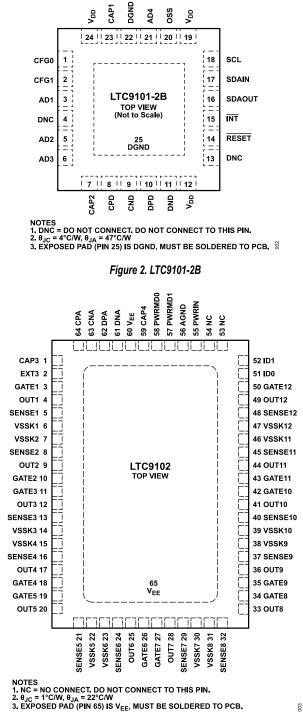

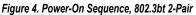

#### **PIN CONFIGURATIONS**

Figure 3. LTC9102

#### **ORDER INFORMATION**

#### Table 3.

| LEAD FREE FINISH                                                                                                                                                                | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------|----------------------------------|-------------------|--|

| LTC9101AUF-2B#PBF                                                                                                                                                               | LTC9101AUF-2B#TRPBF | 9101B        | 24-Lead (4mm × 4mm) Plastic QFN  | -40°C to 85°C     |  |

| LTC9102AUKJ#PBF                                                                                                                                                                 | LTC9102AUKJ#TRPBF   | LTC9102      | 64-Lead (7mm × 11mm) Plastic QFN | -40°C to 85°C     |  |

| Contact the factory for parts specified with wider operating temperature ranges. Tape and reel specifications. Some packages are available in 500 unit reels through designated |                     |              |                                  |                   |  |

Contact the factory for parts specified with wider operating temperature ranges. Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

The \* denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . AGND –  $V_{EE} = 55V$  and  $V_{DD}$  – DGND = 3.3V unless otherwise noted. (Notes 3 and 4)

| SYMBOL                               | PARAMETER                              | CONDITIONS                                                         |   | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------|----------------------------------------|--------------------------------------------------------------------|---|------|------|------|-------|

|                                      | Main PoE Supply Voltage                | AGND – V <sub>EE</sub>                                             |   |      |      |      |       |

|                                      |                                        | Type 3 Compliant Output                                            | * | 51   |      | 57   | V     |

|                                      | LTC9102 Undervoltage Lockout           | AGND – V <sub>EE</sub>                                             | * |      | 8.2  | 9    | V     |

| V <sub>DD</sub>                      | V <sub>DD</sub> Supply Voltage         | V <sub>DD</sub> – DGND                                             | * | 3    | 3.3  | 3.6  | V     |

|                                      | Undervoltage Warning                   |                                                                    |   |      | 2.8  |      | V     |

|                                      | Undervoltage Lockout                   |                                                                    |   |      | 2.6  |      |       |

|                                      | V <sub>DD</sub> Slew Rate, Falling     | 2.4 ≤ V <sub>DD</sub> – DGND ≤ 3.0 (Note 7)                        |   |      |      | 20   | mV/µs |

| V <sub>CAP1.</sub> V <sub>CAP2</sub> | Internal Regulator Supply Voltage      | V <sub>CAP1</sub> – DGND, V <sub>CAP2</sub> – DGND (Note 13)       |   |      | 1.2  |      | V     |

| V <sub>CAP3</sub>                    | Internal 3.3V Regulator Supply Voltage | CAP3 – V <sub>EE</sub> (Note 13)                                   | * | 3    | 3.3  | 3.6  | V     |

| CAPSEXT                              | CAP3 External Supply Rise Time         | 0.5V < CAP3 < CAP3(Min), EXT3 Tied to CAP3 (Note 7)                | * |      |      | 1    | ms    |

| V <sub>CAP4</sub>                    | Internal 4.3V Regulator Supply Voltage | CAP4 – V <sub>EE</sub> (Note 13)                                   | * |      | 4.3  |      | V     |

| EE                                   | V <sub>EE</sub> Supply Current         | PWRIN Pin Connected to AGND, EXT3 LOW, All Gates Fully<br>Enhanced |   | 7.7  | 11   | 14   | mA    |

|                                      | 3.3V Rail Supply Current               | From CAP3 = 3.3V (EXT3 HIGH)                                       |   | 4.2  | 5.4  | 6.6  | mA    |

| I <sub>DD</sub>                      | V <sub>DD</sub> Supply Current         | (V <sub>DD</sub> – DGND) = 3.3V                                    | * |      | 40   | 60   | mA    |

| Detection                            |                                        |                                                                    |   |      |      |      |       |

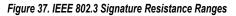

|                                      | Forced Current                         | Load Resistance 15.5k to 32k                                       | * | 220  | 240  | 260  | μA    |

|                                      |                                        |                                                                    | * | 143  | 160  | 180  | μA    |

|                                      | Forced Voltage                         | Load Resistance 18.5k to 27.5k                                     | * | 7    | 8    | 9    | V     |

|                                      |                                        |                                                                    | * | 3    | 4    | 5    | V     |

|                                      | Detection Current Compliance           | AGND – OUTn = 0V                                                   | * |      | 0.8  | 0.9  | mA    |

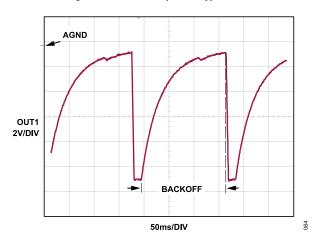

| V <sub>oc</sub>                      | Detection Voltage Compliance           | AGND – OUTn, Open Port                                             | * |      | 10.4 | 12   | V     |

|                                      | Detection Voltage Slew Rate            | AGND – OUTn, C <sub>PORT</sub> = 150nF (Note 7)                    |   |      |      | 0.01 | V/µs  |

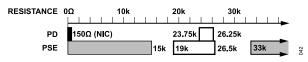

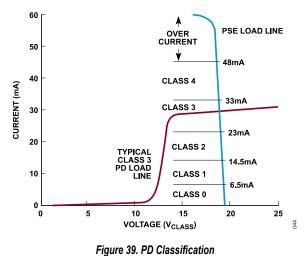

|                                      | Min. Valid Signature Resistance        |                                                                    | * | 15.5 | 17   | 18.5 | kΩ    |

|                                      | Max. Valid Signature Resistance        |                                                                    | * | 27.5 | 29.7 | 32   | kΩ    |

| Classification                       |                                        |                                                                    |   |      |      |      |       |

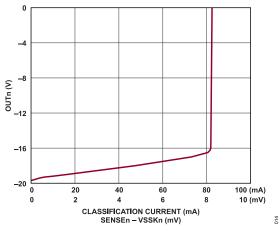

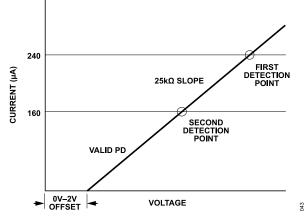

| V <sub>CLASS</sub>                   | Classification Voltage                 | AGND – OUTn, SENSEn – VSSKn < 5mV                                  | * | 16   |      | 20.5 | V     |

| 01.00                                | Classification Current Compliance      | SENSEn – VSSKn, OUTn = AGND (Note 14)                              | * | 7    | 8    | 9    | mV    |

|                                      | Classification Threshold               | SENSEn – VSSKn (Note 14)                                           |   |      |      |      |       |

|                                      |                                        | Class Signature 0 – 1                                              | * | 0.5  | 0.65 | 0.8  | mV    |

|                                      |                                        | Class Signature 1 – 2                                              | * | 1.3  | 1.45 | 1.6  | mV    |

|                                      |                                        | Class Signature 2 – 3                                              | * | 2.1  | 2.3  | 2.5  | mV    |

|                                      |                                        | Class Signature 3 – 4                                              | * | 3.1  | 3.3  | 3.5  | mV    |

|                                      |                                        | Class Signature 4 – Overcurrent                                    | * | 4.5  | 4.8  | 5.1  | mV    |

| V <sub>MARK</sub>                    | Classification Mark State Voltage      | AGND – OUTn, SENSEn – VSSKn < 5mV                                  | * | 7.5  | 9    | 10   | V     |

| in a de                              | Mark State Current Compliance          | OUTn = AGND                                                        | * | 7    | 8    | 9    | mV    |

| Gate Driver                          |                                        |                                                                    |   |      |      |      |       |

|                                      | GATE Pin Pull-Down Current             | Port Off, GATEn = V <sub>EE</sub> + 5V                             |   |      | 1    |      | mA    |

|                                      | GATE Pin Fast Pull-Down Current        | $GATEn = V_{EE} + 5V$                                              |   |      | 65   | 1    | mA    |

|                                      | GATE Pin On Voltage                    | GATEn – V <sub>EE</sub> , I <sub>GATEn</sub> = 1µA                 | * | 11   |      | 14   | V     |

| Output Voltag                        |                                        |                                                                    |   |      |      |      | 1     |

| V <sub>PG</sub>                      | Power Good Threshold Voltage           | OUTn – V <sub>EE</sub>                                             | * | 2    | 2.4  | 2.8  | V     |

|                                      | OUT Pin Pull-Up Resistance to AGND     | Port On                                                            |   |      | 2500 | -    | kΩ    |

|                                      |                                        | Port Off                                                           | * | 300  | 500  | 700  | kΩ    |

## Table 4. (Continued)

| SYMBOL                   | PARAMETER                                               | CONDITIONS                                                                                            |          | MIN  | TYP   | MAX | UNITS  |

|--------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|------|-------|-----|--------|

| Current Sense            | 9                                                       |                                                                                                       |          |      |       |     |        |

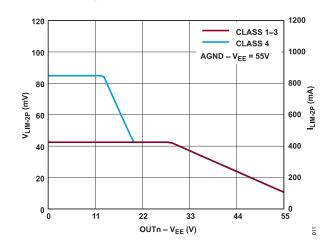

| V <sub>LIM-2P</sub>      | Active Current Limit                                    | OUTn – V <sub>EE</sub> < 10V                                                                          |          |      |       |     |        |

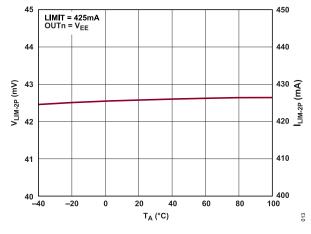

|                          |                                                         | Class 1 to Class 3                                                                                    | *        | 40   | 42.5  | 45  | mV     |

|                          |                                                         | Class 4                                                                                               | *        | 80   | 85    | 90  | mV     |

| VINRUSH-2P               | Active Current Limit, Inrush                            | OUTn – V <sub>EE</sub> < 30V (Note 15)                                                                | *        | 40   | 42.5  | 45  | mV     |

| V <sub>HOLD-2P</sub>     | DC Disconnect Sense Voltage                             | SENSEn – VSSKn                                                                                        | *        | 500  | 700   | 900 | μV     |

| V <sub>SC</sub>          | Short-Circuit Sense                                     | SENSEn – VSSKn – V <sub>LIM-2P</sub>                                                                  |          |      | 60    |     | mV     |

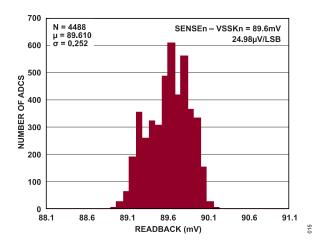

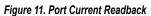

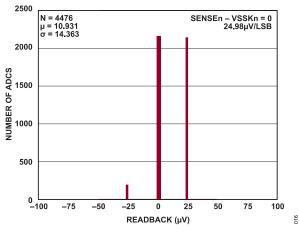

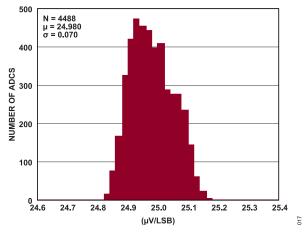

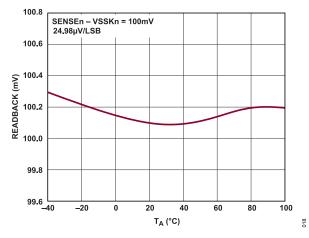

| Port Current I           | Readback (See Typical Performance Characteristics, Note | 16)                                                                                                   |          |      |       |     | 1      |

|                          | Full-Scale Range                                        | (Notes 7, 15)                                                                                         |          |      | 204.6 |     | mV     |

|                          | LSB Weight                                              | SENSEn – VSSKn , VSSKn = V <sub>EE</sub> (Note 14)                                                    |          |      | 24.98 |     | µV/LSE |

|                          | Conversion Period                                       |                                                                                                       |          |      | 1.967 |     | ms     |

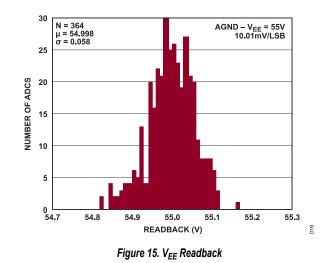

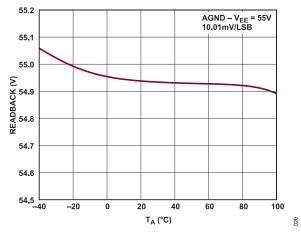

| V <sub>EE</sub> Readback | (See Typical Performance Characteristics, Note 16)      | 1                                                                                                     |          |      |       |     |        |

|                          | Full-Scale Range                                        | (Note 7)                                                                                              |          |      | 82    |     | V      |

|                          | LSB Weight                                              | AGND – V <sub>EE</sub>                                                                                |          |      | 10.01 |     | mV/LSE |

|                          | Conversion Period                                       |                                                                                                       |          |      | 1.967 |     | ms     |

| Digital Interfa          | Ce                                                      |                                                                                                       |          | 1    |       |     |        |

| VILD                     | Digital Input Low Voltage                               | ADn, RESET, OSS, CFGn (Note 6)                                                                        | *        |      |       | 0.8 | V      |

|                          | I <sup>2</sup> C Input Low Voltage                      | SCL, SDAIN (Note 6)                                                                                   | *        |      |       | 1   | V      |

| VIHD                     | Digital Input High Voltage                              |                                                                                                       | *        | 2.2  |       |     | V      |

|                          | Digital Output Low Voltage                              | I <sub>SDAOUT</sub> = 3mA, I <sub>INT</sub> = 3mA                                                     | *        |      |       | 0.4 | V      |

|                          |                                                         | $I_{SDAOUT} = 5mA, I_{INT} = 5mA$                                                                     | *        |      |       | 0.7 | V      |

|                          | Internal Pull-Up to V <sub>DD</sub>                     | ADn, RESET, OSS                                                                                       |          |      | 50    |     | kΩ     |

|                          | Internal Pull-Down to DGND                              | CFG0                                                                                                  |          |      | 50    |     | kΩ     |

|                          | EXT3 Pull-Down to V <sub>EE</sub>                       |                                                                                                       |          |      | 50    |     | kΩ     |

|                          | IDn Internal Pull-Up to CAP4                            | IDn = 0V                                                                                              |          |      | 5     |     | μΑ     |

| PSF Timing C             | haracteristics (Note 7)                                 |                                                                                                       |          |      | -     |     | I      |

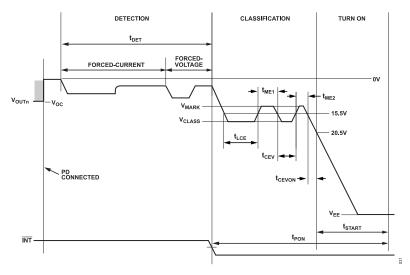

| t <sub>DET</sub>         | Detection Time                                          | Beginning to End of Detection                                                                         | *        |      | 380   | 500 | ms     |

| t <sub>CLASS_RESET</sub> | Classification Reset Duration                           |                                                                                                       | *        | 15   |       |     | ms     |

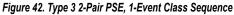

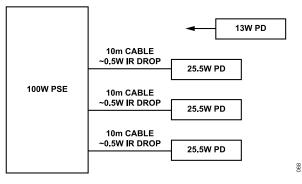

| t <sub>CEV</sub>         | Class Event Duration                                    |                                                                                                       | *        | 6    | 15    | 20  | ms     |

|                          | Class Event Turn On Duration                            | C <sub>PORT</sub> = 0.6µF                                                                             | *        |      |       | 0.1 | ms     |

|                          | Long Class Event Duration                               | OPORT COM.                                                                                            | *        | 88   |       | 105 | ms     |

| t <sub>CLASS</sub>       | Class Event I <sub>CLASS</sub> Measurement Timing       |                                                                                                       | *        | 6    |       |     | ms     |

| tCLASS_LCE               | Long Class Event I <sub>CLASS</sub> Measurement Timing  |                                                                                                       | *        | 6    |       | 75  | ms     |

| tclass_acs               | Autoclass I <sub>CLASS</sub> Measurement Timing         |                                                                                                       | *        | 88   |       | 105 | ms     |

| t <sub>ME1</sub>         | Mark Event Duration (Except Last Mark Event)            | (Note 11)                                                                                             | *        | 6    | 9.6   | 12  | ms     |

| t <sub>ME2</sub>         | Last Mark Event Duration                                | (Note 11)                                                                                             | *        | 6    | 20    |     | ms     |

|                          | Power On Delay, Auto Mode                               | From End of Valid Detect to End of Valid Inrush                                                       | *        |      | 20    | 400 | ms     |

| tAUTO_PSE1               | Autoclass Power Measurement Start                       | From End of Valid Deceder to End of Valid Inden<br>From End of Inrush to Beginning of Autoclass Power | *        | 1.4  |       | 1.6 | s      |

| AUTU_PSET                |                                                         | Measurement                                                                                           |          |      |       | 1.0 |        |

| t <sub>AUTO_PSE2</sub>   | Autoclass Power Measurement End                         | From End of Inrush to End of Autoclass Power Measurement                                              | *        | 3.1  |       | 3.5 | S      |

| t <sub>AUTO WINDOW</sub> | Autoclass Average Power Sliding Window                  |                                                                                                       | *        | 0.15 | 0.23  | 0.3 | S      |

| t <sub>ED</sub>          | Fault Delay                                             | From Power On Fault to Next Detect                                                                    | *        | 1.0  | 1.3   | 1.8 | S      |

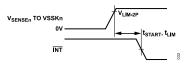

| t <sub>START</sub>       | Maximum Current Limit Duration During Inrush            |                                                                                                       | *        | 50   | 60    | 75  | ms     |

| t <sub>LIM</sub>         | Maximum Current Limit Duration After Inrush             | (Note 12)                                                                                             |          |      |       |     |        |

|                          |                                                         | $t_{\text{LIMn}} = 0 \times 0$                                                                        |          | 50   |       |     | ms     |

|                          |                                                         | $t_{\text{LIM}} = 0x1$                                                                                | $\vdash$ | 15   |       |     | ms     |

|                          |                                                         | $t_{\text{LIM}} = 0.2$                                                                                | $\vdash$ | 10   | 15    | 22  | ms     |

#### Table 4. (Continued)

| SYMBOL                     | PARAMETER                                              | CONDITIONS                                             |   | MIN | TYP | MAX | UNITS |

|----------------------------|--------------------------------------------------------|--------------------------------------------------------|---|-----|-----|-----|-------|

|                            |                                                        | t <sub>LIMn</sub> = 0x3                                |   | 6   | 11  | 17  | ms    |

| t <sub>MPS</sub>           | Maintain Power Signature (MPS) Pulse Width Sensitivity | Current Pulse Width to Reset Disconnect Timer (Note 8) | * |     |     | 6   | ms    |

| t <sub>DIS</sub>           | Maintain Power Signature (MPS) Dropout Time            | (Note 5)                                               | * | 320 | 370 | 400 | ms    |

| t <sub>BIT</sub>           | Bit Duration                                           |                                                        | * | 24  | 25  | 26  | μs    |

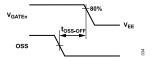

| t <sub>oss-off</sub>       | Shutdown Priority Delay                                |                                                        | * |     | 6.5 | 10  | μs    |

| t <sub>r_OSS</sub>         | OSS Rise Time                                          |                                                        | * | 1   |     | 300 | ns    |

| t <sub>f_OSS</sub>         | OSS Fall Time                                          |                                                        | * | 1   |     | 300 | ns    |

| t <sub>oss_IDL</sub>       | OSS Idle Time                                          |                                                        |   |     | 50  |     | μs    |

|                            | I <sup>2</sup> C Watchdog Timer Duration               |                                                        | * | 1.5 | 2   | 3   | s     |

|                            | Minimum Pulse Width for Masked Shutdown                |                                                        | * | 3   |     |     | μs    |

|                            | Minimum Pulse Width for RESET                          |                                                        | * | 4.5 |     |     | μs    |

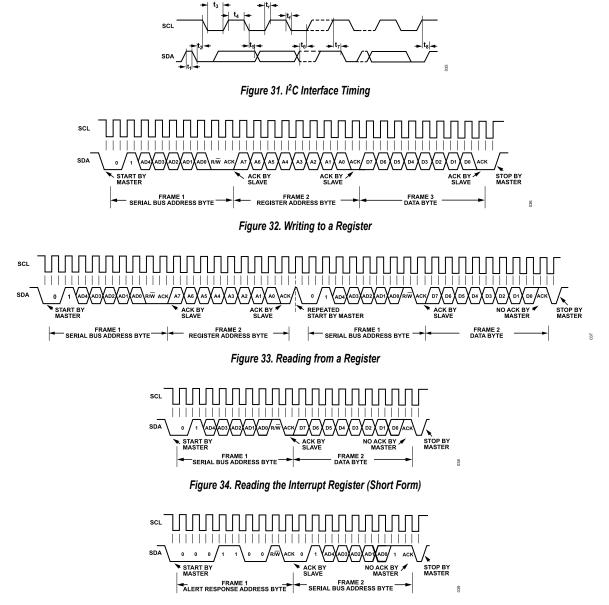

| I <sup>2</sup> C Timing (I | Note 7)                                                |                                                        |   |     |     |     |       |

| f <sub>SCLK</sub>          | Clock Frequency                                        |                                                        | * |     |     | 1   | MHz   |

| t <sub>1</sub>             | Bus Free Time                                          | Figure 31 (Note 9)                                     | * | 480 |     |     | ns    |

| t <sub>2</sub>             | Start Hold Time                                        | Figure 31 (Note 9)                                     | * | 240 |     |     | ns    |

| t <sub>3</sub>             | SCL Low Time                                           | Figure 31 (Note 9)                                     | * | 480 |     |     | ns    |

| t <sub>4</sub>             | SCL High Time                                          | Figure 31 (Note 9)                                     | * | 240 |     |     | ns    |

| t <sub>5</sub>             | SDAIN Data Hold Time                                   | Figure 31 (Note 9)                                     | * | 60  |     |     | ns    |

|                            | Data Clock to SDAOUT Valid                             | Figure 31 (Note 9)                                     | * |     |     | 250 | ns    |

| t <sub>6</sub>             | Data Set-Up Time                                       | Figure 31 (Note 9)                                     | * | 80  |     |     | ns    |

| t <sub>7</sub>             | Start Set-Up Time                                      | Figure 31 (Note 9)                                     | * | 240 |     |     | ns    |

| t <sub>8</sub>             | Stop Set-Up Time                                       | Figure 31 (Note 9)                                     | * | 240 |     |     | ns    |

| t <sub>r</sub>             | SCL, SDAIN Rise Time                                   | Figure 31 (Note 9)                                     | * |     |     | 120 | ns    |

| t <sub>f</sub>             | SCL, SDAIN Fall Time                                   | Figure 31 (Note 9)                                     | * |     |     | 60  | ns    |

|                            | Fault Present to INT Pin Low                           | (Notes 9, 10)                                          | * |     |     | 150 | ns    |

|                            | Stop Condition to INT Pin Low                          | (Notes 9, 10)                                          | * |     |     | 1.5 | μs    |

|                            | ARA to INT Pin High Time                               | (Note 9)                                               | * |     |     | 1.5 | μs    |

|                            | SCL Fall to ACK Low                                    | (Note 9)                                               | * |     |     | 250 | ns    |

**Note 1**: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifespan.

**Note 2**: This chipset includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 140°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 3: All currents into device pins are positive; all currents out of device pins are negative.

**Note 4**: The LTC9102 operates with a negative supply voltage (with respect to AGND). To avoid confusion, voltages in this data sheet are referred to in terms of absolute magnitude.

Note 5: t<sub>DIS</sub> is the same as t<sub>MPDO</sub> defined by IEEE 802.3.

Note 6: The LTC9101-2B digital interface operates with respect to DGND. All logic levels are measured with respect to DGND.

Note 7: Guaranteed by design, not subject to test.

**Note 8**: The IEEE 802.3 defines MPS as the set of minimum PSE and PD input current requirements to maintain power. An LTC9101-2B/ LTC9102 port resets its MPS timer when  $V_{SENSEn} - VSSKn \ge V_{HOLD-2P}$  for  $t_{MPS}$  and removes port power when  $V_{SENSEn} - VSSKn \ge V_{HOLD-2P}$  for a period longer than  $t_{DIS}$ . See the Disconnect section.

**Note 9**: Values Measured at V<sub>IHD</sub>.

analog.com

Note 10: If a fault condition occurs during an I<sup>2</sup>C transaction, the INT pin will not be pulled down until a stop condition is present on the I<sup>2</sup>C bus.

Note 11: Load characteristics of the LTC9102 during Mark: 7V < (AGND - V<sub>OUTn</sub>) < 10V

Note 12: See the LTC9101-2B Software Interface guide for information on serial bus usage and device configuration and status registers.

Note 13: Do not source or sink current from CAP1, CAP2, CAP3 and CAP4.

Note 14: Port current and port power measurements depend on sense resistor value (0.1Ω typical). See the External Component Selection section for details.

Note 15: See the Inrush Control section for details on inrush threshold selection.

**Note 16:** ADC characteristics and typical performance are described in terms of LTC9102 hardware capability. Measurements from LTC9102 are processed and synthesized by the LTC9101-2B. See LTC9101-2B Software Interface guide for register descriptions and LSB weights, as presented to the user (port current, port voltage, V<sub>EE</sub> voltage, and system temperature).

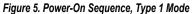

Figure 7. Inrush Current Limit (Note 15)

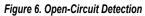

Figure 8. Power-On Current Limits

Figure 9. ILIM-2P vs. Temperature

Figure 12. Port Current Readback Offset

Figure 13. Port Current Readback LSB

Figure 14. Port Current Readback vs. Temperature

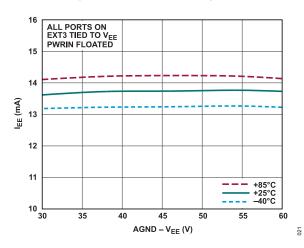

Figure 17. V<sub>EE</sub> Supply Current (I<sub>EE</sub>) vs. Voltage and Temperature

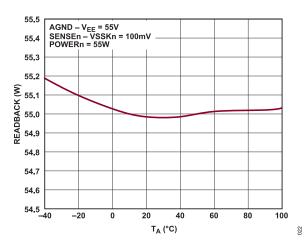

Figure 18. Port Power Monitor Accuracy vs. Temperature

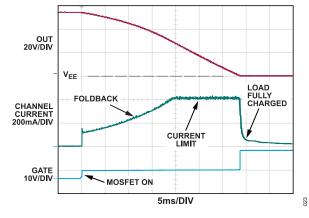

Figure 19. Powering Up into 180µF

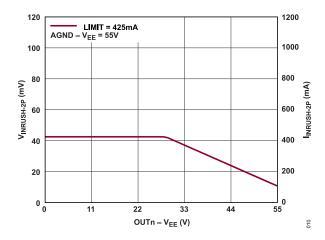

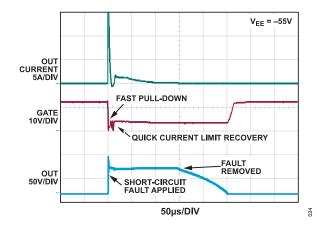

Figure 20. Short-Circuit Recovery

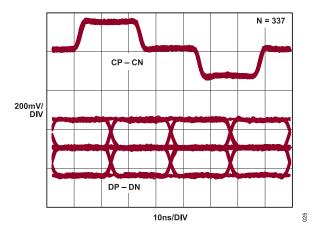

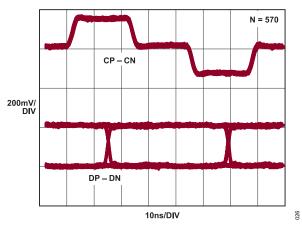

Figure 21. Clock and Data Write Eye Diagram

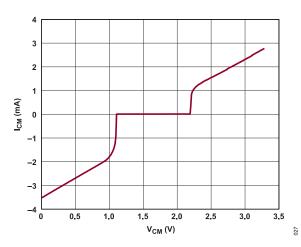

Figure 23. LTC9102 CP/CN and DP/DN Common-Mode Correction Current

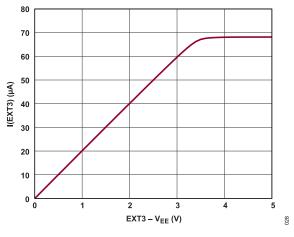

Figure 24. EXT3 Pin Current vs. Voltage

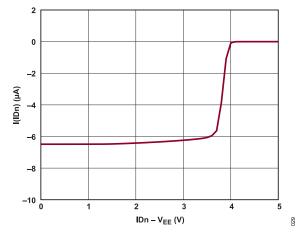

Figure 25. IDn Pin Current vs. Voltage

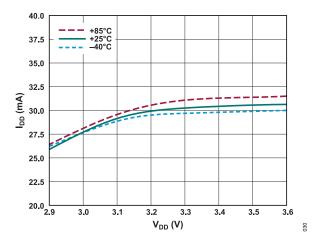

Figure 26. V<sub>DD</sub> Supply Current (I<sub>DD</sub>) vs. Voltage and Temperature

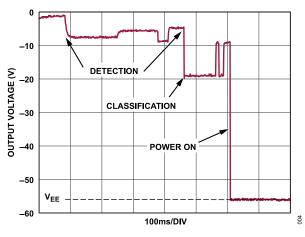

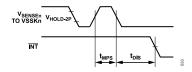

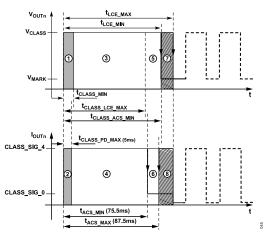

#### **TEST TIMING DIAGRAMS**

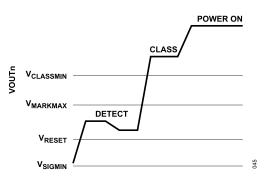

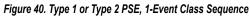

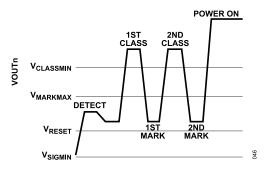

Figure 27. Detect, Class, and Turn-On Timing, Auto or Semi-Auto Modes

Figure 28. Current Limit Timings

Figure 29. DC Disconnect Timing

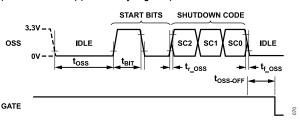

Figure 30. One-Bit Shutdown Priority Timing

#### **TEST TIMING DIAGRAMS**

## I<sup>2</sup>C TIMING DIAGRAMS

Figure 35. Reading from Alert Response Address

## **PIN FUNCTIONS**

| Pin No.                    | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC9101-2B                 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pins 2, 1<br>Respectively  | CFG[1:0]        | Device Configuration Inputs. Tie the<br>configuration pins high or low to set the<br>number of connected LTC9102 devices.<br>See the Device Configuration section<br>for additional details.                                                                                                                                                                                                                                                                                                            |

| Pins 7, 23<br>Respectively | CAP[2:1]        | Core Power Supply Bypass Capacitors.<br>Connect each pin to a $1\mu$ F capacitance<br>to DGND for the internal 1.2V regulator<br>bypass. Do not use other capacitor<br>values. Do not source or sink current<br>from this pin.                                                                                                                                                                                                                                                                          |

| Pin 8                      | CPD             | Clock Transceiver Positive Input Output<br>(Digital). Connect to CPA through a data<br>transformer.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin 9                      | CND             | Clock Transceiver Negative Input<br>Output (Digital). Connect to CNA<br>through a data transformer.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin 10                     | DPD             | Data Transceiver Positive Input Output<br>(Digital). Connect to DPA through a data<br>transformer.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pin 11                     | DND             | Data Transceiver Negative Input Output<br>(Digital). Connect to DNA through a<br>data transformer.                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pins 12, 19, 24            | V <sub>DD</sub> | $\label{eq:VDD} \begin{array}{l} V_{DD} \mbox{ IO Power Supply. Connect to} \\ a 3.3V \mbox{ power supply relative to} \\ DGND. Each V_{DD} \mbox{ pin must be locally} \\ bypassed with at least a 0.1 \mbox{$\mu$F$} \\ capacitor. A 10 \mbox{$\mu$F$} \mbox{ bulk capacitor must} \\ \mbox{ be connected across } V_{DD} \mbox{ for increased} \\ \mbox{ surge immunity.} \end{array}$                                                                                                               |

| Pin 14                     | RESET           | Reset Input, Active Low. When RESET<br>is low, the LTC9101-2B/LTC9102 is<br>held inactive with all ports off and all<br>internal registers reset. When RESET is<br>pulled high, the LTC9101-2B/LTC9102<br>begins normal operation. RESET can<br>be connected to an external capacitor<br>or RC network to provide a power<br>turn-on delay. Internal filtering of<br>RESET prevents glitches less than 1µs<br>wide from resetting the LTC9101-2B/<br>LTC9102. Internally pulled up to V <sub>DD</sub> . |

| Pin 15                     | ĪNT             | Interrupt Output, Open Drain. INT will<br>pull low when any one of several<br>events occur in the LTC9101-2B. It<br>will return to a high impedance state<br>when bits 6 or 7 are set in the Reset<br>register. The INT signal can be used<br>to generate an interrupt to the host<br>processor, eliminating the need for<br>continuous software polling. Individual<br>INT events can be disabled using the<br>Int Mask register. See LTC9101-2B<br>Software Interface guide documentation             |

| LTC91 | 01-2B/l | TC9102 |

|-------|---------|--------|

|       |         |        |

| Pin No.                          | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |          | for more information. INT is only updated between I <sup>2</sup> C transactions.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pin 16                           | SDAOUT   | Serial Data Output, Open Drain Data<br>Output for the I <sup>2</sup> C Serial Interface<br>Bus. The LTC9101-2B uses two pins<br>to implement the bidirectional SDA<br>function to simplify opto isolation<br>of the I <sup>2</sup> C bus. To implement a<br>standard bidirectional SDA pin, tie<br>SDAOUT and SDAIN together. See<br>the Applications Information section for<br>additional details.                                                                                                                                   |

| Pin 17                           | SDAIN    | Serial Data Input. High impedance<br>data input for the I <sup>2</sup> C serial interface<br>bus. The LTC9101-2B uses two pins<br>to implement the bidirectional SDA<br>function to simplify opto isolation<br>of the I <sup>2</sup> C bus. To implement a<br>standard bidirectional SDA pin, tie<br>SDAOUT and SDAIN together. See<br>the Applications Information section for<br>additional details.                                                                                                                                 |

| Pin 18                           | SCL      | Serial Clock Input. High impedance<br>clock input for the I <sup>2</sup> C serial interface<br>bus. The SCL pin should be connected<br>directly to the I <sup>2</sup> C SCL bus line. SCL<br>must be tied high if the I <sup>2</sup> C serial<br>interface bus is not used.                                                                                                                                                                                                                                                            |

| Pin 20                           | OSS      | Maskable Shutdown Input, Active High.<br>Supports both 1-bit shutdown priority<br>and 3-bit shutdown priority. See the<br>Over Supply Shutdown (OSS) section<br>for additional details. Internally pulled<br>down to DGND.                                                                                                                                                                                                                                                                                                             |

| Pins 21, 6, 5, 3<br>Respectively | AD[4:1]  | I <sup>2</sup> C Address Bits 4 to 1. Tie the address<br>pins high or low to set the base I <sup>2</sup> C<br>serial address. The base address will b<br>(01A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> 0b). Internally pulled up to<br>V <sub>DD</sub> . See the Bus Addressing section<br>for additional details.                                                                                                                                                                                                    |

| Pins 22, 25                      | DGND     | Digital Ground. DGND should be<br>connected to the return from the V <sub>DD</sub><br>supply.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LTC9102                          |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin 1                            | САРЗ     | Analog Internal 3.3V Power Supply<br>Bypass Capacitor. Connect a 1µF<br>ceramic cap to V <sub>EE</sub> . A 3.3V power<br>supply may be connected to this pin<br>to improve power supply efficiency. The<br>EXT3 pin must be pulled to CAP3 to<br>shut off the internal 3.3V regulator if<br>power is supplied externally. Do not<br>source or sink current from this pin. Do<br>not connect to CAP3 except as explicitly<br>instructed in ADI documentation (e.g.,<br>strapping LTC9102 pins and terminating<br>the serial interface). |

## **PIN FUNCTIONS**

| Pin No.                                                                  | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin 2                                                                    | EXT3        | External 3.3V Enable. Connect the<br>EXT3 pin to CAP3 to shut off the<br>internal 3.3V regulator when power is<br>supplied externally. Float or connect to<br>V <sub>EE</sub> for internal regulator operation.                                                                                                                                                                                                                                                                                                               |

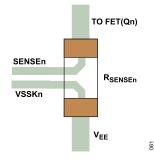

| Pins 47, 46, 39, 38,<br>31, 30, 23, 22, 15,<br>14, 7, 6<br>Respectively  | VSSK[12:1]  | Kelvin Sense to $V_{EE}$ . Connect to $V_{EE}$<br>side of sense resistor for channel n<br>through a 0.1 $\Omega$ resistor. Do not connect<br>directly to $V_{EE}$ plane. See the Kelvin<br>Sense section for requirements.                                                                                                                                                                                                                                                                                                    |

| Pins 48, 45, 40, 37,<br>32, 29, 24, 21, 16,<br>13, 8, 5<br>Respectively  | SENSE[12:1] | Current Sense Input, channel n.<br>SENSEn monitors the external<br>MOSFET current via a $0.1\Omega$ sense<br>resistor between SENSEn and VSSKn.<br>If the voltage across the sense resistor<br>reaches the current limit threshold<br>I <sub>LIM-2P</sub> , the GATEn pin voltage is<br>lowered to maintain constant current<br>in the external MOSFET. See the<br>Applications Information section for<br>additional details. If the channel is<br>unused, tie SENSEn to V <sub>EE</sub> .                                   |

| Pins 49, 44, 41, 36,<br>33, 28, 25, 20, 17,<br>12, 9, 4<br>Respectively  | OUT[12:1]   | Output Voltage Monitor, channel n.<br>Connect OUTn to the output channel.<br>A current limit foldback circuit limits<br>the power dissipation in the external<br>MOSFET by reducing the current limit<br>threshold when the drain-to-source<br>voltage exceeds 10V. A port power<br>good event is raised when the voltage<br>from OUTn to $V_{EE}$ drops below 2.4V<br>(typ). A 500k resistor is connected<br>internally from OUTn to AGND when the<br>channel is idle. If the channel is unused,<br>the OUTn pin must float. |

| Pins 50, 43, 42, 35,<br>34, 27, 26, 19, 18,<br>11, 10, 3<br>Respectively | GATE[12:1]  | Gate Drive, channel n. Connect GATEn to the gate of the external MOSFET for channel n. When the MOSFET is turned on, the gate voltage is driven to 12V (typ) above $V_{EE}$ . During a current limit condition, the voltage at GATEn will be reduced to maintain constant current through the external MOSFET. If the fault timer expires, GATEn is pulled down, turning the MOSFET off and raising a port fault event. If the channel is unused, the GATEn pin must float.                                                   |

| Pins 52, 51<br>Respectively                                              | ID[1:0]     | Transceiver ID. Sets the address of the LTC9102 on the multidrop high-speed data interface. ID numbering must start at 00b. Tie high by connecting to CAP3. Tie low by connecting to $V_{\text{EE}}$ . See the Device Configuration section for additional details.                                                                                                                                                                                                                                                           |

| Pin 55                                                                   | PWRIN       | Startup Regulator Bypass and External<br>Low Voltage Supply Input. Power for the                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin No.                                          | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                 | internal 4.3V and 3.3V internal supplies<br>An internal regulator maintains the<br>voltage of this pin above 6V. An externa<br>resistor or supply may be connected<br>to this node to improve the power<br>efficiency of the LTC9102. Connect a<br>1µF capacitor between this pin and V <sub>EE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin 56                                           | AGND            | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Pins 57, 58<br>Respectively                      | PWRMD[1:0]      | Maximum Power Mode Input. Connect<br>PWRMD0 of the LTC9102 with ID[1:0] :<br>00b to V <sub>EE</sub> with configuration resistor<br>R <sub>PWRMD</sub> . When the LTC9101-2B is<br>reset, R <sub>PWRMD</sub> selects initial maximum<br>power allocation values for every port<br>in the chipset; the system power<br>supply must be sized to support all<br>ports outputting up to R <sub>PWRMD</sub> . When<br>auto mode is enabled, the chipset<br>runs independently as a PoE PSE.<br>The chipset detects and classes all<br>ports, granting power to each port<br>up to R <sub>PWRMD</sub> setting. The PWRMD0<br>pin of LTC9102 with ID pins set<br>to 01b, 10b, and 11b must be left<br>floating. The PWRMD1 pin of all<br>LTC9102 must be left floating. See<br>the Auto Mode Maximum PSE Power<br>section for R <sub>PWRMD</sub> options and details<br>The PWRMD pins are ignored when<br>a custom configuration package is<br>present. See the Stored Configurations<br>section for additional details. |

| Pin 59                                           | CAP4            | Analog Internal 4.3V Power Supply<br>Bypass Capacitor. Connect a $1\mu$ F<br>ceramic cap to V <sub>EE</sub> . Do not source or<br>sink current from this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pins 60, 65                                      | V <sub>EE</sub> | Main PoE Supply Input. Connect to a<br>-51V to -57V supply, relative to AGND<br>Voltage depends on PSE Type (Type 3<br>or 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Pin 61                                           | DNA             | Data Transceiver Negative Input Outpu<br>(Analog). Connect to DND through a<br>data transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin 62                                           | DPA             | Data Transceiver Positive Input Output<br>(Analog). Connect to DPD through a<br>data transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin 63                                           | CNA             | Clock Transceiver Negative Input<br>Output (Analog). Connect to CND<br>through a data transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Pin 64                                           | CPA             | Clock Transceiver Positive Input Outpu<br>(Analog). Connect to CPD through a<br>data transformer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Common Pins                                      |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LTC9101-2B Pins<br>4, 13; LTC9102<br>Pins 53, 54 | NC, DNC         | All pins identified with "NC" or "DNC" must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## OVERVIEW

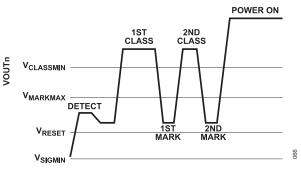

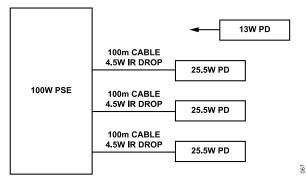

Power over Ethernet, or PoE, is a standard protocol for sending DC power over copper Ethernet data wiring. The IEEE group that administers the 802.3 Ethernet data standards added PoE powering capability in 2003. This original PoE standard, known as 802.3af, allowed for 48V DC power at up to 13W. 802.3af was widely popular, but 13W was not adequate for some applications. In 2009, the IEEE released a new standard, known as 802.3at or PoE+, increasing the voltage and current requirements to provide 25.5W of delivered power. IEEE 802.3af and 802.3at are commonly known as PoE 1. In 2018, the IEEE released the latest PoE standard, known as 802.3bt or PoE 2. 802.3bt maximizes PD delivered power at 71.3W.

The IEEE standard also defines PoE terminology. A device that provides power to the network is known as a PSE, or power sourcing equipment, while a device that draws power from the network is known as a PD, or powered device. PSEs come in two types: endpoints (typically network switches or routers), which provide data and power; and midspans, which provide power but pass through data. Midspans are typically used to add PoE capability to existing non-PoE networks. PDs are typically IP phones, wireless access points, security cameras, and similar devices.

## **PoE++** Evolution

Even during the development of the IEEE 802.3at (PoE 1) 25.5W standard, it became clear there was a significant and increasing need for more than 25.5W of delivered power. In 2013, the 802.3bt task force was formed to develop a standard capable of increasing delivered PD power.

The primary objective of the task force was to use all four pairs of the Ethernet cable as opposed to the two pair power utilized by 802.3at. Using all four pairs allows for at least twice the delivered power over existing Ethernet cables. Further, the amount of current per two pairs (known as a pairset) is increased while maintaining the Ethernet data signal integrity. 802.3bt increases PD delivered power from 25.5W to 71.3W, enabling IEEE-compliant high power PD applications.

The LTC9101-2B/LTC9102 is a 2-pair device, delivering power to each port over one pairset. Each pairset is driven by a dedicated power channel. In this data sheet, the term channel refers to the PSE circuitry assigned to a corresponding pairset. For the purposes of this document, the terms channel and pairset may be considered interchangeable.

In addition, IEEE 802.3bt enables substantially lower Maintain Power Signature (MPS) currents, resulting in significantly lower standby power consumption. This allows new and emerging government or industry standby regulations to be met using standard PoE components.

## LTC9101-2B/LTC9102 Product Overview

The LTC9101-2B/LTC9102 is a sixth generation PSE controller that implements up to 48 (25.5W) 2-pair PSE ports in either an endpoint or midspan application. Virtually all necessary circuitry is included to implement an IEEE 802.3bt-compliant PSE design, requiring an external power MOSFET and sense resistor per port; these minimize power loss compared to alternative designs with onboard MOSFETs, and increase system reliability.

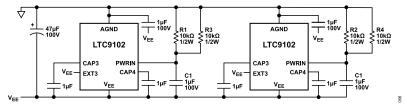

The LTC9101-2B/LTC9102 chipset implements an optional proprietary isolation scheme for inter-chip communication. This architecture substantially reduces BOM cost by replacing expensive opto-isolators and isolated power supplies with a single low-cost transformer. A single LTC9101-2B is capable of controlling a bus of up to 4 LTC9102s over this transformer-isolated interface. Direct connection of the LTC9101-2B and the associated LTC9102s is also possible.

The LTC9101-2B/LTC9102 offers a configurable interrupt signal triggered by per-port events, per-channel power on control and fault telemetry, per-channel current monitoring, V<sub>EE</sub> monitoring, and 100ms rolling current and voltage averaging.

The LTC9101-2B/LTC9102 also offers advanced sixth-generation PSE features including internal eFlash for storage of firmware updates and custom user configuration packages, 802.3at/bt-compliant mode select, l<sup>2</sup>C quad virtualization for full backwards-compatibility with quad-based IC drivers, ultra-low 100m $\Omega$  sense resistors, +80V/–20V tolerant port-facing pins, and improvements to cable surge ride through.

Each LTC9102 power channel includes dedicated detection and classification hardware. This allows all ports and channels to detect, classify and power on simultaneously, drastically reducing power on latency across a switch. Other less-advanced PSEs are subject to visible delays as PDs, e.g. LED lights, power on a port-by-port basis.

$V_{\text{EE}}$  and port current measurements are performed simultaneously, enabling coherent and precise per-port power monitoring.

## 802.3BT 2-PAIR OPERATION

The LTC9101-2B includes up to 12 groups of four identical channels. Each group of four channels is referred to as a quad. In the LTC9101-2B architecture, each quad contains register configuration and status for exactly four channels and provides control for four 2-pair 802.3bt ports.

In 2-pair mode, the IEEE 802.3bt standard supports delivered power up to 25.5W, supporting PDs requesting Class 4 power or lower. High-power single-signature PDs (Class 5 and above) and dual-signature PDs are demoted to Class 4 (25.5W) power and receive power over a single pairset.

#### 802.3at Type 1 Mode

All 802.3bt-compliant PSEs are fully backwards compatible with existing 802.3at Type 1 and Type 2 PDs as shown in Table 5.

In addition to full compatibility, 802.3bt PSEs extend support for lower standby power, enhanced current limit timing, and dynamic power management to all PD Types (as supported by the PD application).

The LTC9101-2B further supports 802.3af compliant port operation. In the rare event an 802.3af PD is incompatible with 802.3bt operation, a 15W, No CC mode is supported in the cfg2p4p register.

Note that an 802.3at PSE will not pass an 802.3bt PSE compliance test, and an 802.3bt PSE will not pass an 802.3at PSE compliance test. This is by design of the respective standards. 802.3at and 802.3bt devices are designed to be interoperable. Key features of 802.3at and 802.3bt standards are contrasted in Table 6.

Table 5. PSE Maximum Delivered Power, Per-Port<sup>1</sup>

| DEVICE |          |      | PSE              |                    |                    |                  |       |  |  |  |

|--------|----------|------|------------------|--------------------|--------------------|------------------|-------|--|--|--|

|        | STANDARD |      | 802              | .3at               | 802.3bt            |                  |       |  |  |  |

|        |          | TYPE | 1                | 2                  | 3 (2-<br>Pair)     | 3 (4-<br>Pair)   | 4     |  |  |  |

| PD     | 802.3at  | 1    | 13W              | 13W                | 13W                | 13W              | 13W   |  |  |  |

|        |          | 2    | 13W <sup>1</sup> | 25.5W              | 25.5W              | 25.5W            | 25.5W |  |  |  |

|        | 802.3bt  | 3    | 13W <sup>1</sup> | 25.5W <sup>1</sup> | 25.5W <sup>1</sup> | 51W              | 51W   |  |  |  |

|        |          | 4    | 13W <sup>1</sup> | 25.5W <sup>1</sup> | 25.5W <sup>1</sup> | 51W <sup>1</sup> | 71.3W |  |  |  |

<sup>1</sup> Indicates PD may be allocated less power than requested (demoted).

#### Table 6. 802.3at Type 1 vs 802.3bt Features

| FEATURE                     | 802.3at (Type 1)       | 802.3bt         |  |

|-----------------------------|------------------------|-----------------|--|

| First Class Event           | Short                  | Long            |  |

| First Mark Event (15W Mode) | No                     | Yes             |  |

| Limit Timer                 | No (Uses Cutoff Timer) | Yes             |  |

| Connection Check            | No                     | 2-Pair: No      |  |

|                             |                        | 4-Pair: Yes     |  |

| Active Alternative(s)       | A or B                 | 2-Pair: A or B  |  |

|                             |                        | 4-Pair: A and B |  |

| Maximum Class Events        | 1                      | 2-Pair: 2       |  |

|                             |                        | 4-Pair: 5       |  |

| Maximum Available Power     | Class 3                | 2-Pair: Class 4 |  |