# ADIN3310/ADIN6310

# Industrial Ethernet Time Sensitive Networking Switch

#### **FEATURES**

- ▶ Ethernet MAC interfaces: 10 Mb, 100 Mb or 1 Gb per port

- ▶ 6-port: 4x RMII/RGMII/SGMII and 2x RMII/RGMII

- ▶ 3-port: 2x RMII/RGMII/SGMII and 1x RMII/RGMII

- ▶ SGMII, 1000BASE-SX/1000BASE-LX/1000BASE-KX, and 100BASE-FX

- ▶ Low Latency, Layer 2 Ethernet switch

- ▶ Deterministic latency from port to port

- ► Cut-through or store and forward operation

- ▶ Traffic types and bridge delay per IEEE/IEC 60802

- ▶ Standard bridging per IEEE 802.1Q-2018 (tailored)

- ▶ Each port is nonblocking and independent

- ▶ 32 kB frame buffer per transmit port

- ▶ 4096 VLANs

- ▶ Time synchronization

- ▶ IEEE 802.1AS-2020

- ▶ IEEE 1588-2019 default profile

- ▶ IEEE C37.238-2017 energy profile<sup>2</sup>

- ▶ 8 ns timestamp resolution

- ▶ Frames timestamped on ingress or egress

- ▶ IEEE 802.1Q time sensitive networking bridging

- Qbv: enhancements for scheduled traffic

- Qci: per stream filtering and policing

- ▶ Qbu: frame preemption

- Qch: cyclic queuing and forwarding

- ▶ Qav: forwarding and queuing enhancement<sup>2</sup>

- ▶ Qcc: stream reservation protocol enhancements<sup>2</sup>

- Number of streams

- ▶ 16000 TSN Layer 2 streams

- ▶ 256 extended lookup streams (IPV4, IPV6, PCP, and so on)

- ▶ PROFINET SendList control

- High availability and redundancy

- ▶ IEEE 802.1CB Frame Replication and Elimination for Reliability

- ▶ IEC62439-3:2016-03 HSR-/PRP-Compliant Protocol for Seamless Failover

- ▶ IEC62439-3-2021-12 Media Redundancy Protocol

- ► Custom Layer 2 on two ports for PROFINET IRT, EtherNet/IP beacon-based DLR, POWERLINK (100 Mbps)<sup>2</sup>

- Packet assist engine offloads host and manages TSN and switch features

- ▶ Portable C drivers for TSN and industrial Ethernet protocols

- Standard not finalized.

- Future software capability.

#### Rev. A

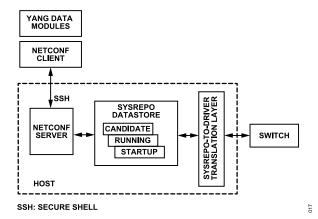

- ▶ NETCONF support (driver to Sysrepo translation layer)

- ▶ Hardware root of trust based security features

- ► Secure boot, secure update with anti-rollback

- Hardware-based cryptography

- Secure host pairing Protocol

- Cryptographic authenticity checking

- Interfaces to external host processor

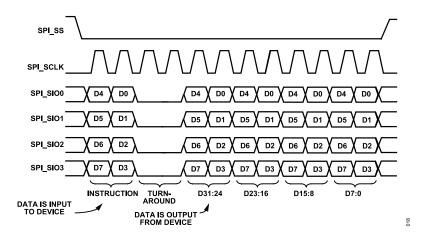

- ► RMII, RGMII, SGMII, SPI, dual SPI, or Quad SPI

- ▶ Power

- 3 external power supplies: 1.1 V, 3.3 V, and VDDIO\_x (1.8 V, 2.5 V, or 3.3 V)

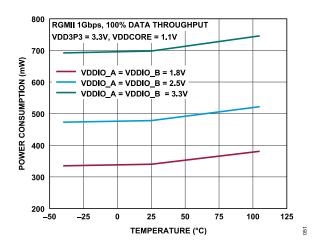

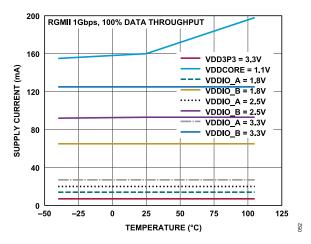

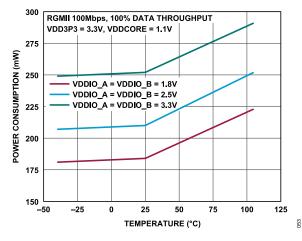

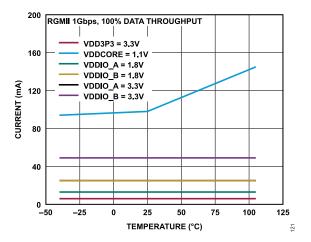

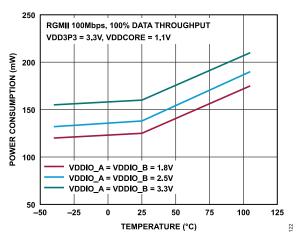

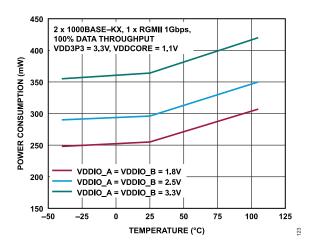

- ▶ Total chip power 60 mW per port at 1 Gbps, full utilization with VDDIO B = 1.8 V

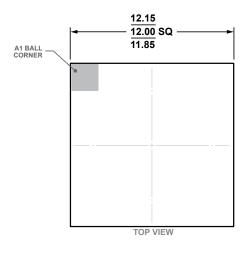

- Package and temperature range

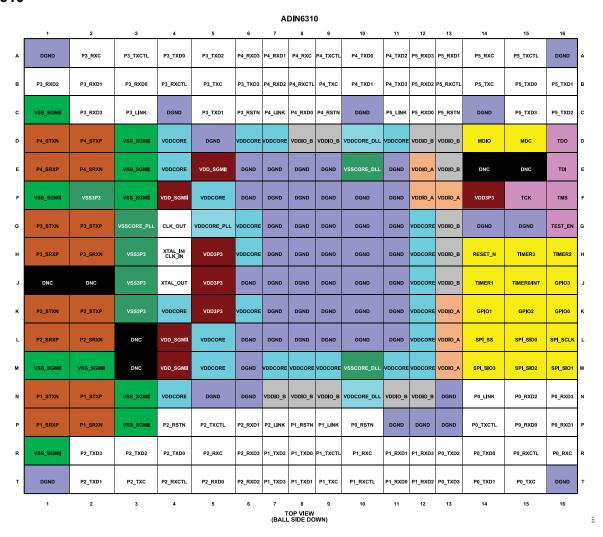

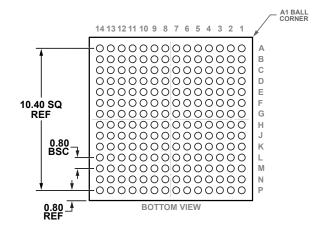

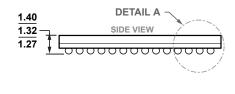

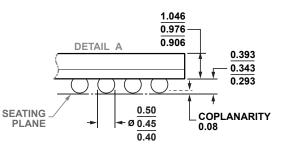

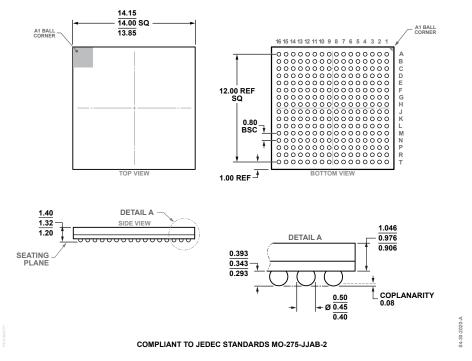

- ▶ 256-ball CSP BGA, 14 mm × 14 mm, 0.8 mm pitch

- ▶ 196-ball CSP BGA, 12 mm × 12 mm, 0.8 mm pitch

- ► Temperature range -40°C to +85 or -40°C to 105°C

#### **APPLICATIONS**

- ▶ Factory and process automation

- ▶ Motion control, robots, and cobots

- Energy automation

- ▶ Transportation

- Instrumentation

- Building automation

## **GENERAL DESCRIPTION**

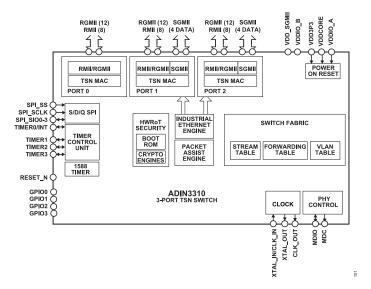

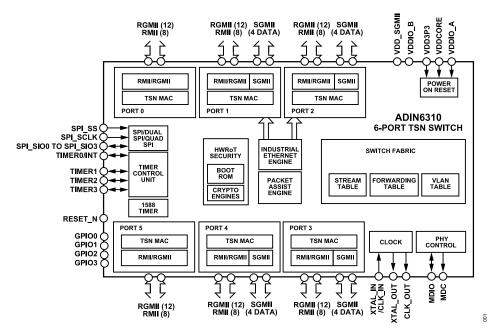

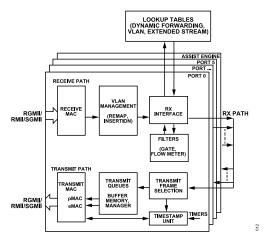

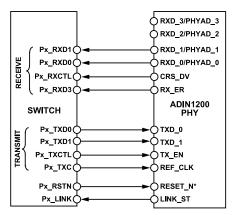

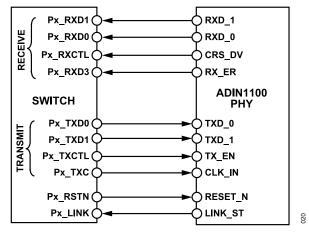

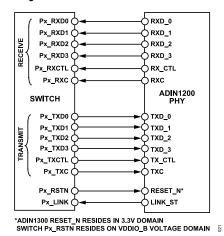

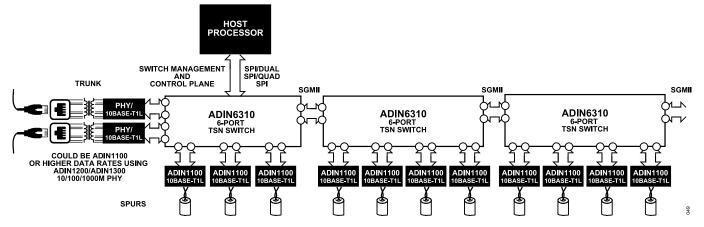

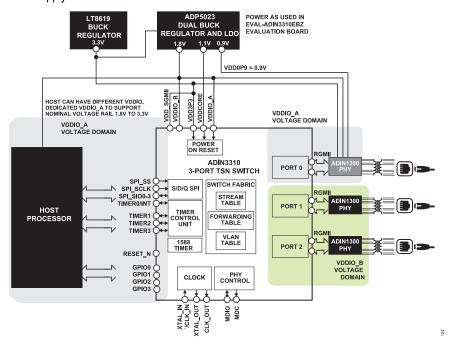

The ADIN3310 and ADIN6310 are 3-port and 6-port Gigabit Ethernet time sensitive networking (TSN) switches with integrated security primarily designed for industrial Ethernet applications. Each port can be configured to operate at different speeds. These switches have uncommitted media access controller (MAC) interfaces and can be paired with Analog Devices, Inc., physical (PHY) layer devices such as ADIN1100, ADIN1200, and ADIN1300, to form a low power, low latency system. Four serial gigabit media independent interface (SGMII) and serializer/deserializer (serdes) interfaces allow backplane connections, connectivity to SFP modules and cascade switches. The switch supports the suite of IEEE 802.1Q time sensitive networking bridging features required by IEEE 60802 standard providing quality of service (QoS) for latency sensitive streams. The device also includes hardware capability to support parallel redundancy protocol (PRP) or high availability seamless redundancy (HSR) redundancy protocols, thereby offloading the host processor.

| Features                               | 1   | GPIO                                    |    |

|----------------------------------------|-----|-----------------------------------------|----|

| Applications                           | 1   | Hardware RESET                          |    |

| General Description                    | 1   | Clocking                                | 53 |

| Functional Block Diagram               | 6   | Power Architecture                      | 54 |

| Specifications                         | 7   | Power Supplies and Supply Domains       |    |

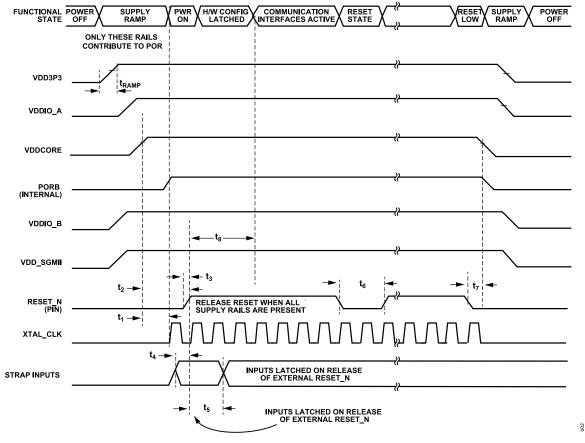

| Timing Characteristics                 | 13  | Power-On Reset (POR)                    | 54 |

| Power-Up, Power-Down, and Reset Timing | J13 | Power Supply Sequencing                 | 54 |

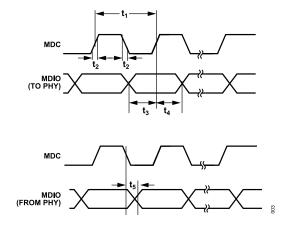

| Management Interface Timing            | 14  | Grounding                               | 54 |

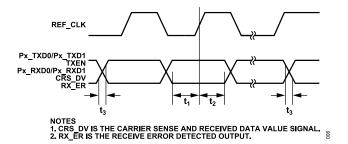

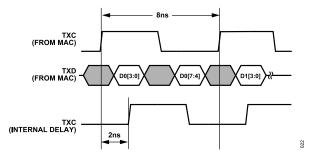

| RGMII Transmit and Receive Timing      | 15  | Power Consumption and Thermal           |    |

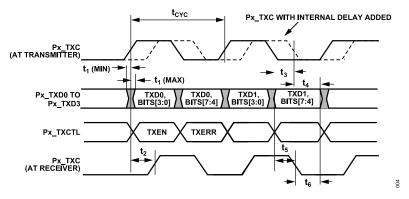

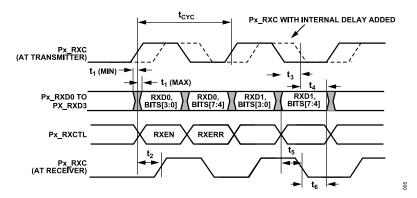

| RMII Transmit and Receive Timing       | 16  | Considerations                          | 55 |

| SGMII Serial Interface Transmit and    |     | Power Supply Decoupling                 | 55 |

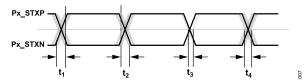

| Receive Timing                         | 17  | Time Synchronization                    |    |

| Serial Interface Timing                | 18  | Precision Time Protocol (PTP)           | 56 |

| Absolute Maximum Ratings               | 19  | Time Domains                            |    |

| Thermal Resistance                     | 19  | IEEE 802.1AS 2020                       | 56 |

| Electromagnetic Compatibility (EMC)    |     | IEEE 1588-2019 Default Profile          | 56 |

| Performance                            | 19  | IEEE C37.238.2017 Energy Profile        | 56 |

| Electrostatic Discharge (ESD) Ratings  | 20  | TSN Functionality                       | 57 |

| ESD Caution                            |     | Scheduled Traffic (IEEE 802.1Qbv)       | 57 |

| Pin Configuration and Pin Descriptions | 21  | Frame Preemption (IEEE 802.1Qbu)        | 57 |

| ADIN3310                               | 21  | Per Stream Filtering and Policing (IEEE |    |

| ADIN6310                               | 25  | 802.1Qci)                               | 59 |

| Typical Performance Characteristics    | 31  | Cyclic Queuing and Forwarding (IEEE     |    |

| Theory of Operation                    | 33  | 802.1Qch)                               | 59 |

| Switch Overview                        | 33  | Forwarding and Queuing Enhancements     |    |

| Port Overview                          | 33  | (IEEE 802.1Qav)                         | 59 |

| Storm Protection                       | 34  | SendList                                | 61 |

| Switch Fabric                          | 34  | SendList Example                        |    |

| Lookup Tables                          | 34  | Redundancy                              | 62 |

| Types of Lookups                       | 36  | High-Availability Seamless Redundancy   |    |

| Buffer Management                      | 37  | (HSR)                                   | 62 |

| Quality of Service (QoS)               | 38  | HSR Port Modes                          | 63 |

| Congestion Control                     | 38  | HSR Statistics                          | 64 |

| Port Forwarding Mask                   | 38  | Parallel Redundancy Protocol (PRP)      | 64 |

| Ethernet Frame                         | 38  | PRP Statistics                          |    |

| Switch Latency                         | 40  | Hybrid HSR and PRP Networks             | 66 |

| Receive and Transmit Port Statistics   | 41  | Frame Replication and Elimination for   |    |

| Packet Assist Engine                   | 42  | Reliability, IEEE 802.1CB               | 66 |

| Software Running on the Switch         | 42  | Media Redundancy Protocol (MRP)         | 67 |

| Firmware Update                        |     | Other Functionality                     |    |

| NETCONF                                | 43  | Industrial Ethernet Engine              | 70 |

| Interfaces                             | 44  | Logical MAC Operation                   | 70 |

| Serial Interface, SPI                  |     | Layer 2 Transmit and Receive            | 71 |

| PHY MDC and MDIO Interface             | 46  | Event Subscription                      | 71 |

| Ethernet Interfaces                    | 47  | Link Layer Discovery Protocol (LLDP)    | 72 |

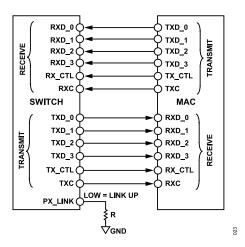

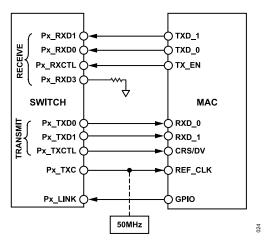

| MAC to MAC Interface                   | 49  | IGMP Snooping                           |    |

| Host Interface                         |     | Port Mirroring                          | 72 |

| Host Interface Strapping Pins          |     | Multiple Spanning Tree Protocol         | 72 |

| TIMER Inputs and Outputs               | 52  | Applications Information                | 74 |

|                                        |     |                                         |    |

| Application Circuit Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74         | Silicon Anomaly    | 83 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|----|

| Application Use Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 76         | Outline Dimensions | 85 |

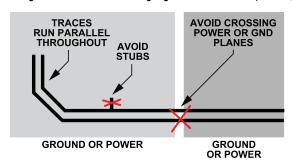

| Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81         | Ordering Guide     | 86 |

| General Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 81         | Evaluation Boards  | 86 |

| Component Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 81         |                    |    |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                    |    |

| 1/2025—Rev. 0 to Rev. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                    |    |

| Added ADIN3310 (Universal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                    |    |

| Changes to Features Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                    |    |

| Changes to General Description Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                    |    |

| Added Figure 1; Renumbered Sequentia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                    |    |

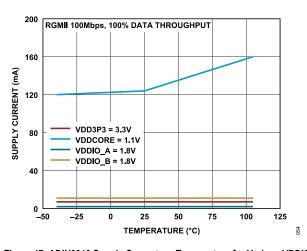

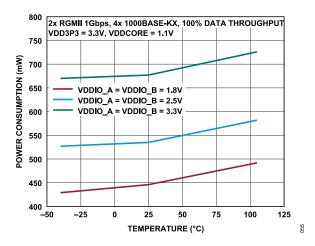

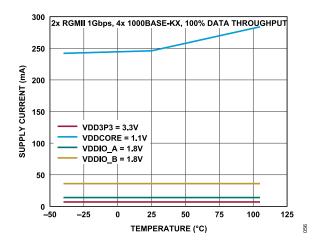

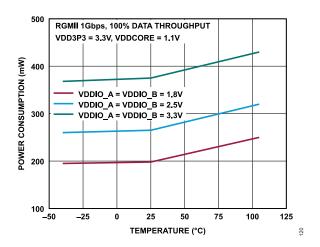

| Added ADIN3310 Current and Power Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -          |                    |    |

| Changes to Table 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                    |    |

| Changes to Table 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                    |    |

| Changes to Electromagnetic Compatibility Change to Table 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • '        |                    |    |

| Added ESD Ratings for ADIN3310 Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                    |    |

| Added ADIN3310 Section, Figure 12, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                    |    |

| Changes to Table 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                    |    |

| Changes to Figure 14 Caption to Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                    |    |

| Added Figure 20 to Figure 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                    |    |

| Changes to Switch Overview Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                    |    |

| Changes to Port Overview Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                    |    |

| Changes to Switch Fabric Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                    |    |

| Changes to Stream Lookup Table Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                    |    |

| Changes to VLAN Table and Manageme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                    |    |

| Changes to Buffer Management Section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                    |    |

| Changes to Quality of Service (QoS) Sec                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ction      |                    | 38 |

| Added Congestion Control Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                    | 38 |

| Changes to Table 16 and Table 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                    |    |

| Changes to Packet Assist Engine Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                    | 42 |

| Changes to Software Running on the Sw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |                    |    |

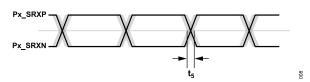

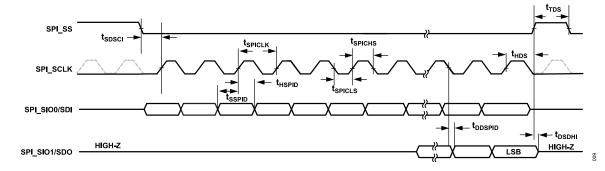

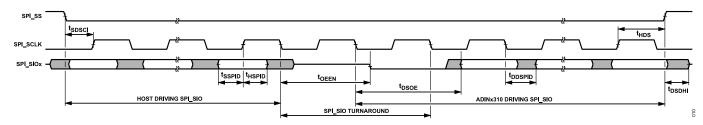

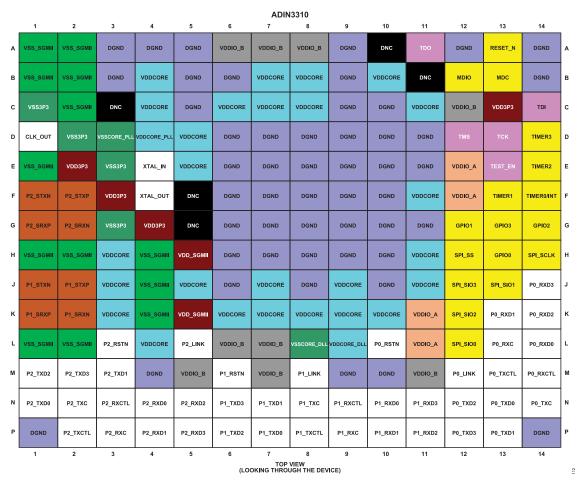

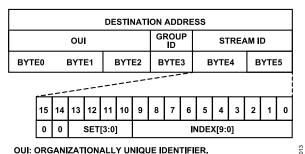

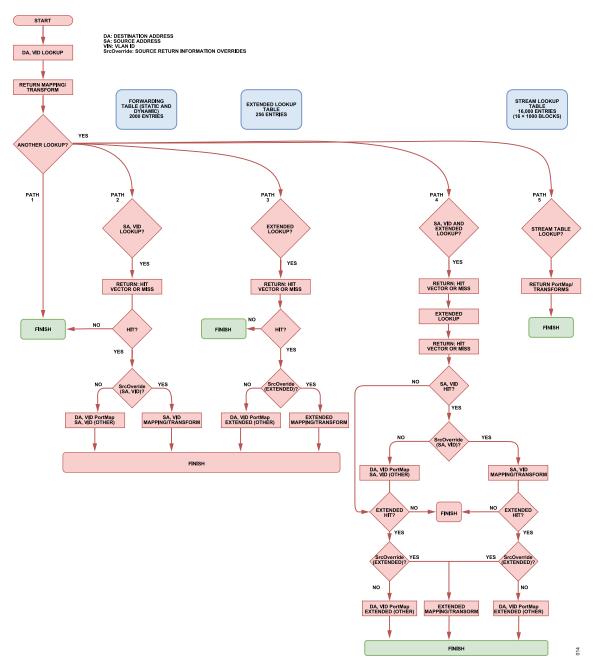

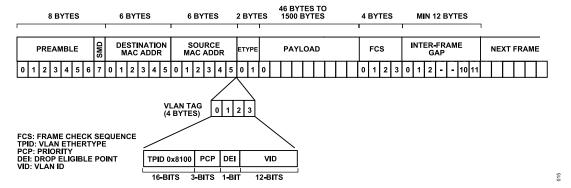

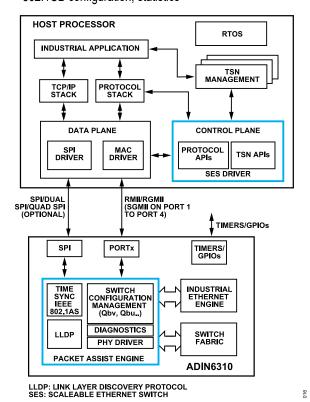

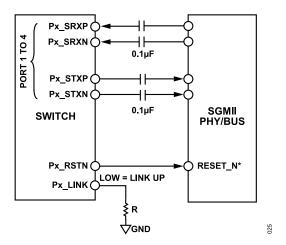

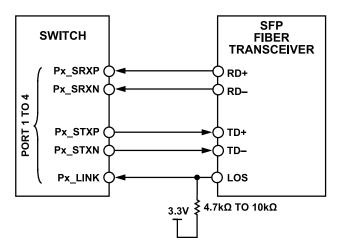

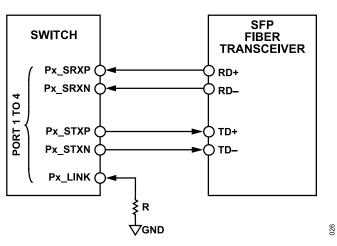

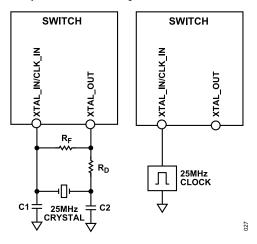

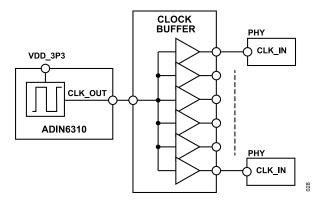

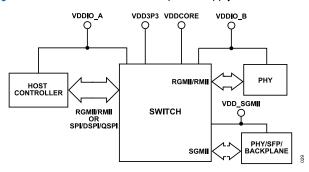

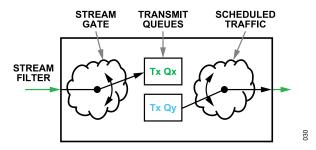

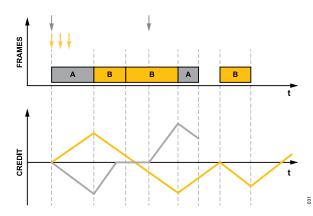

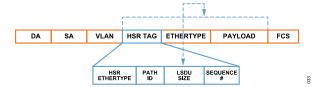

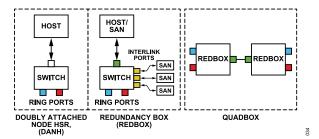

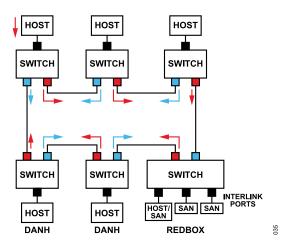

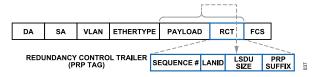

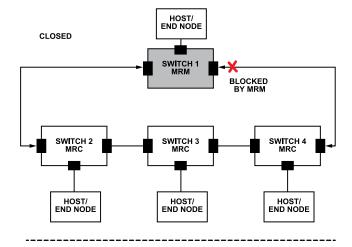

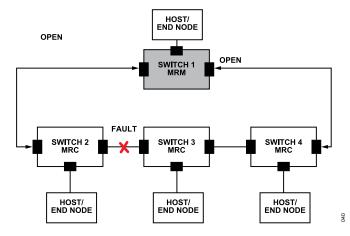

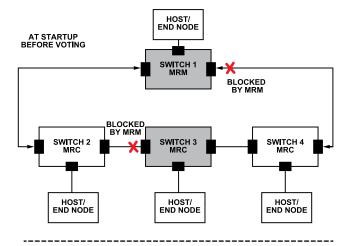

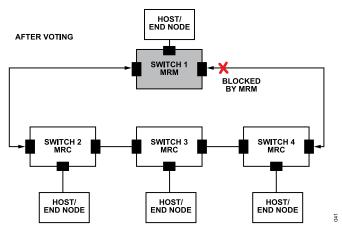

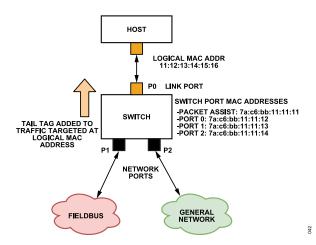

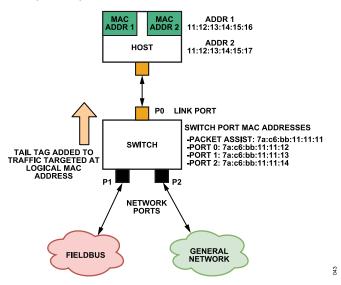

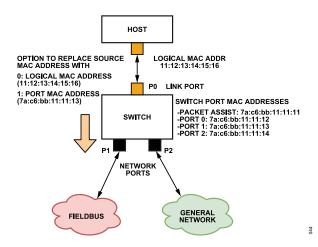

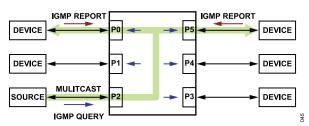

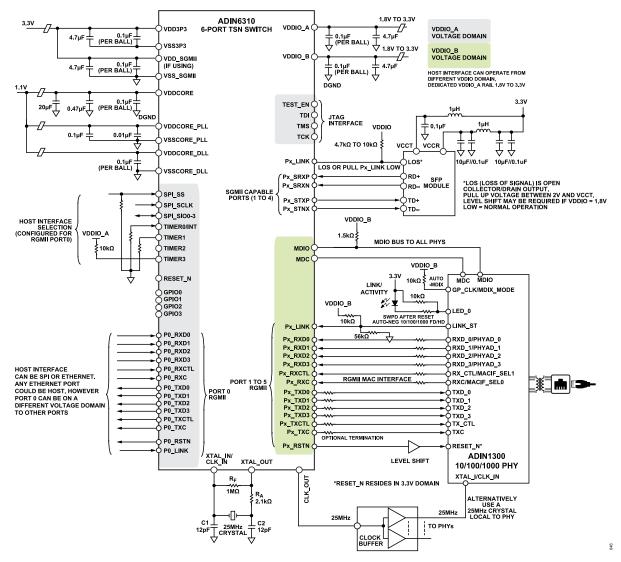

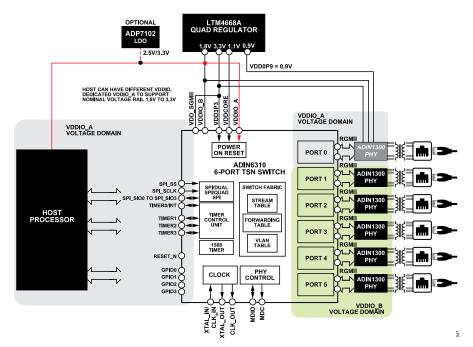

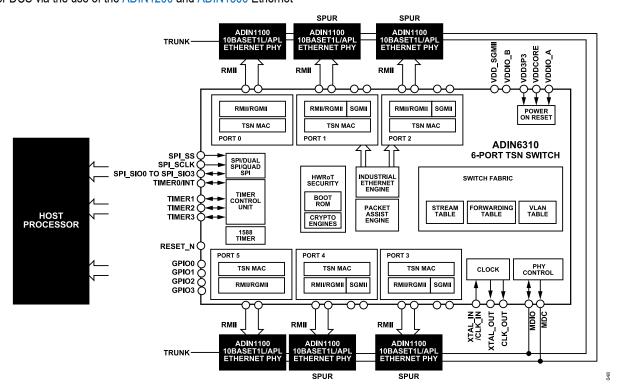

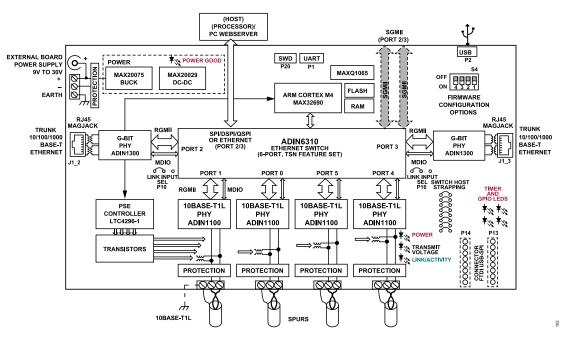

| Changes to Firmware Update Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                    |    |