# ADF4382

## Microwave Wideband Synthesizer with Integrated VCO

#### **FEATURES**

- Output frequency range: 687.5 MHz to 22 GHz

- Integrated RMS jitter at 20 GHz = 20 fs (integration bandwidth: 100 Hz to 100 MHz)

- Integrated RMS jitter at 20 GHz = 31 fs (ADC SNR method)

- VCO fast calibration time < 1 µs</p>

- ▶ VCO autocalibration time < 100 µs

- ▶ Phase noise floor: -156 dBc/Hz at 20 GHz

- PLL specifications

- ▶ -239 dBc/Hz: normalized in-band phase noise floor

- ► -287 dBc/Hz: normalized 1/f phase noise floor

- 625 MHz maximum phase/frequency detector input frequency

- ▶ 4.5 GHz reference input frequency

- ▶ Typical spurious f<sub>PFD</sub>: -90 dBc

- Reference to output delay specifications

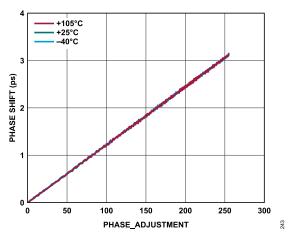

- ▶ Propagation delay temperature coefficient: 0.06 ps/°C

- Adjustment step size: <1 ps</p>

- Multichip output phase alignment

- ▶ 3.3 V and 5 V power supplies

- ► ADIsimPLL<sup>™</sup> loop filter design tool support

- ▶ 7 mm × 7 mm, 48-terminal LGA

- ▶ -40°C to +105°C operating temperature

#### **APPLICATIONS**

- High performance data converter clocking

- Wireless infrastructure (MC-GSM, 5G, 6G)

- Test and measurement

#### **GENERAL DESCRIPTION**

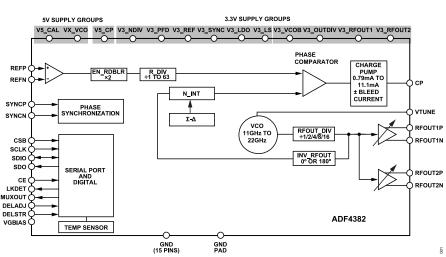

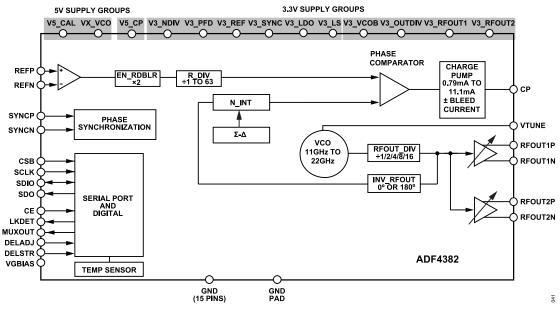

The ADF4382 is a high performance, ultra-low jitter, fractional-N phased-locked loop (PLL) with an integrated voltage controlled oscillator (VCO) ideally suited for local oscillator (LO) generation for 5G applications or data converter clock applications. The high performance PLL has a figure of merit of −239 dBc/Hz, low 1/f noise and high PFD frequency of 625 MHz in integer mode that can achieve ultra-low in-band noise and integrated jitter. The ADF4382 can generate frequencies in a fundamental octave range of 11 GHz to 22 GHz, thereby eliminating the need for subharmonic filters. The output dividers on the ADF4382 allow a complete output frequency range to be generated from 687.5 MHz to 22 GHz.

For multiple data converter clock applications, the ADF4382 automatically aligns its output to the input reference edge by including the output divider in the PLL feedback loop. For applications that require deterministic delay or delay adjustment capability, a programmable reference to output delay with <1 ps resolution is provided. The reference to output delay matching across multiple devices and over temperature allows predictable and precise multichip alignment.

The simplicity of the ADF4382 block diagram eases development time with a simplified serial peripheral interface (SPI) register map, external SYNC input, and repeatable multichip alignment in both integer and fractional mode.

#### FUNCTIONAL BLOCK DIAGRAM

Rev. 0 DOCUMENT FEEDBACK

**TECHNICAL SUPPORT**

Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| 1 |

|---|

| 1 |

| 1 |

| 1 |

| 3 |

| 7 |

| 8 |

| 9 |

| 9 |

| 9 |

| 9 |

| 9 |

| 0 |

| 2 |

| 0 |

| 0 |

| 1 |

| 2 |

|   |

## **REVISION HISTORY**

12/2024—Revision 0: Initial Version

| Applications Information                 | 33 |

|------------------------------------------|----|

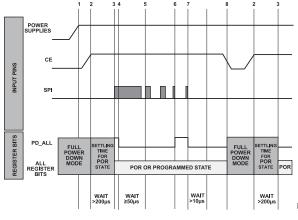

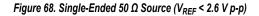

| Power-Up and Initialization Sequence     | 33 |

| Loop Filter Design                       | 35 |

| Loop Filter Layout Considerations        |    |

| Reference Source Considerations          |    |

| SYNC Input Network                       | 37 |

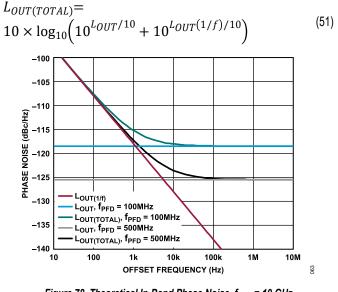

| Output Phase Noise Characteristics       | 37 |

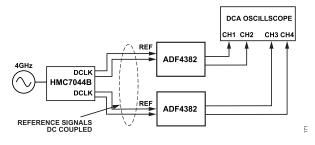

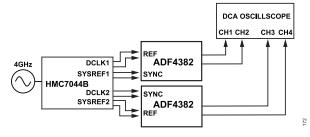

| Output Phase Synchronization of Multiple |    |

| ADF4382 Devices                          | 37 |

| Phase Synchronization Settings           | 39 |

| Phase Resynchronization                  | 40 |

| Σ-Δ Modulator Optimization Modes         | 41 |

| Register Map                             | 42 |

| Register Details                         |    |

| Outline Dimensions                       |    |

| Ordering Guide                           |    |

| Evaluation Boards                        |    |

|                                          |    |

3.3 V Supply Group 1 pins voltage ( $V_{3.3V_1}$ ) = 3.3 V Supply Group 2 pins voltage ( $V_{3.3V_2}$ ) = 3.15 V to 3.45 V, V5\_VCO voltage ( $V_{5V_VCO}$ ) = 5V\_CP voltage ( $V_{5V_CP}$ ) = 5V\_CAL voltage ( $V_{5V_CAL}$ ) = 4.75 V to 5.25 V, all voltages are with respect to GND, and  $T_A$  = -40°C to +105°C, operating temperature range, unless otherwise noted.

| Parameter                                      | Symbol           | Min | Тур   | Max  | Unit   | Test Conditions/Comments                                                                     |

|------------------------------------------------|------------------|-----|-------|------|--------|----------------------------------------------------------------------------------------------|

| REFERENCE INPUTS (REFP AND REFN)               |                  |     |       |      |        |                                                                                              |

| Input Frequency                                | f <sub>REF</sub> | 10  |       | 4500 | MHz    |                                                                                              |

| Input Signal Level                             | V <sub>REF</sub> | 0.5 |       | 2.6  | V р-р  | Refer to Figure 51                                                                           |

| Minimum Input Slew Rate                        |                  |     | 100   |      | V/µs   |                                                                                              |

| Input Duty Cycle                               |                  |     | 50    |      | %      |                                                                                              |

| Self Bias Voltage                              |                  |     | 1.85  |      | V      |                                                                                              |

| Input Resistance                               |                  |     | 3     |      | kΩ     | Differential                                                                                 |

| Input Capacitance                              |                  |     | 1     |      | pF     | Differential                                                                                 |

| Input Current                                  |                  |     | 2     |      | μA     |                                                                                              |

| REFERENCE PEAK DETECTOR                        |                  |     |       |      |        |                                                                                              |

| Input Frequency                                |                  | 10  |       | 4500 | MHz    |                                                                                              |

| Minimum Input Signal Detected (REF_OK = 1)     |                  |     | 200   |      | mV p-p | f <sub>REF</sub> = 100 MHz, single-ended sine wave                                           |

| Maximum Input Signal Not Detected (REF_OK = 0) |                  |     | 160   |      | mV p-p | f <sub>REF</sub> = 100 MHz, single-ended sine wave                                           |

| REFERENCE DIVIDER                              |                  | 1   |       | 63   |        | All integers included                                                                        |

| REFERENCE DOUBLER                              |                  |     |       |      |        |                                                                                              |

| Input Frequency                                |                  | 10  |       | 2000 | MHz    | EN_RDBLR = 1                                                                                 |

| PHASE/FREQUENCY DETECTOR (PFD)                 |                  |     |       |      |        |                                                                                              |

| Input Frequency                                | f <sub>PFD</sub> |     |       |      |        |                                                                                              |

| Integer Mode                                   |                  | 5.4 |       | 625  | MHz    | Integer mode, for all values of the N divider, excluding 15 and 28 to 31                     |

|                                                |                  | 5.4 |       | 540  | MHz    | For the N divider values 15 and 28 to 31                                                     |

| Fractional Mode                                |                  | 5.4 |       | 250  | MHz    | EFM3_MODE = 0 and EFM3_MODE = 4                                                              |

|                                                |                  | 5.4 |       | 220  | MHz    | EFM3_MODE = 5                                                                                |

| SYNCHRONIZATION INPUTS (SYNCP AND SYNCN)       |                  |     |       |      |        |                                                                                              |

| Input Signal Level                             | V <sub>REF</sub> | 0.4 |       | 2.6  | V р-р  | Low voltage differential signaling (LVDS) mode, differential                                 |

|                                                |                  | 0.5 |       | 2.6  | V р-р  | Current mode logic (CML) mode, differential                                                  |

| Self Bias Voltage                              |                  |     | 1.3   |      | V      | LVDS mode                                                                                    |

|                                                |                  |     | 1.85  |      | V      | CML mode                                                                                     |

| Synchronization to Reference Setup Time        |                  | 400 |       |      | ps     | Common-mode voltage (V <sub>CM</sub> ) set to self bias voltage, V <sub>CM</sub> = 0.8 V p-p |

| Synchronization to Reference Hold Time         |                  | 600 |       |      | ps     | $V_{CM}$ set to self bias voltage, $V_{CM}$ = 0.8 V p-p                                      |

| Input Resistance                               |                  |     | 3     |      | kΩ     | Differential                                                                                 |

| Input Capacitance                              |                  |     | 1     |      | pF     | Differential                                                                                 |

| Input Current                                  |                  |     | 3     |      | μA     |                                                                                              |

| CHARGE PUMP (CP)                               |                  |     |       |      |        |                                                                                              |

| Output Current                                 | I <sub>CP</sub>  |     |       |      |        |                                                                                              |

| Minimum                                        |                  |     | 0.79  |      | mA     | Set by the CP_I bit fields                                                                   |

| Maximum                                        |                  |     | 11.1  |      | mA     | Set by the CP_I bit fields                                                                   |

| Output Current Source and Sink                 |                  |     |       |      |        |                                                                                              |

| Accuracy                                       |                  |     | ±2    |      | %      | All setting, CP voltage ( $V_{CP}$ ) = $V_{CP}/2$                                            |

| Matching                                       |                  |     | ±2    |      | %      | All setting, $V_{CP} = V_{CP}/2$                                                             |

| Output Current vs. Output Voltage Sensitivity  |                  |     | 0.2   |      | % V/V  | V <sub>CP</sub> <sup>1</sup>                                                                 |

| Output Current vs. Temperature                 |                  |     | 280   |      | ppm/C  | $V_{CP} = V_{CP}/2$                                                                          |

| Output High-Z Leakage Current                  |                  |     | -0.01 |      | μA     | Minimum I <sub>CP</sub> , V <sub>CP1</sub>                                                   |

|                                                |                  |     | -0.3  |      | μA     | Maximum I <sub>CP</sub> , V <sub>CP1</sub>                                                   |

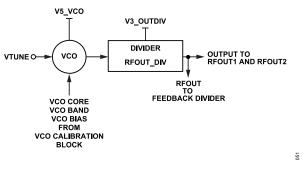

| Parameter                                                       | Symbol                                 | Min    | Тур                                | Мах   | Unit  | Test Conditions/Comments                                                                                                                                    |

|-----------------------------------------------------------------|----------------------------------------|--------|------------------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCO                                                             |                                        |        |                                    |       |       |                                                                                                                                                             |

| Fundamental Frequency Range                                     | f <sub>VCO</sub>                       | 11     |                                    | 22    | GHz   |                                                                                                                                                             |

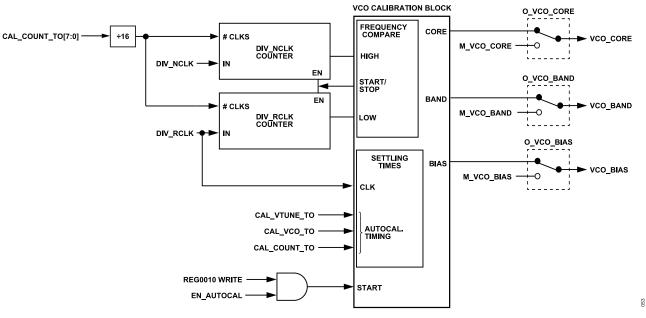

| VCO Autocalibration Time                                        |                                        |        | 100                                |       | μs    |                                                                                                                                                             |

| Tuning Sensitivity                                              | K <sub>VCO</sub>                       |        | 50 to 150                          |       | MHz/V | K <sub>VCO</sub> <sup>2,3</sup>                                                                                                                             |

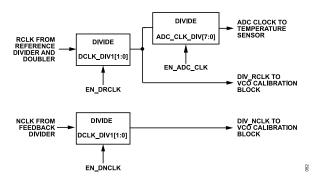

| Divided Reference Clock (DIV_RCLK) VCO<br>Calibration Frequency | f <sub>DIV_RCLK</sub>                  |        |                                    | 125   | MHz   | Must set DCLK_MODE = 1, when f <sub>DIV_RCLK</sub> > 80 MHz                                                                                                 |

| FEEDBACK (N) AND OUTPUT DIVIDER (O)                             |                                        |        |                                    |       |       |                                                                                                                                                             |

| Ν                                                               |                                        | 4      |                                    | 4095  |       | Integer mode                                                                                                                                                |

|                                                                 |                                        | 19     |                                    | 4095  |       | Fractional mode                                                                                                                                             |

| 0                                                               |                                        | 1      |                                    | 16    |       | 1, 2, 4, 8, and 16                                                                                                                                          |

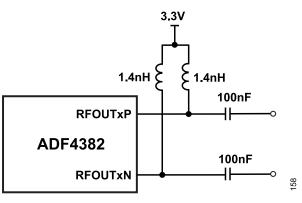

| RF OUTPUTS (RFOUT1P and RFOUT1N, RFOUT2P and RFOUT2N)           |                                        |        |                                    |       |       | Differential termination = $100 \Omega$ for all RF output (RFOUT) specifications unless otherwise noted                                                     |

| Output Frequency                                                | f <sub>OUT</sub>                       | 11     |                                    | 22    | GHz   |                                                                                                                                                             |

| Divide by 2                                                     |                                        | 5.5    |                                    | 11    | GHz   |                                                                                                                                                             |

| Divide by 4                                                     |                                        | 2.75   |                                    | 5.5   | GHz   |                                                                                                                                                             |

| Divide by 8                                                     |                                        | 1.375  |                                    | 2.75  | GHz   |                                                                                                                                                             |

| Divide by 16                                                    |                                        | 0.6875 |                                    | 1.375 | GHz   |                                                                                                                                                             |

| Differential RF Output Power                                    | P <sub>RFOUT</sub>                     |        | 10                                 |       | dBm   | RFOUT1_OPWR = RFOUT2_OPWR = 11,<br>f <sub>OUT</sub> = 11 GHz                                                                                                |

|                                                                 |                                        |        | 9                                  |       | dBm   | RFOUT1_OPWR = RFOUT2_OPWR = 11,<br>f <sub>OUT</sub> = 14 GHz                                                                                                |

|                                                                 |                                        |        | 5                                  |       | dBm   | RFOUT1_OPWR = RFOUT2_OPWR = 11,<br>$f_{OUT} = 20 \text{ GHz}$                                                                                               |

| Output Resistance                                               |                                        |        | 100                                |       | Ω     | Differential                                                                                                                                                |

| Output Common Mode                                              |                                        |        | 3.3 – V <sub>OD</sub> <sup>4</sup> |       | V     | Differentia                                                                                                                                                 |

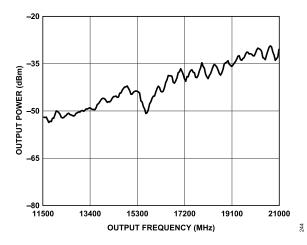

| Output Rise Time                                                | t <sub>R</sub>                         |        | 15                                 |       | ps    | 20% to 80%, RFOUT1_OPWR = RFOUT2_OPWR = 1                                                                                                                   |

| Output Fall Time                                                | t <sub>F</sub>                         |        | 15                                 |       | ps    | 80% to 20%, RFOUT1_OPWR =<br>RFOUT2_OPWR = 1                                                                                                                |

| Output Duty Cycle                                               |                                        |        | 50                                 |       | %     |                                                                                                                                                             |

| Skew, RFOUT1 to RFOUT2                                          |                                        |        | ±3                                 |       | ps    |                                                                                                                                                             |

| REFERENCE INPUT TO OUTPUT DELAY                                 |                                        |        |                                    |       |       | Device setup for all delay specifications<br>unless noted as follows, measure rising<br>reference edge at reference input to rising<br>edge at RFOUT output |

| Propagation Delay                                               | t <sub>PD</sub>                        |        | 190                                |       | ps    | REF_SEL = 0 and REF_SEL = 1                                                                                                                                 |

| Propagation Delay Temperature Coefficient                       | t <sub>PD-TC</sub>                     |        | 0.06                               |       | ps/°C | REF_SEL = 0                                                                                                                                                 |

| LOGIC INPUTS (CSB, SCLK, SDIO, DELADJ and DELSTR)               |                                        |        |                                    |       |       |                                                                                                                                                             |

| Input High Voltage                                              | V <sub>INH</sub>                       | 1.2    |                                    |       | V     |                                                                                                                                                             |

| Input Low Voltage                                               | V <sub>INL</sub>                       |        |                                    | 0.6   | V     |                                                                                                                                                             |

| Input Current                                                   | I <sub>IH</sub> /I <sub>IL</sub>       |        |                                    | ±1    | μA    |                                                                                                                                                             |

| Input Capacitance                                               | CIN                                    |        | 3                                  |       | pF    |                                                                                                                                                             |

| LOGIC INPUT (CE)                                                |                                        |        |                                    |       |       |                                                                                                                                                             |

| Input High Voltage                                              | V <sub>INH-3V</sub>                    | 1.8    |                                    |       | V     |                                                                                                                                                             |

| Input Low Voltage                                               | V <sub>INL-3V</sub>                    | -      |                                    | 0.8   | V     |                                                                                                                                                             |

| Input Current                                                   | I <sub>IH-3V</sub> /I <sub>IL-3V</sub> |        |                                    | ±1    | μA    |                                                                                                                                                             |

| Input Capacitance                                               | C <sub>IN-3V</sub>                     |        | 3                                  |       | pF    |                                                                                                                                                             |

| Parameter                                    | Symbol                           | Min                    | Тур        | Max  | Unit   | Test Conditions/Comments                                                                                                                           |

|----------------------------------------------|----------------------------------|------------------------|------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS (SDIO, SDO, LKDET, and MUXOUT) |                                  |                        |            |      |        |                                                                                                                                                    |

| Output High Voltage (1.8 V Mode)             | V <sub>OH-1.8V</sub>             | 1.5                    | 1.8        | 2    | V      | Output high current ( $I_{OH}$ ) = 500 µA, 1.8 V output selected (default setting)                                                                 |

| Output High Voltage (3.3 V Mode)             | V <sub>OH-3V</sub>               | V <sub>3.3V</sub> – 0. | 4          |      |        | I <sub>OH</sub> = 500 μA, 3.3 V output selected, set<br>by the voltage on the V3_LDO pin, and<br>CMOS_OV can set to either 1.8 V or 3.3 V<br>logic |

| Output Low Voltage                           | V <sub>OL</sub>                  |                        |            | 0.4  | V      | Output low current ( $I_{OL}$ ) = 500 µA                                                                                                           |

| SDO High-Z Leakage                           | I <sub>ZH</sub> /I <sub>ZL</sub> |                        |            | ±1   | μA     |                                                                                                                                                    |

| POWER SUPPLIES                               |                                  |                        |            |      |        | Device Setup is default configuration for all<br>Supply Current specifications unless noted<br>below.                                              |

| V5_VCO Supply Range                          | V <sub>V5_VCO</sub>              | 4.75                   | 5          | 5.25 | V      |                                                                                                                                                    |

| V5_CAL Supply Range                          | V <sub>V5 CAL</sub>              | 4.75                   | 5          | 5.25 | V      |                                                                                                                                                    |

| V5_CP Supply Range                           | V <sub>V5 CP</sub>               | 4.75                   | 5          | 5.25 | V      |                                                                                                                                                    |

| V <sub>3.3V_1</sub> Supply Range             | V <sub>3.3V_1</sub>              | 3.15                   | 3.3        | 3.45 | V      | Group 1: V3_LS, V3_LDO, V3_REF, V3_PFD, V3_NDIV, and V3_SYNC                                                                                       |

| V <sub>3.3V_2</sub> Supply Range             | V <sub>3.3V_2</sub>              | 3.15                   | 3.3        | 3.45 | V      | Group 2: V3_RFOUT1, V3_RFOUT2,<br>V3_VCO, and V3_OUTDIV                                                                                            |

| V5_VCO Supply Current                        | I <sub>5V_VCO</sub>              |                        | 140        | 195  | mA     | f <sub>OUT</sub> = 11 GHz to 22 GHz, RFOUT_DIV = 0,<br>maximum charge pump current                                                                 |

| V5_CAL Supply Current                        | I <sub>5V_CAL</sub>              |                        | 105        | 215  | μA     |                                                                                                                                                    |

|                                              |                                  |                        | 15         |      | mA     | During VCO calibration                                                                                                                             |

| V5_CP Supply Current                         | I <sub>5V_CP</sub>               |                        | 60         | 70   | mA     | I <sub>CP</sub> = 11.1 mA                                                                                                                          |

| V <sub>3.3V_1</sub> Supply Current           | I <sub>3.3V_1</sub>              |                        | 200        | 240  | mA     |                                                                                                                                                    |

| V <sub>3.3V_2</sub> Supply Current           | I <sub>3.3V_2</sub>              |                        | 310        | 340  | mA     | PD_RFOUT1 = 0, PD_RFOUT2 = 0,<br>RFOUT1_OPWR = 11, and RFOUT2_OPWR<br>= 11 (maximum power)                                                         |

| Typical Power Dissipation                    | P <sub>DIS</sub>                 |                        | 2.2 to 2.6 |      |        | PD_RFOUT1 = 1, PD_RFOUT2 = 0,<br>RFOUT1_OPWR = 11, and RFOUT2_OPWR<br>= 11 (maximum power)                                                         |

| Typical Power Down Current                   |                                  |                        |            |      |        |                                                                                                                                                    |

| 3.3 V                                        |                                  |                        | 3.1        |      | mA     | PD_ALL =1, I <sub>3.3V_1</sub> + I <sub>3.3V_2</sub>                                                                                               |

| 5 V                                          |                                  |                        | 340        |      | μA     | $PD\_ALL=1, I_{VCO-5V + I_{CAL-5V} + I_{CP-5V}}$                                                                                                   |

| Typical Disable Current                      |                                  |                        |            |      |        |                                                                                                                                                    |

| 3.3 V Supplies                               |                                  |                        | 710        |      | μA     | $CE = Iow, I_{3.3V_{1}} + I_{3.3V_{2}}$                                                                                                            |

| 5 V Supplies                                 |                                  |                        | 340        |      | μA     | $CE = Iow, I_{VCO-5V} + I_{CAL-5V} + I_{CP-5V}$                                                                                                    |

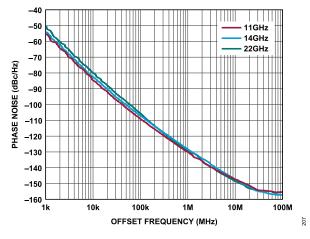

| RF OUTPUT NOISE CHARACTERISTICS              |                                  |                        |            |      |        |                                                                                                                                                    |

| RF Output = 20 GHz                           |                                  |                        |            |      |        | VCO noise in open-loop conditions, and offset<br>from 20 GHz carrier                                                                               |

| Phase Noise Floor                            |                                  |                        | -156       |      | dBc/Hz |                                                                                                                                                    |

| 100 KHz Offset                               |                                  |                        | -103       |      | dBc/Hz |                                                                                                                                                    |

| 1 MHz Offset                                 |                                  |                        | -125       |      | dBc/Hz |                                                                                                                                                    |

| 10 MHz Offset                                |                                  |                        | -144       |      | dBc/Hz |                                                                                                                                                    |

| RF Output = 14 GHz                           |                                  |                        |            |      |        | VCO noise in open-loop conditions and offset<br>from 14 GHz carrier                                                                                |

| Phase Noise Floor                            |                                  |                        | -156       |      | dBc/Hz |                                                                                                                                                    |

| 100 KHz Offset                               |                                  |                        | -106       |      | dBc/Hz |                                                                                                                                                    |

| 1 MHz Offset                                 |                                  |                        | -125       |      | dBc/Hz |                                                                                                                                                    |

| 10 MHz Offset                                |                                  |                        | -145       |      | dBc/Hz |                                                                                                                                                    |

| Parameter                                         | Symbol                      | Min | Тур  | Мах | Unit   | Test Conditions/Comments |

|---------------------------------------------------|-----------------------------|-----|------|-----|--------|--------------------------|

| Normalized In-Band Phase Noise Floor <sup>5</sup> |                             |     |      |     |        |                          |

| Integer Mode                                      | L <sub>NORM-INT</sub>       |     | -239 |     | dBc/Hz |                          |

| Fractional Mode                                   | L <sub>NORM-FRAC</sub>      |     | -237 |     | dBc/Hz |                          |

| Normalized 1/f Phase Noise Floor <sup>5, 6</sup>  | L <sub>1/f</sub>            |     | -287 |     | dBc/Hz | Normalized to 1 Hz       |

| Normalized 1/f Figure of Merit (FOM) <sup>6</sup> | L <sub>1/f_1G_10k</sub>     |     |      |     |        |                          |

| Integer Mode                                      | L <sub>1/f_1G_10k INT</sub> |     | -147 |     | dBc/Hz |                          |

| Fractional Mode                                   | L <sub>1/f_1G_10k</sub>     |     | -143 |     | dBc/Hz |                          |

|                                                   | FRAC                        |     |      |     |        |                          |

| Integrated RMS Jitter                             |                             |     |      |     |        |                          |

| Integration Bandwidth: 100 Hz to 100 MHz          |                             |     | 20   |     | fs     | RFOUT = 20 GHz           |

| ADC SNR Method                                    |                             |     | 31   |     | fs     | RFOUT = 20 GHz           |

| Spurious                                          |                             |     |      |     |        |                          |

| f <sub>REF</sub>                                  |                             |     | <-95 |     | dBc    |                          |

| f <sub>PFD</sub>                                  |                             |     | -90  |     | dBc    |                          |

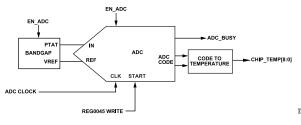

| TEMPERATURE SENSOR (ANALOG-TO-DIGITAL             |                             |     |      |     |        |                          |

| CONVERTER (ADC))                                  |                             |     |      |     |        |                          |

| ADC Clock Frequency                               | f <sub>ADC_CLK</sub>        |     |      | 400 | kHz    | ADC clock divider output |

| ADC Clock Divider Frequency                       | f <sub>ADC_CLKDIV</sub>     |     |      | 125 | MHz    | ADC clock divider input  |

| Resolution                                        |                             |     |      | 8   | Bits   |                          |

<sup>1</sup>  $0.9 \text{ V} < \text{V}_{CP} < \text{V}_{5V CP} - 0.9 \text{ V}.$

<sup>2</sup> Valid for 1.60 V  $\leq$  V<sub>TUNE</sub>  $\leq$  2.85 V with part calibrated after a power cycle or software power-on reset.

<sup>3</sup> Based on characterization.

<sup>4</sup> V<sub>OD</sub> is the output differential voltage.

<sup>5</sup> These values are modeled in ADIsimPLL.

<sup>6</sup> Integrated ranged 1 kHz to f<sub>OUT</sub>.

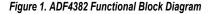

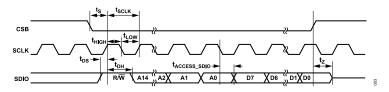

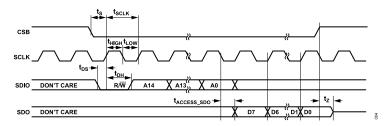

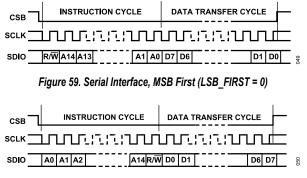

#### SERIAL INTERFACE TIMING CHARACTERISTICS

$V_{3.3V\_1}$  = 3.3 V,  $V_{3.3V\_2}$  = 3.15 V to 3.45 V,  $V_{5V\_VCO}$  =  $V_{5V\_CP}$  =  $V_{5V\_CAL}$  = 4.75 V to 5.25 V, all voltages are with respect to GND, and  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 1. Serial Interface Timing Characteristics

| Parameter                                | Symbol                   | Min | Тур | Max | Unit | Test Conditions/Comments             |

|------------------------------------------|--------------------------|-----|-----|-----|------|--------------------------------------|

| SERIAL INTERFACE (CSB, SCLK, SDIO, SDO)  |                          |     |     |     |      | See Figure 2, Figure 3, and Figure 4 |

| SCLK Frequency                           | f <sub>SCLK</sub>        |     |     | 75  | MHz  |                                      |

| SCLK Pulse Width High                    | t <sub>HIGH</sub>        | 6   |     |     | ns   |                                      |

| SCLK Pulse Width Low                     | t <sub>LOW</sub>         | 6   |     |     | ns   |                                      |

| SDIO Setup Time                          | t <sub>DS</sub>          | 4   |     |     | ns   |                                      |

| SDIO Hold Time                           | t <sub>DH</sub>          | 2   |     |     | ns   |                                      |

| SCLK Fall Edge to SDIO Valid Prop Delay  | t <sub>ACCESS_SDIO</sub> | 6   |     |     | ns   |                                      |

| SCLK Fall Edge to SDO Valid Prop Delay   | t <sub>ACCESS_SDO</sub>  | 6   |     |     | ns   |                                      |

| CSB Rising Edge to SDIO High-Z           | tz                       | 6   |     |     | ns   |                                      |

| CSB Falling Edge to SCLK Rise Setup Time | ts                       | 2   |     |     | ns   |                                      |

| SCLK Rising Edge to CSB Rise Hold Time   | t <sub>H</sub>           | 3   |     |     | ns   |                                      |

#### Serial Interface Timing Diagrams

#### Figure 2. Write Timing Diagram

Figure 3. 3-Wire Read Timing Diagram (SDO\_ACTIVE = 0)

Figure 4. 4-Wire Read Timing Diagram (SDO\_ACTIVE = 1)

#### PHASE ADJUST 2-WIRE INTERFACE

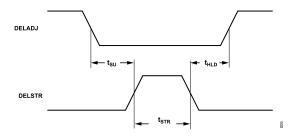

#### Table 2. Phase Adjust 2-Wire Interface Specifications

| Parameter    | Symbol           | Min | Тур | Max | Unit |

|--------------|------------------|-----|-----|-----|------|

| TIME         |                  |     |     |     |      |

| Setup        | t <sub>SU</sub>  | 20  |     |     | ns   |

| Hold         | t <sub>HLD</sub> | 20  |     |     | ns   |

| STROBE WIDTH | t <sub>STR</sub> | 10  |     |     | ns   |

## Phase Adjust 2-Wire Interface Timing Diagram

Figure 5. 2-Wire Phase Adjust Timing Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3. Absolute Maximum Ratings

| Parameter                                                                  | Rating                                                                                 |

|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| V <sub>3.3V_1</sub> (V3_LS, V3_LDO, V3_REF, V3_PFD,<br>and V3_NDIV) to GND | -0.3 V to +3.6 V                                                                       |

| $V_{3.3V\ 2}$ (V3_VCO, V3_OUTDIV, V3_RFOUT1, and V3_FOUT2) to GND          | -0.3 V to +3.6 V                                                                       |

| $V_{V5\_CAL}$ , $V_{V5\_VCO}$ , and $V_{V5\_CP}$ to GND                    | -0.3 V to +5.5 V                                                                       |

| Voltage on CP Pin                                                          | -0.3 V to V5_CP + 0.3 V                                                                |

| Voltage on All Other Pins                                                  | -0.3 V to V <sub>3.3V 1</sub> + 0.3 V                                                  |

| Digital Outputs (MUXOUT, LKDET, SDO, and SDIO)                             | 5 mA                                                                                   |

| RFOUT1P/RFOUT1N and RFOUT2P/RFOUT2N                                        | Maximum (GND - 0.3 V,<br>V <sub>3.3V_2</sub> -1.2 V) to<br>V <sub>3.3V_2</sub> + 0.3 V |

| REFP and REFN                                                              | -0.65 V to V <sub>3.3V 1</sub> + 0.65 V                                                |

| Voltage on all Other Pins                                                  | -0.3 V to V <sub>3.3V 1</sub> + 0.3 V                                                  |

| REFP to REFN and SYNCP to SYNCN                                            | ±1.35 V                                                                                |

| Temperature                                                                |                                                                                        |

| Operating Junction Range                                                   | -40°C to +125°C                                                                        |

| Storage Range                                                              | -55°C to +150°C                                                                        |

| Maximum Junction                                                           | 150°C                                                                                  |

| Reflow Soldering                                                           |                                                                                        |

| Peak Temperature                                                           | 260°C                                                                                  |

| Time at Peak Temperature                                                   | 30 sec                                                                                 |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.  $\theta_{JC\text{-}TOP}$  and  $\theta_{JC\text{-}BOTTOM}$  are the junction-to-case thermal resistance top and bottom.

#### Table 4. Thermal Resistance

| Package Type <sup>1</sup> | $\theta_{JA}$ | θ <sub>JC-TOP</sub> | θ <sub>JC-BOTTOM</sub> | Unit |

|---------------------------|---------------|---------------------|------------------------|------|

| CC-48-10                  | 25.23         | 16.11               | 5.10                   | °C/W |

<sup>1</sup> Test Condition 1: thermal impedance simulated values are based on use of a 4-layer PCB with the thermal impedance paddle soldered to a ground plane.

#### TRANSISTOR COUNT

The transistor count for the ADF4382 is 4700 (bipolar) and 385,400 (CMOS).

## **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

#### ESD Ratings for ADF4382

#### Table 5. ADF4382, 48-Terminal LGA

| ESD Model | Withstand Threshold (V) | Class |

|-----------|-------------------------|-------|

| HBM       | 4000                    | 3A    |

| CDM       | 1000                    | C3    |

#### ESD CAUTION

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

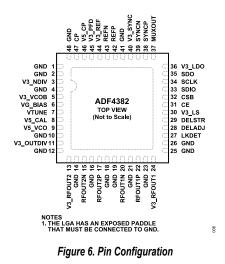

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 6. Pin Function Descriptions

| Pin No.                                                    | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 10, 12, 14, 16, 18, 19,<br>21, 23, 25, 26, 41, 48 | GND              | Negative Power Supply (Ground). Tie the GND pins directly to the ground pad.                                                                                                                                                                                                                                                                                                                        |

| 3                                                          | V3_NDIV          | 3.15 V to 3.45 V Positive Power Supply Pin for the PLL Feedback Divider Circuitry. Short the V3_NDIV pin to the other pins in the 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                       |

| 5                                                          | V3_VCOB          | 3.15 V to 3.45 V Positive Power Supply Pin for the Bias Circuitry and Digital Logic Control Portion of the VCO. Short the V3_VCOB pin to the other pins in the 3.3 V Power Supply Group 2.                                                                                                                                                                                                          |

| 6                                                          | VG_BIAS          | Bias Decoupling Pin. Connect uninstalled 0402, 0.1 µF capacitor footprint to GND.                                                                                                                                                                                                                                                                                                                   |

| 7                                                          | VTUNE            | VCO Tuning Input. This frequency control pin is normally connected to the external loop filter.                                                                                                                                                                                                                                                                                                     |

| 8                                                          | V5_CAL           | 4.75 V to 5.25 V Positive Power Supply Pin for VCO Calibration Circuitry. The V5_CAL pin can be shorted to the V5_VCO supply plane.                                                                                                                                                                                                                                                                 |

| 9                                                          | V5_VCO           | 4.75 V to 5.25 V Positive Power Supply Pin for the VCO Circuitry.                                                                                                                                                                                                                                                                                                                                   |

| 11                                                         | V3_OUTDIV        | 3.15 V to 3.45 V Positive Power Supply Pin for the Output Divider Circuitry. Short the V3_OUTDIV pin to the other pins in the 3.3 V Power Supply Group 2.                                                                                                                                                                                                                                           |

| 13                                                         | V3_RFOUT2        | 3.15 V to 3.45 V Positive Power Supply Pin for the RFOUT 2 Buffer Circuitry. Short the V3_RFOUT2 pin to the other pins in the 3.3 V Power Supply Group 2.                                                                                                                                                                                                                                           |

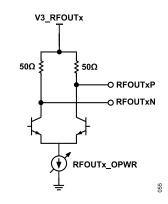

| 15, 17                                                     | RFOUT2N, RFOUT2P | RF Output 2 Output Signal. The VCO output divider is buffered and presented differentially on the RFOUT2N and RFOUT2P pins. The outputs have a 50 $\Omega$ (typical) output resistance per side (100 $\Omega$ differential). The far end of the transmission line is typically terminated with 100 $\Omega$ connected across the outputs. The output amplitude is programmable via the serial port. |

| 20, 22                                                     | RFOUT1N, RFOUT1P | RF Output 1 Output Signal. The VCO output divider is buffered and presented differentially on the RFOUT1N and REFOUT1P pins. The outputs have 50 $\Omega$ (typical) output resistance per side (100 $\Omega$ differential). The far end of the transmission line is typically terminated with 100 $\Omega$ connected across the outputs. The output amplitude is programmable via the serial port.  |

| 24                                                         | V3_RFOUT1        | 3.15 V to 3.45 V Positive Power Supply Pin for the RFOUT 1 Buffer Circuitry. Short the V3_RFOUT1 pin to the other pins in the 3.3 V Power Supply Group 2.                                                                                                                                                                                                                                           |

| 27                                                         | LKDET            | PLL Lock Detect. This output presents the lock status of the PLL. The PLL is locked when LKDET is a logic high.                                                                                                                                                                                                                                                                                     |

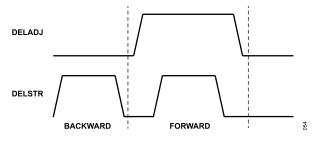

| 28                                                         | DELADJ           | Delay Adjust Input Signal. Logic 0 ensures that the delay of the RF output signal is reduced after DELSTR is asserted. Logic 1 ensures that the delay of the RF output signal is increased after DELSTR is asserted.                                                                                                                                                                                |

| 29                                                         | DELSTR           | Delay Strobe Input Signal. A rising edge on this signal indicates that an adjustment is needed. The adjustment is then made on the falling edge.                                                                                                                                                                                                                                                    |

| 30                                                         | V3_LS            | 3.15 V to 3.45 V Positive Power Supply Pin for the Internal Level Shift Circuitry. Short the V3_LS pin to the other pins in the 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                         |

| 31                                                         | CE               | Chip Enable. 3.3 V CMOS input. Does not support 1.8 V CMOS levels. This CMOS input enables the device when driven high. A logic low disables the device, putting the device in a full power-down state causing the register to reset. Conversely, the PD_ALL bit powers down the device, but does not reset the registers.                                                                          |

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

#### Table 6. Pin Function Descriptions (Continued)

| Pin No.     | Mnemonic     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32          | CSB          | Serial Port Chip Select. This CMOS input initiates a serial port communication burst when driven low, ending the burst when driven back high.                                                                                                                                                                                                                                                                                                             |

| 33          | SDIO         | Serial Data Input/Output. CMOS input and output. When configured as an input, the serial port uses this CMOS input for data. In 3-wire readback mode (default mode), the SDIO pin outputs data from the serial port during a read communication burst.                                                                                                                                                                                                    |

| 34          | SCLK         | Serial Port Clock. This CMOS input clocks serial port input data on its rising edge.                                                                                                                                                                                                                                                                                                                                                                      |

| 35          | SDO          | Optional Serial Data Output. In 3-wire mode (default mode), this three-state CMOS pin remains in a high impedance state. In 4-wire readback mode, the SDO pin presents data from the serial port during a read communication burst. When the CSB is de-asserted, SDO returns to a high impedance. Optionally, attach a resistor of >200 k $\Omega$ to prevent a floating output.                                                                          |

| 36          | V3_LDO       | 3.15 V to 3.45 V Positive Power Supply Pin for the Internal Low Dropout (LDO) Regulator Circuitry. Short the V3_LDO pin to the other pins in the 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                              |

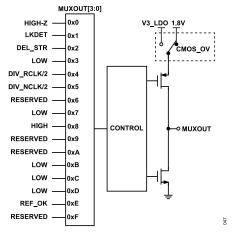

| 37          | MUXOUT       | Internal Device Multiplexor Output. This output pin can be connected to multiple internal nodes for factory test and debug purposes.                                                                                                                                                                                                                                                                                                                      |

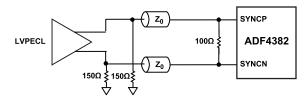

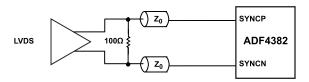

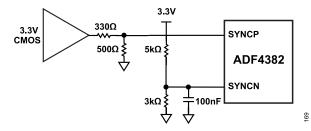

| 38, 39      | SYNCP, SYNCN | Synchronization Input Signals. Both RF output signals are synchronized to an input signal at these pins. SYNCP and SYNCN are used for multichip phase synchronization. This differential input can accept both high and low common-mode input signals (based on the SPI bit setting).                                                                                                                                                                     |

| 40          | V3_SYNC      | 3.15 V to 3.45 V Positive Power Supply. Short the V3_SYNC pin to the other pins in the 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                                                        |

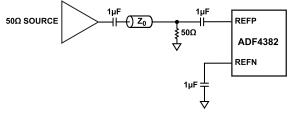

| 42, 43      | REFP, REFN   | Reference Input Signals. These differential inputs are buffered with a low noise amplifier (LNA) ideally suited for high slew rates (default mode). For low slew rate reference input signals, an alternate LNA can be selected via the serial port. Reference inputs are self biased and must be AC-coupled with 1 µF capacitors. Reference inputs accept differential or single-ended inputs. See the Reference Input Network section for more details. |

| 44          | V3_REF       | 3.15 V to 3.45 V Positive Power Supply Pin for the PLL Reference Circuitry. Short the V3_REF pin to the other pins in the 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                     |

| 45          | V3_PFD       | 3.15 V to 3.45 V Positive Power Supply Pin for PFD Circuitry. Short the V3_PFD pin to the other pins in the 3.3 V Power Supply Group 1.                                                                                                                                                                                                                                                                                                                   |

| 46          | V5_CP        | 4.75 V to 5.25 V Positive Power Supply Pin for Charge Pump Circuitry. Isolate the V5_CP pin from the V5_VCO supply plane.                                                                                                                                                                                                                                                                                                                                 |

| 47          | CP           | Charge Pump Output. This bidirectional current output is normally connected to the external loop filter.                                                                                                                                                                                                                                                                                                                                                  |

| Exposed Pad | GND          | Negative Power Supply (Ground). The package exposed pad must be soldered directly to the PCB land. The PCB land pattern must have multiple thermal vias to the ground plane for both low ground inductance and low thermal resistance.                                                                                                                                                                                                                    |

Figure 7. Open-Loop VCO Phase Noise vs. Offset Frequency at Various Frequencies

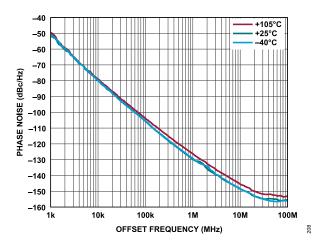

Figure 8. Open-Loop VCO Phase Noise vs. Offset Frequency at RFOUT = 22 GHz and Various Temperatures

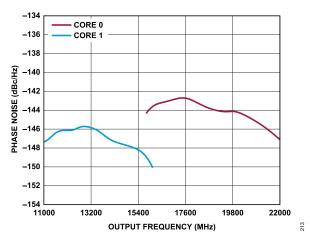

Figure 9. Open-Loop VCO Phase Noise Across Output Frequency at 1 kHz Offset

Figure 10. Open-Loop VCO Phase Noise Across Output Frequency at 10 kHz Offset

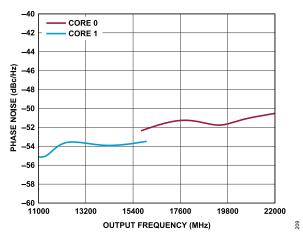

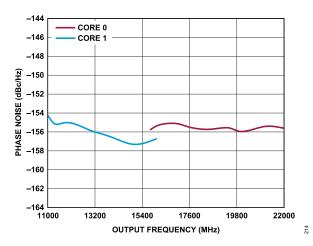

Figure 11. Open-Loop VCO Phase Noise Across Output Frequency at 100 kHz Offset

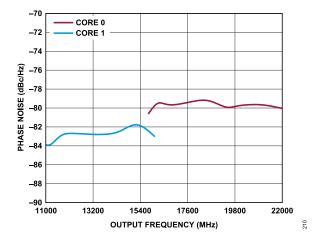

Figure 12. Open-Loop VCO Phase Noise Across Output Frequency at 1 MHz Offset

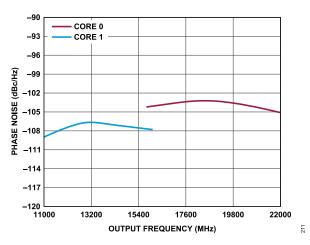

Figure 13. Open-Loop VCO Phase Noise Across Output Frequency at 10 MHz Offset

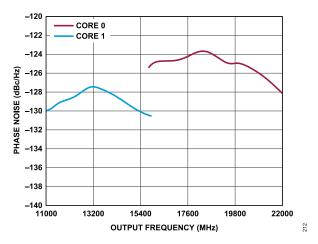

Figure 14. Open-Loop VCO Phase Noise Across Output Frequency at 100 MHz Offset

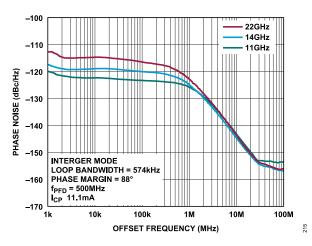

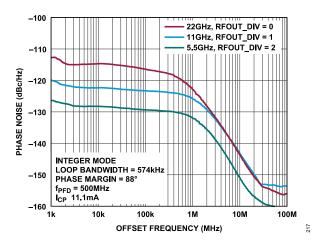

Figure 15. Closed-Loop Phase Noise vs. Offset Frequency at RFOUT = 11 GHz, RFOUT = 14 GHz, and RFOUT = 22 GHz

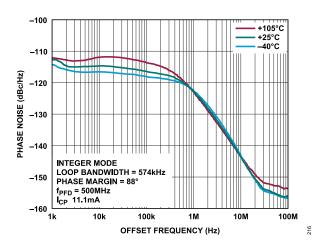

Figure 16. Closed-Loop Phase Noise vs. Offset Frequency at 22 GHz VCO Frequency Across Temperatures

Figure 17. Closed-Loop Phase Noise vs. Offset Frequency at 22 GHz VCO Frequency and Divided Output Frequencies

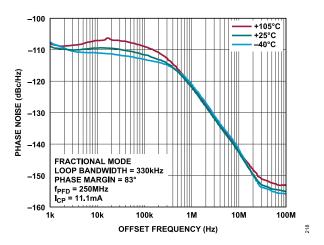

Figure 18. Closed-Loop Phase Noise vs. Offset Frequency at 21.9 GHz VCO Frequency Across Temperatures

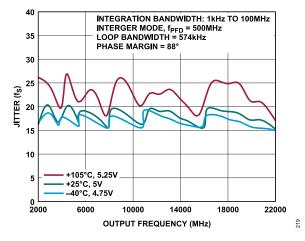

Figure 19. 1 kHz to 100 MHz Integrated Jitter in Integer Mode, f<sub>PFD</sub> = 500 MHz

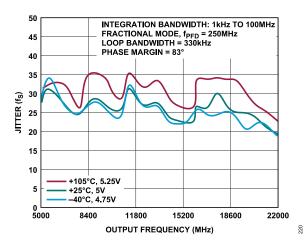

Figure 20. 1 kHz to 100 MHz Integrated Jitter in Fractional Mode,  $f_{PFD}$  = 250 MHz

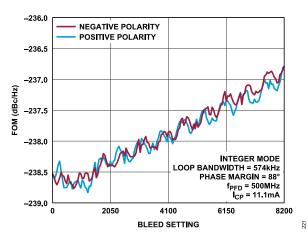

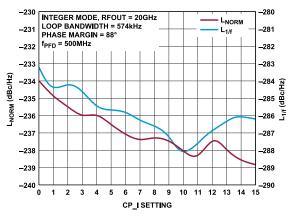

Figure 21. FOM,  $L_{NORM}$  Integer Mode vs. Bleed Setting,  $f_{PFD}$  = 500 MHz, RFOUT = 20 GHz

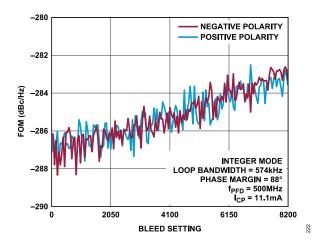

Figure 22. FOM,  $L_{1/f}$  Integer Mode vs. Bleed Setting,  $f_{PFD}$  = 500 MHz, RFOUT = 20 GHz

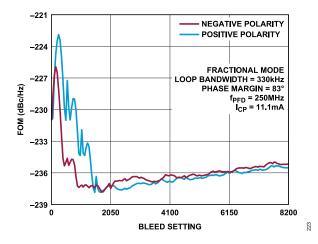

Figure 23. FOM,  $L_{NORM}$  Fractional Mode vs. Bleed Setting,  $f_{PFD}$  = 250 MHz, RFOUT = 20.001 GHz

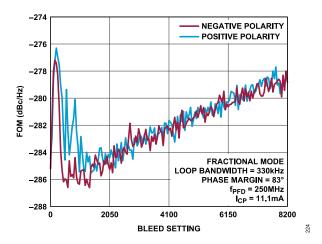

Figure 24. FOM,  $L_{1/f}$  Fractional Mode vs. Bleed Setting,  $f_{PFD}$  = 250 MHz, RFOUT = 20.001 GHz

225

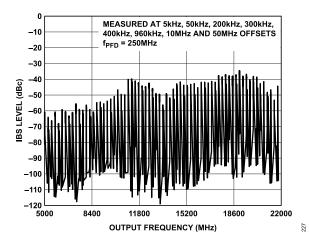

Figure 27. Worst Case Integer Boundary Spurs (IBS) Level vs. Output Frequency with f<sub>PFD</sub> = 250 MHz

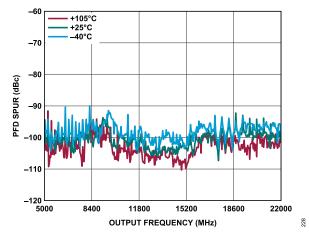

Figure 28. PFD Spur vs. Output Frequency at Various Temperatures

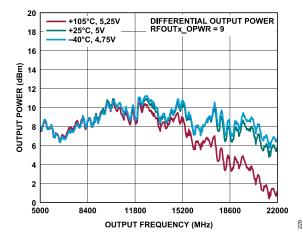

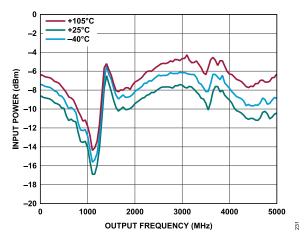

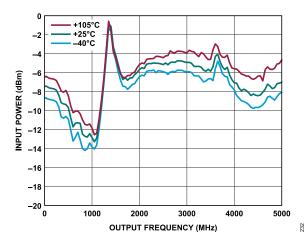

Figure 29. Differential Output Power vs. Output Frequency at Various Temperatures and Voltages

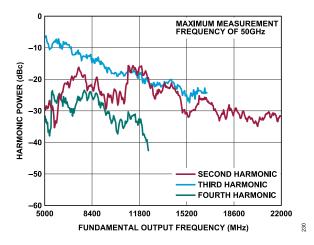

Figure 30. Harmonic Power vs. Fundamental Output Frequency

Figure 31. Minimum Input Signal for REF\_OK = 1 for Delayed Match Amplifier (DMA) Buffer at Various Temperatures

Figure 32. Minimum Input Signal for REF\_OK = 1 for LNA Buffer at Various Temperatures

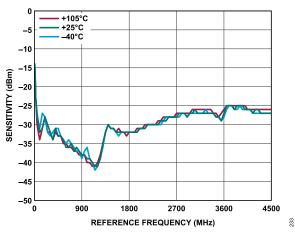

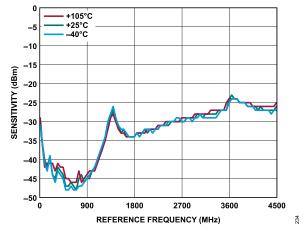

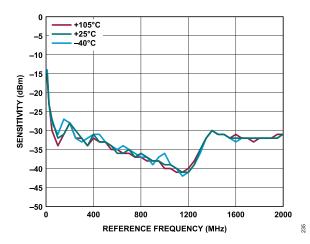

Figure 33. Reference Sensitivity for DMA Buffer at Various Temperatures

Figure 34. Reference Sensitivity for LNA Buffer at Various Temperatures

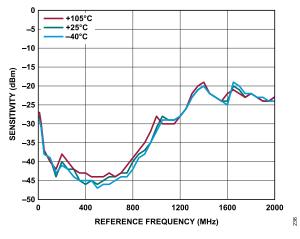

Figure 35. Reference Doubler Sensitivity for DMA Buffer at Various Temperatures

Figure 36. Reference Doubler Sensitivity for LNA Buffer at Various Temperatures

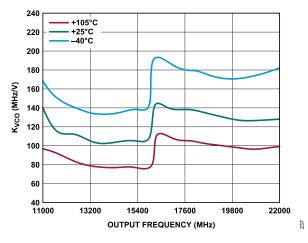

Figure 37. K<sub>VCO</sub> vs. Output Frequency at Various Temperatures

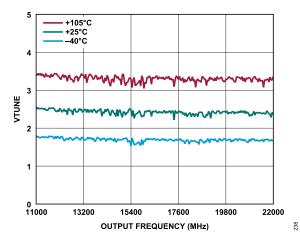

Figure 38. VTUNE vs. Output Frequency at Various Temperatures

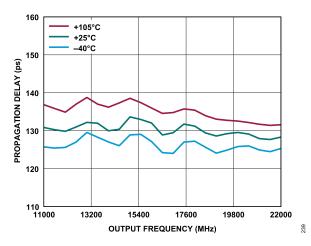

Figure 39. Propagation Delay vs. Output Frequency

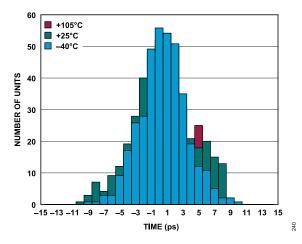

Figure 40. Normalized Propagation Delay (tPD) Histogram

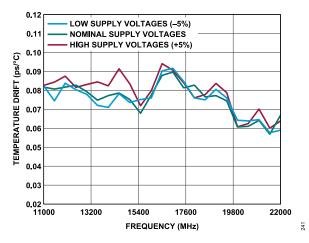

Figure 41. Temperature Drift vs. Frequency

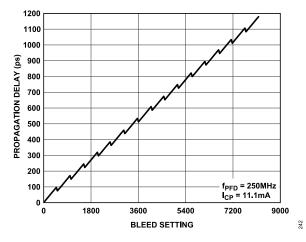

Figure 42. Propagation Delay vs. Bleed Setting

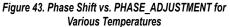

Figure 44. Output Power when Buffer Powered Down (PD\_RFOUTx = 1) vs. Output Frequency

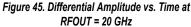

Figure 46. 3.3 V Supply Group 2 Current at Various Output Settings Across Temperature

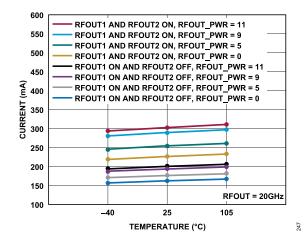

Figure 47. 3.3 V Supply Group 2 Current at Various Power Supply Voltages and RFOUT DIV Settings

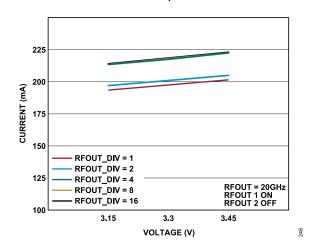

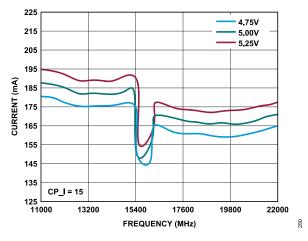

Figure 48. 5 V Delta Supply Current (Δ<sub>CURRENT</sub>) at Various CP\_I Settings

Figure 49. 5 V Supply Current at Various Output Frequencies and Power Supply Voltages

## INTRODUCTION

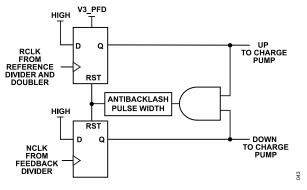

A PLL is a complex feedback system that can conceptually be considered a frequency multiplier. The system multiplies the frequency input at REFP/REFN and outputs a higher frequency at RFOUTxP/ RFOUTxN. The PFD, charge pump, output divider, feedback divider, VCO, and external loop filter form a feedback loop to accurately control the output frequency (see Figure 50). When operating in integer mode, the reference divider or reference doubler sets the frequency resolution. When operating in fractional mode, the fractional-N divider sets the frequency resolution.

Figure 50. PLL Loop Diagram

#### **OUTPUT FREQUENCY**

When the loop is locked, the  $f_{VCO}$  (in Hz) produced at the output of the VCO is determined by  $f_{\text{REF}}$  and the O, R, and N values given by the following equation.

$$f_{VCO} = f_{REF} \times \frac{D \times N \times O}{R} \tag{1}$$

where:

f<sub>REF</sub> is the reference frequency.

D is the reference doubler.

R is the reference divider.

O is the output divider.

$f_{PFD}$  is given by the following:

$$f_{PFD} = \frac{f_{REF} \times D}{R} \tag{2}$$

and f<sub>VCO</sub> can be alternatively expressed as follows:

$$f_{VCO} = f_{PFD} \times N \times O \tag{3}$$

The output frequency,  $f_{\text{RFOUT}}$ , produced at the output of the output divider is given by the following:

$$f_{RFOUT} = \frac{f_{VCO}}{O} \tag{4}$$

N is the feedback divider and is given by the following:

$$N = N_{INT} + \frac{FRAC\,IWORD + \frac{FRAC\,2WORD}{MOD\,2WORD}}{MOD\,1WORD}$$

(5)

#### **Output Frequency Calculation Procedure**

The following is a worked example for a fractional mode  $f_{RFOUT}$  using the formulas in the Output Frequency section for an  $f_{RFOUT}$  = 20.132 GHz, a channel spacing ( $f_{CHSP}$ ) of 1 Hz, and where  $f_{REF}$  =  $f_{PFD}$  = 250 MHz.

Because  $f_{REF} = f_{PFD}$ , the reference divider is set to divide by 1 (R\_DIV = 1), and the reference doubler is bypassed (EN\_RDBLR = 0).

The output frequency is within the fundamental VCO frequency range ( $f_{VCO}$ ), which means that the output divider (O) is set to divide by 1 (RFOUT\_DIV = 0).

The steps to calculate all N-divider component values are outlined as follows:

1. Calculate the overall N-value required based on the  $f_{\text{RFOUT}}$  and  $f_{\text{PFD}}$  provided as follows:

$$N = \frac{f_{RFOUT}}{f_{PFD}} \tag{6}$$

$$V = \frac{20.132 \text{ GHz}}{250 \text{ MHz}} = 80.528 \tag{7}$$

2. Separate the  $N_{\text{INT}}$  and  $N_{\text{FRAC}}$  components as follows:

$$N_{INT} = INT(N) = 80 \tag{8}$$

$$N_{FRAC} = N - N_{INT} = 0.528$$

(9)

$$N_{FRAC1WORD} = N_{FRAC} \times MOD\, 1WORD \tag{10}$$

where MOD1WORD is a fixed value of 2<sup>25</sup> = 33554432

$$N_{FRAC1WORD} = 0.528 \times 33554432$$

= 17716740.096 (11)

$$FRAC 1WORD = INT(N_{FRAC1WORD})$$

$$= 17716740$$

(12)

FRAC2WORD and MOD2WORD are only required if  $N_{FRAC1WORD}$  is not an integer number. If  $N_{FRAC1WORD}$  is an integer, then no further calculation is required. In this case, VAR\_MOD\_EN is set to 0 to disable FRAC2WORD and MOD2WORD.

- 4. Calculate the MOD2WORD as follows:

- **a.** Determine the remainder of the fractional word as follows:

$$N_{REMAINDER} = N_{FRAC\,1WORD} - FRAC\,1WORD = 0.096$$

(13)

$$N_{REMAINDER} = 17716740.096$$

- 17716740 = 0.096 (14)

**b.** Find the greatest common divisor (GCD) between  $f_{FPD}$  and MOD1WORD ×  $f_{CHSP}$  as follows:

$$GCD(MOD \, 1WORD \times f_{CHSP}, f_{PFD}) \tag{15}$$

$$GCD(2^{25} \times 1, 250 \text{ MHz}) = 128$$

(16)

c. Calculate the initial MOD2WORD calculation as follows:

$$MOD 2WORD_{INITIAL} = \frac{f_{PFD}}{GCD(MOD 1WORD \times f_{CHSP}, f_{PFD})}$$

(17)

$$MOD 2WORD_{INITIAL} = \frac{250 \text{ MHz}}{128}$$

(18)

= 1953125

d. Compare with MOD2WORD<sub>MAX</sub>.

In this example, phase resynchronization is not required. Therefore, MOD2WORD<sub>MAX</sub> =  $2^{24} - 1 = 16777215$  and the MOD2WORD = 1953125 previously calculated can be used.

If phase resynchronization were required, then MOD2WORD<sub>MAX</sub> =  $2^{17} - 1 = 131071$ . Then, f<sub>CHSP</sub> must be increased to reduce MOD2WORD  $\leq$  MOD2WORD<sub>MAX</sub>.

It is recommended to increase the  $f_{CHSP}$  by multiplying by five for each repetition of the previous step to reduce to MOD2WORD  $\leq$  MOD2WORD $_{MAX}$ .

1

e. Calculate the final MOD2WORD.

To maximize the frequency resolution, the final value of MOD2WORD is calculated by obtaining the highest integer multiple of the initial MOD2WORD, that is less than or equal to the MOD2WORD<sub>MAX</sub> as follows.

$$MOD 2WORD = INT$$

$$\left(\frac{MOD 2WORD_{MAX}}{MO2 WORD_{INITIAL}}\right)$$

$$\times MOD 2WORD_{INITIAL}$$

$$MOD 2WORD = INT\left(\frac{16777215}{1953125}\right)$$

$$\times 1953125$$

(19)

(20)

$$MOD2WORD = 8 \times 1953125$$

= 15625000

5. Calculate FRAC2WORD as follows:

$$FRAC2WORD = INT(N_{REMAINDER} \times MOD2WORD)$$

(22)

$$FRAC 2WORD = INT(0.096) \times 15625000)$$

(23)

$FRAC2WORD = 1500000 \tag{24}$

6. Calculate the total N-value using the original formula as follows:

$$N = N_{INT} + \frac{FRAC\,IWORD + \frac{FRAC\,2WORD}{MOD\,2WORD}}{MOD\,1WORD}$$

(25)

$$N = 80 + \frac{17716740 + \frac{1500000}{15625000}}{33554432} = 80.528$$

(26)

7. Calculate f<sub>RFOUT</sub> as follows:

$$f_{VCO} = f_{REF} \times \frac{D \times N \times O}{R} \tag{27}$$

Because  $f_{REF} = f_{PFD}$  and  $f_{VCO} = f_{RFOUT}$ ; therefore, the following:

$$f_{RFOUT} = f_{REF} \times N \tag{28}$$

$f_{RFOUT} = 250 \text{ MHz} \times 80.528 = 20$ .132 GHz (29)

#### **CIRCUIT DESCRIPTION**

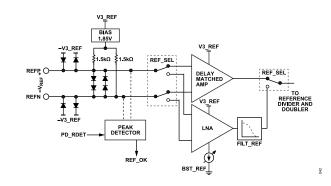

#### **Reference Input Buffer**

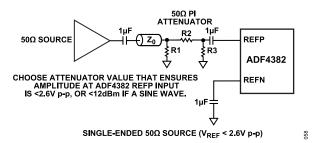

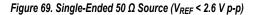

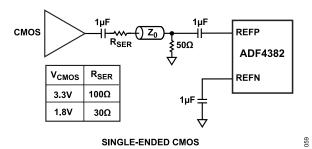

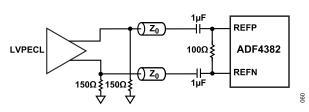

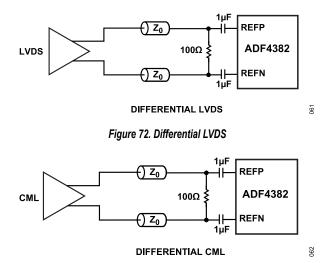

The reference frequency of the PLL is applied differentially on the REFP and REFN pins. These high impedance inputs are self biased and must be AC-coupled with 1  $\mu$ F capacitors (see Figure 51 for a simplified schematic). Alternatively, the inputs can be used single ended by applying the reference frequency at REFP and bypassing REFN to GND with a 1  $\mu$ F capacitor.

Figure 51. Reference Input Stage

A high quality signal must be applied to the REFP and REFN inputs as these inputs provide the frequency reference to the entire PLL.

To achieve the in-band phase noise performance of the ADF4382,

(21) apply a continuous wave signal or a square wave with a slew rate of at least 1000 V/µs. See the Reference Source Considerations section for more information on reference input signal requirements and interfacing.

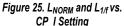

The REF\_SEL bit (Register 0x030, Bit 5) can be set to either a CML reference input or sine wave or slow slew-rate reference input. When REF\_SEL is set to 0, the delay matched amplifier (DMA) buffer is selected. The DMA is optimized for high slew rate signals, such as square waves or higher frequency and higher amplitude sine waves. The DMA has a controlled propagation delay from the reference input to clock output, which eases time zero and over temperature multichip clock alignment.

When the REF\_SEL bit is set to 1, the LNA is selected. The LNA is optimized for low slew rate signals, such as lower frequency or lower amplitude sine waves.

The REF\_SEL bit must be set correctly to optimize the in-band phase noise performance and propagation delay,  $t_{PD}$ . See Table 7 for recommended settings.

| Table 7. RE | F_SEL | Programming |

|-------------|-------|-------------|

|-------------|-------|-------------|

| REF_SEL | Sine Wave Slew Rate (V/µs) | Square Wave    | Optimized t <sub>PD</sub> |

|---------|----------------------------|----------------|---------------------------|

| 0       | ≥1000                      | Preferred      | Yes                       |

| 1       | <1000                      | Not applicable | Not applicable            |

To calculate the slew rate of a sine wave, use the following equation:

$$Slew Rate = 2 \times \pi \times f \times V \tag{30}$$

where:

f is the sine wave frequency.

V is the sine wave amplitude (in V peak)

The FILT\_REF bit (Register 0x02F, Bit 6) controls the reference input LPF of the LNA and must be set only for sine wave signals less than 20 MHz to limit the wideband noise of the reference. The FILT\_REF bit must be set correctly to reach the normalized in-band phase noise floor (L<sub>NORM</sub>). Square wave inputs have FILT\_REF set to 0. Table 8 shows the recommended settings.

#### Table 8. FILT\_REF Programming

| FILT_REF | Sine Wave f <sub>REF</sub> (MHz) | Square Wave f <sub>REF</sub> |

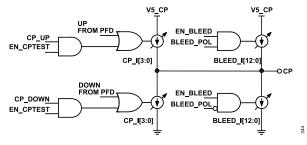

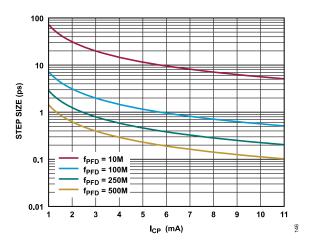

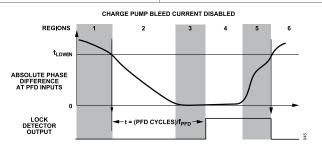

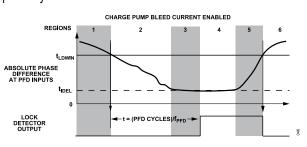

|----------|----------------------------------|------------------------------|