# SELECTED ITEM DRAWING

| Unless otherwise<br>specified<br>DIMENSIONS | TOLERANCES:<br>.XX +/- 0.010<br>.XXX +/- 0.005 | Drawing<br>practices       |           | 81 GHz to 86 GHz,<br>Medium Power Amplifier |

|---------------------------------------------|------------------------------------------------|----------------------------|-----------|---------------------------------------------|

| ARE IN INCHES<br>(MM)                       | .XXXX +/- 0.002<br>ANGLES+/5 DEG               | per <b>ASME</b><br>Y14.100 | SIZE<br>A | DRAWING NUMBER SID000019                    |

#### SID000019

Rev. A Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Analog Way, Wilmington, MA 01887-2356, U.S.A. Tel: 781.935.5565 www.analog.com Tel: 800.262.5643 © 2024 Analog Devices, Inc. All rights reserved.

## 1. SCOPE

1.1. <u>Scope</u>

This drawing establishes the requirements for the 81 GHz to 86 GHz, GaAs, HEMT, MMIC, Medium Power Amplifier, to be screened in accordance with MIL-PRF-38534, Class K, to the requirements specified in 4.1, and 4.2 herein.

1.2. Analog Devices Part Number

| Generic Part Number | Screened Part Number |

|---------------------|----------------------|

| ADH-APH634S         | HMC8243              |

## 2. APPLICABLE DOCUMENTS

#### 2.1. Government Documents

Unless otherwise specified, the following drawings and standards, of the issue in effect on the date of the accepted purchase order, in the Department of Defense Index of Specifications and Standards (DODISS) and supplement thereto, shall form a part of this drawing to the extent specified herein.

## DEPARTMENT OF DEFENSE TEST METHOD STANDARD

MIL-STD-883 Microcircuits

## DEPARTMENT OF DEFENSE PERFORMANCE SPECIFICATIONS

MIL-PRF-38534 Hybrid Microcircuits, General Specifications For

MIL-PRF-38535 Integrated Circuit (Microcircuits) Manufacturing, General Specifications For

#### 2.2. Non-Government Documents

The following documents, of the issue in effect on the date of the purchase order, form a part of this drawing to the extent specified herein:

#### Analog Devices Inc.

HMC-APH634S Data Sheet Commercial Product Die Datasheet v01.0713 (Reference Only)

## 3. **REQUIREMENTS**

## 3.1. General Requirements

The devices delivered shall comply to this specification.

## 3.2. Design Construction and Physical Dimensions

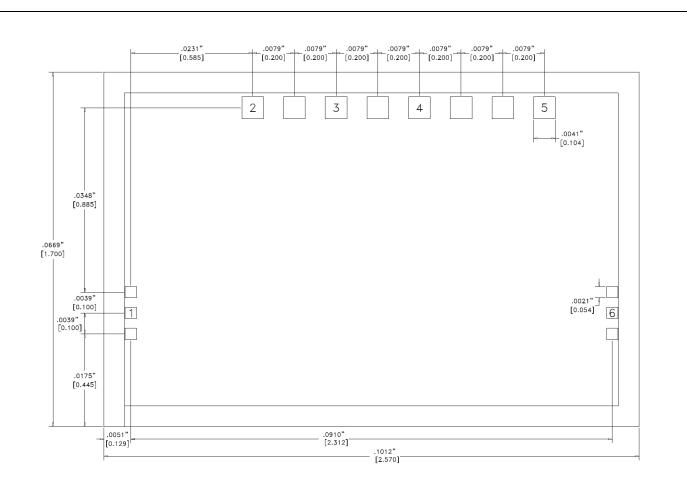

The design construction and physical dimensions shall be as defined in Figure 1 herein.

#### 3.3. Traceability

Each delivered device shall be traceable to the wafer number and the wafer lot number of each device. Inspection lot records shall be maintained to provide traceability to the specific wafer and wafer lot from which the chips originated.

## 3.4. Burn-In and Life Test Circuit

The burn-in and life test circuit and conditions shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test methods 1005 and 1015 per MIL-STD-883.

## 4. QUALITY ASSURANCE PROVISIONS

## 4.1. Wafer Acceptance Testing

The wafer lot acceptance testing shall consist of Class Level S inspections per MIL-STD-883 TM 5007. All deliverable Die shall have passed 100% element electrical test per 4.2.1. Element evaluation per 4.2.2 and passed 100% visual inspection, per MIL-STD-883 TM2010 Condition A, after wafer dicing.

#### 4.2. Dice Qualification Requirements

Dice qualification requirements shall be in accordance with MIL-PRF-38534, Appendix C, Table C-II, per Class K.

#### 4.2.1. Element Electrical Test (RF-On Wafer)

Electrical tests shall consist of the tests specified on Table I, tested at room temperature only.

## 4.2.2. Element Evaluation (Lot Acceptance Testing)

Sample Die shall be randomly selected from the wafer that has successfully passed RF-On wafer testing per 4.2.1 and shall be mounted to suitable fixturing for screening.

#### 4.2.2.1. Initial Electrical Test (Pre Burn-In)

Pre Burn-In electrical tests shall consist of the tests specified on Table II, tested at room temperature only.

#### 4.2.2.2. Interim Electrical Test (Post Burn-In)

Post Burn-In electrical tests shall consist of the tests specified on Table II tested at room temperature only and shall meet performance requirements in accordance with Table II and Table III.

#### 4.2.2.3. Final Electrical Test (Post Life Test)

Final electrical tests shall consist of the tests specified in Table II tested at -10 °C and +45 °C, which shall be Read and Record only, and shall meet performance requirements in accordance with Table II and Table III.

## 5. MIL-PRF-38534 EXCEPTIONS

5.1. Wafer Fabrication

Foundry information is available upon request.

- 5.2. Microcircuit Dice Evaluation Requirements (TABLE C-II)

- Pre-screen test post assembly required to Die qualification to remove all assembly related rejects.

- Subgroup 4: mechanical shock or constant acceleration not performed.

- Subgroup 4: Interim and post burn-in electrical tests will include tests screened at +25 °C only.

- Subgroup 4: Final electrical test (Subgroup 2, 3, 5, and 6) Qty/Acc = 5/0.

## 6. PREPARATION FOR DELIVERY

The preparation for delivery, packaging, preservation, ESD protection and handling shall be in accordance with MIL-PRF-38534.

6.1. <u>Die Packaging Information</u>

The Die shall be delivered in accordance with Table IV herein.

6.2. Inspection Data Requirements

The following data shall accompany each shipment.

a. A Certificate of Conformance (C of C) certifies that the lot(s) meets all requirements of this specification.

- b. Die Photograph

- c. Attribute data for all tests.

- d. Wafer Lot Acceptance data including photos from SEM inspection in 4.1.

- e. Summary of RF-On wafer test data per 4.2.1.

- f. Element Evaluation test results per 4.2.2.

- a. Variables data for electrical end-point measurements.

- g. Failure Analysis with photos (If applicable)

- h. A cover sheet indicating the following purchasing information:

- 1. Customer purchase order number.

- 2. Analog Devices part number.

- 3. Part lot identification codes.

- 4. Date & quantity shipped.

#### **TABLE I: DIE ELECTRICAL CHARACTERISTICS**

| Demonster                                  | Conditions <u>1/2/3</u> /  | Limits |     |     | 11    |  |

|--------------------------------------------|----------------------------|--------|-----|-----|-------|--|

| Parameter                                  | Unless otherwise specified | Min    | Тур | Max | Units |  |

| Gain                                       |                            | 7      |     |     | dB    |  |

| OP1dB                                      |                            | 15     |     |     | dBm   |  |

| Supply Current<br>(Idd1 + Idd2) <u>4</u> / | No Signal at RFIN          |        | 240 |     | mA    |  |

TABLE I Notes:

<u>1</u>/ Test limits apply at +25 °C only with Vdd1 = Vdd2 = +4 V.

2/ Gain and OP1dB measurements made at 83 GHz, 84 GHz, 85 GHz, and 86 GHz.

$\frac{3}{4}$  / Performance limits based upon direct to Die measurements. Limits differ than that of actual performance in a 50-ohm system with wirebonds.  $\frac{4}{4}$  / Vgg1 = Vgg2 voltage adjusted between -0.8 V and +0.3 V to achieve typical Idd1 + Idd2 = 400 mA

#### TABLE II: ELECTRICAL CHARACTERISTICS FOR QUALIFICATION SAMPLES

|                                            | Conditions <u>1/2/4/5/6</u> / |           | Limits |     |     | _     |  |

|--------------------------------------------|-------------------------------|-----------|--------|-----|-----|-------|--|

| Parameter Unless otherwise specified       |                               | Sub-Group | Min    | Тур | Мах | Units |  |

| Gain                                       |                               | 4         | 7      |     |     | dB    |  |

| OP1dB                                      |                               | 4         | 15     |     |     | dBm   |  |

| Supply Current<br>(Idd1 + Idd2) <u>3</u> / | No Signal at RFIN             | 1         |        | 240 |     | mA    |  |

TABLE II Notes:

<u>1</u>/Limits apply at +25 °C only with Vdd1 = Vdd2 = +4 V.

2/ Gain and OP1dB measurements made at 83 GHz, 84 GHz, 85 GHz, and 86 GHz.

$\frac{3}{2}$  / Vgg1 = Vgg2 voltage adjusted between -0.8 V and +0.3 V to achieve typical Idd1 + Idd2 = 400 mA at +25 °C only.

4/ Each device shall use the individual Vgg1= Vgg2 voltage established at pre burn-in throughout all electrical testing.

5/ -10 °C and +45 °C (subgroups 2, 3, 5, and 6) shall be Read and Record only and shall be performed on five (5) units only. <u>6</u>/ See MIL-PRF-38535 Table C-Xa for subgroup parameter definitions.

## TABLE III: BURN-IN/LIFE TEST DELTA LIMITS 1/2/3/4/

| Parameter                       | Test Conditions | Delta Limits | Units |

|---------------------------------|-----------------|--------------|-------|

| Gain                            |                 | ± 1.5        | dB    |

| Supply Current<br>(Idd1 + Idd2) | Per Table II    | ± 10         | %     |

TABLE III Notes:

<u>1</u>/ Delta test is performed at  $T_A = +25$  °C only.

$\underline{2}$ / Table II limits will not be exceeded.

$\overline{\underline{3}}$ / Delta calculated pre/post 240 hours and post 240 hours / post 1000 hours.

NOTES:

- 1. ALL DIMENSIONS ARE IN INCHES [MM]

- 2. DIE THICKNESS IS .004"

- 3. TYPICAL BOND PAD IS .004" SQUARE

- 4. BOND PAD METALIZATION: GOLD

- 5. BACKSIDE METALIZATION: GOLD

- 6. BACKSIDE METAL IS GROUND

- 7. NO CONNECTION REQUIRED FOR UNLABELED BOND PADS

- 8. OVERALL DIE SIZE ±.002"

| PAD | DESCRIPTION | PAD SIZE                  |

|-----|-------------|---------------------------|

| 1   | RFIN        | .0021[.054] X .0021[.054] |

| 2   | Vgg1        | .0041[.104] X .0041[.104] |

| 3   | Vdd1        | .0041[.104] X .0041[.104] |

| 4   | Vgg2        | .0041[.104] X .0041[.104] |

| 5   | Vdd2        | .0041[.104] X .0041[.104] |

| 6   | RFOUT       | .0021[.054] X .0021[.054] |

Figure 1 – Device Outline for the HMC8243

SID000019 Rev. A | Page 6 of 8

## **TABLE IV: DIE PACKAGING INFORMATION**

| Standard Package | Alternate  |

|------------------|------------|

| GP-1 (Gel Pack)  | <u>1</u> / |

TABLE IV Note:

<u>1</u>/ For alternate packaging information, contact Analog Devices Inc.

## **ORDERING GUIDE**

| Model   | Temperature Range |

|---------|-------------------|

| HMC8243 | –10 °C to +45 °C  |

## **Revision History**

|     | Revision History      |            |  |  |  |

|-----|-----------------------|------------|--|--|--|

| Rev | Description of Change | Date       |  |  |  |

| А   | Initial release.      | 10/04/2024 |  |  |  |

|     |                       |            |  |  |  |

© 2024 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective companies. Printed in the U.S.A. 09/2024

www.analog.com

SID000019 Rev. A | Page 8 of 8