# 5V/2A, Synchronous No-Opto Isolated Flyback DC-DC Converter Using MAX17690 and MAX17606

MAXREFDES1022

#### Introduction

Due to its simplicity and low cost, the flyback converter is the preferred choice for low-to-medium isolated DC-DC power-conversion applications. However, the use of an optocoupler or an auxiliary winding on the flyback transformer for voltage feedback across the isolation barrier increases the number of components and design complexity. The MAX17690 eliminates the need for an optocoupler or auxiliary transformer winding and achieves ±5% output voltage regulation over line, load, and temperature variations.

The MAX17690 implements an innovative algorithm to accurately determine the output voltage by sensing the reflected voltage across the primary winding during the flyback time interval. By sampling and regulating this reflected voltage when the secondary current is close to zero, the effects of secondary-side DC losses in the transformer winding, the PCB tracks, and the rectifying diode on output voltage regulation can be minimized.

The MAX17690 also compensates for the negative temperature coefficient of the rectifying diode.

Other features include the following:

- 4.5V to 60V Input Voltage Range

- Programmable Switching Frequency from 50kHz to 250kHz

- Programmable Input Enable/UVLO Feature

- Programmable Input Overvoltage Protection

- Adjustable Soft-Start

- 2A/4A Peak Source/Sink Gate Drive Capability

- Hiccup Mode Short-Circuit Protection

- Fast Cycle-by-Cycle Peak Current Limit

- Thermal Shutdown Protection

- Space-Saving, 16-Pin, 3mm x 3mm TQFN Package

- -40°C to +125°C Operating Temperature Range

#### **Hardware Specification**

An isolated no-opto flyback DC-DC converter using the MAX17690 and MAX17606 is demonstrated for a 5V DC output application. The power supply delivers up to 2A at 5V. Table 1 shows an overview of the design specification.

**Table 1. Design Specification**

| PARAMETER                     | SYMBOL             | MIN    | MAX  |

|-------------------------------|--------------------|--------|------|

| Input Voltage                 | V <sub>IN</sub>    | 10V    | 50V  |

| Frequency                     | f <sub>SW</sub>    | 128kHz |      |

| Efficiency at Full Load       | $\eta_{MAX}$       | 85%    |      |

| Efficiency at Minimum<br>Load | η <sub>MIN</sub>   | 55%    |      |

| Output Voltage                | Vo                 | 4.9V   | 5.1V |

| Output Voltage Ripple         | $\Delta V_{O(SS)}$ | 100mV  |      |

| Output Current                | Io                 | 0.2A   | 2.0A |

| Maximum Output Power          | Po                 | 10W    |      |

#### Designed-Built-Tested

This document describes the hardware shown in Figure 1. It provides a detailed systematic technical guide to designing an isolated no-opto flyback DC-DC converter using Maxim's MAX17690 controller. The power supply has been built and tested.

Figure 1. MAXREFDES1022 hardware.

Rev 0; 10/17 Maxim Integrated | 1

#### The Isolated No-Opto Flyback Converter

One of the drawbacks encountered in most isolated DC-DC converter topologies is that information relating to the output voltage on the isolated secondary side of the transformer must be communicated back to the primary side to maintain output voltage regulation. In a regular isolated flyback converter, this is normally achieved using an optocoupler feedback circuit or an additional auxiliary winding on the flyback transformer. Optocoupler feedback circuits reduce overall power-supply efficiency, and the extra components increase the cost and physical size of the power supply. In addition, optocoupler feedback circuits are difficult to design reliably due to their limited bandwidth, nonlinearity, high CTR variation, and aging effects. Feedback circuits employing auxiliary transformer windings also exhibit deficiencies. Using an extra winding adds to the flyback transformer's complexity, physical size, and cost, while load regulation and dynamic response are often poor.

The MAX17690 is a peak current-mode controller designed specifically to eliminate the need for optocoupler or auxiliary transformer winding feedback in the traditional isolated flyback topology, therefore reducing size, cost, and design complexity. It derives information about

the isolated output voltage by examining the voltage on the primary-side winding of the flyback transformer.

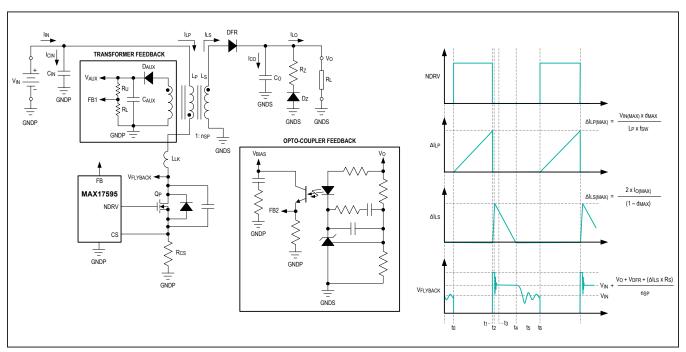

Other than this uniquely innovative method for regulating the output voltage, the no-opto isolated flyback converter using the MAX17690 follows the same general design process as a traditional flyback converter. To understand the operation and benefits of the no-opto flyback converter it is useful to review the schematic and typical waveforms of the traditional flyback converter (using the MAX17595), shown in Figure 2.

The simplified schematic in Figure 2 illustrates how information about the output voltage is obtained across the isolation barrier in traditional isolated flyback converters. The optocoupler feedback mechanism requires at least 10 components including an optocoupler and a shunt regulator, in addition to a primary-side bias voltage, V<sub>BIAS</sub>, to drive the photo-transistor. The error voltage FB2 connects to the FB pin of the flyback controller.

The transformer feedback method requires an additional winding on the primary side of the flyback transformer, a diode, a capacitor, and two resistors to generate a voltage proportional to the output voltage. This voltage is compared to an internal reference in a traditional flyback controller to generate the error voltage.

Figure 2. Isolated flyback converter topology with typical waveforms.

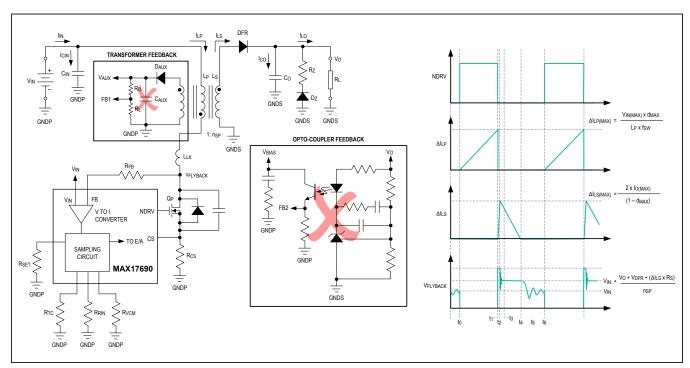

By including additional innovative features internally in the MAX17690 no-opto flyback controller, Maxim has enabled power-supply designers to eliminate the additional components, board area, complexity, and cost associated with both the optocoupler and transformer feedback methods. Figure 3 illustrates a simplified schematic and typical waveforms for an isolated no-opto flyback DC-DC converter using the MAX17690.

By comparing Figure 3 with Figure 2, it is evident that there is no difference in the voltage and current waveforms in the traditional and no-opto flyback topologies. The difference is in the control method used to maintain  $V_{\rm O}$  at its target value over the required load, line, and temperature range. The MAX17690 achieves this with minimum components by forcing the voltage  $V_{\rm FLYBACK}$  during the conduction period of DFR to be precisely the voltage required to maintain a constant  $V_{\rm O}$ . When  $Q_{\rm P}$  turns off, DFR conducts and the drain voltage of  $Q_{\rm P}$ , rises to a voltage  $V_{\rm FLYBACK}$  above  $V_{\rm IN}$ . After initial ringing due to transformer leakage inductance and the junction capacitance of DFR and output capacitance of  $Q_{\rm P}$ , the voltage  $V_{\rm FLYBACK}$  is given by:

$$V_{FLYBACK} = V_{IN} + \frac{\left(V_O + V_{DFR}(T) + I_{LS}(t) \times R_S(T)\right)}{n_{SP}}$$

where:

$V_{\text{FLYBACK}}$  is the  $Q_P$  drain voltage relative to primary ground  $V_{\text{DFR}}(T)$  is the forward voltage drop of DFR, which has a negative temperature coefficient

$I_{LS}(t)$  is the instantaneous secondary transformer current  $R_S(T)$  is the total DC resistance of the secondary circuit, which has a positive temperature coefficient

$\ensuremath{n_{\text{SP}}}$  is the secondary to primary turns ratio of the flyback transformer

The voltage of interest is  $(V_{FLYBACK} - V_{IN})$  since this is a measure of  $V_O$ . An internal voltage to current amplifier generates a current proportional to  $(V_{FLYBACK} - V_{IN})$ . This current then flows through  $R_{SET}$  to generate a ground referenced voltage,  $V_{SET}$ , proportional to  $(V_{FLYBACK} - V_{IN})$ . This requires that:

$$\frac{V_{FLYBACK} - V_{IN}}{R_{FB}} = \frac{V_{SET}}{R_{SET}}$$

Combining this equation with the previous equation for  $V_{\text{FLYBACK}}$ , we have:

$$V_{O} = V_{SET} \times \left(\frac{R_{FB}}{R_{SET}}\right) \times n_{SP} - V_{DFR}(T) - I_{LS}(t) \times R_{S}(T)$$

Figure 3. Isolated no-opto flyback converter topology with typical waveforms.

#### **Temperature Compensation**

We need to consider the effect of the temperature dependence of  $V_{\rm DFR}$  and the time dependence of  $I_{\rm LS}$  on the control system. If  $V_{\rm FLYBACK}$  is sampled at a time when  $I_{\rm LS}$  is very close to zero, then the term  $I_{\rm LS}(t)$  x  $R_{\rm S}(T)$  is negligible and can be assumed to be zero in the previous expression. This is the case when the flyback converter is operating in, or close to, discontinuous conduction mode. It is very important to sample the  $V_{\rm FLYBACK}$  voltage before the secondary current reaches zero since there is a very large oscillation on  $V_{\rm FLYBACK}$  due to the resonance between the primary magnetizing inductance of the flyback transformer and the output capacitance of  $Q_{\rm P}$  as soon as the current reaches zero in the secondary, as shown in Figures 2 and 3. The time at which  $V_{\rm FLYBACK}$  is sampled is set by resistor  $R_{\rm VCM}$ .

The V<sub>DFR</sub> term has a significant negative temperature coefficient that must be compensated to ensure acceptable output voltage regulation over the required temperature range. This is achieved by internally connecting a positive temperature coefficient current source to the V<sub>SET</sub> pin. The current is set by resistor R<sub>TC</sub> connected to ground. The simplest way to understand the temperature compensation mechanism is to think about what needs to happen in the control system when temperature increases. In an uncompensated system, as the temperature increases, V<sub>DFR</sub> decreases due to its negative temperature coefficient. Since V<sub>DFR</sub> decreases, V<sub>O</sub> increases by the same amount, therefore  $V_{\text{FLYBACK}}\xspace$  remains unchanged. Since  $V_{\text{SET}}$  is proportional to  $V_{\text{FLYBACK}},\,V_{\text{SET}}$  also remains unchanged. Since there is no change in  $V_{\text{SET}}$  there is no change in duty cycle demand to bring Vo back down to its target value. What needs to happen in the temperature compensated case is, when Vo increases due to the negative temperature coefficient of V<sub>DFR</sub>, V<sub>SET</sub> needs to increase by an amount just sufficient to bring Vo back to its target value. This is achieved by designing V<sub>SET</sub> with a positive temperature coefficient. Expressed mathematically as:

$$\frac{\delta V_{DFR}}{\delta_T} \times \frac{1}{n_{SP}} + \frac{\delta V_{TC}}{\delta_T} \times \frac{R_{FB}}{R_{TC}} = 0$$

where:

$\delta V_{DFR}/\delta T$  is the diodes forward temperature coefficient  $\delta V_{TC}/\delta T=1.85mV/^{\circ}C$

$V_{TC}$  = 0.55V is the voltage at the TC pin at +25°C. Rearranging the above expression gives:

$$R_{TC} = -R_{FB} \times n_{SP} \times \frac{\delta T}{\delta V_{DFR}} \times \frac{\delta V_{TC}}{\delta T}$$

The effect of adding the positive temperature coefficient current, TC, to the current in  $R_{FB}$  is equivalent to adding a positive temperature coefficient voltage in series with  $V_{DFR}$  on the secondary side of value:

$$\frac{V_{TC}}{R_{TC}} \times R_{FB} \times n_{SP}$$

Substituting from the previous expression, this becomes:

$$-V_{TC} \times \frac{\delta V_{DFR}}{\delta T} \times \frac{\delta T}{\delta V_{TC}}$$

We can now substitute this expression into the expression for  $V_{\Omega}$  as follows:

$$V_{o} = V_{SET} \times \left(\frac{R_{FB}}{R_{SET}}\right) \times n_{SP} - V_{DFR} - V_{tc} \times \frac{\delta V_{DFR}}{\delta T} \times \frac{\delta T}{\delta V_{tc}}$$

and finally solve for R<sub>FB</sub>:

$$R_{FB} = \frac{R_{SET}}{n_{SP} \times V_{SET}} \times \left\{ V_{O} + V_{DFR} + V_{TC} \times \frac{\delta V_{DFR}}{\delta T} \times \frac{\delta T}{\delta V_{TC}} \right\}$$

Values for  $R_{SET}$ ,  $V_{SET}$ , and  $\delta V_{TC}/\delta T$  can be obtained from the MAX17690 data sheet as follows:

$R_{SFT} = 10k\Omega$

$V_{SFT} = 1V$

$\delta V_{TC}/\delta T = 1.85 \text{mV/}^{\circ} \text{C}$

Values for  $V_{DFR}$  and  $\delta V_{DFR}/\delta T$  can be obtained from the output diode data sheet, and  $n_{SP}$  is calculated when the flyback transformer is designed.

The value of  $R_{\text{TC}}$  can then be calculated using the expression from earlier, restated below:

$$R_{TC} = -R_{FB} \times n_{SP} \times \frac{\delta T}{\delta V_{DFR}} \times \frac{\delta V_{TC}}{\delta T}$$

The calculated resistor values for  $R_{\text{FB}}$  and  $RT_{\text{C}}$  should always be verified experimentally and adjusted, if necessary, to achieve optimum performance over the required temperature range. Note that the reference design described in this document has only been verified at room temperature.

Finally, the internal temperature compensation circuitry requires a current proportional to  $V_{\text{IN}}$ .  $R_{\text{RIN}}$  should be chosen as approximately:

$$R_{RIN} = 0.6 \times R_{FR}$$

#### Setting the V<sub>FLYBACK</sub> Sampling Instant

The MAX17690 generates an internal voltage proportional to the on-time volt-second product. This enables the device to determine the correct sampling instant for  $V_{\text{FLYBACK}}$  during the  $Q_P$  off-time. The  $R_{\text{VCM}}$  resistor is used to scale this internal voltage to an acceptable internal voltage limit in the device. Selection of this resistor is described in detail in the MAX17690 data sheet.

# Designing the No-Opto Flyback Converter Using MAX17690

Now that the principle difference between a traditional isolated flyback converter using optocoupler or auxiliary transformer winding feedback and the isolated no-opto flyback converter using the MAX17690 is understood, a practical design example can be illustrated. The converter design process can be divided into three parts: the power stage design, the setup of the MAX17690 no-opto flyback controller, and closing the control loop. This document is intended to complement the information contained in the MAX17690 data sheet.

The following design parameters are used throughout this document:

| SYMBOL             | FUNCTION                           |

|--------------------|------------------------------------|

| V <sub>IN</sub>    | Input voltage                      |

| V <sub>UVLO</sub>  | Undervoltage turn-on threshold     |

| V <sub>ovi</sub>   | Overvoltage turn-off threshold     |

| t <sub>ss</sub>    | Soft-start time                    |

| Vo                 | Output voltage                     |

| $\Delta V_{O(SS)}$ | Steady-state output ripple voltage |

| I <sub>o</sub>     | Output current                     |

| I <sub>O(CL)</sub> | Maximum current-limit threshold    |

| Po                 | Nominal output power               |

| $\eta_{(MAX)}$     | Target efficiency at maximum load  |

| η <sub>(MIN)</sub> | Target efficiency at minimum load  |

| P <sub>IN</sub>    | Input power                        |

| f <sub>SW</sub>    | Switching frequency                |

| d                  | Duty cycle                         |

| n <sub>SP</sub>    | Secondary-primary turns ratio      |

These symbols are sometimes followed by parentheses to indicate whether minimum or maximum values of the parameters are intended, for example, the symbol  $V_{\text{IN}(\text{MIN})}$  is minimum input voltage. In addition, throughout the design procedure reference is made to the schematic.

#### **Part I: Designing the Power Components**

#### Step 1: Choose a Maximum Duty Cycle

The maximum duty cycle, d<sub>MAX</sub>, occurs at maximum output power, P<sub>O(MAX)</sub>, and minimum input voltage, V<sub>IN(MIN)</sub>. The MAX17690 no-opto flyback controller uses peak current-mode control. Switching power converters using peak current-mode control exhibit subharmonic oscillations at duty cycles greater than 50% unless slope compensation is added to the sensed primary MOSFET current. Slope compensation is added internally in the MAX17690 to allow stable operation up to duty cycles of 66%, as specified in the data sheet. Choosing the maximum allowable duty cycle ensures the highest energy density for the power converter. For the current design, we have chosen:

$$d_{MAX} = 0.65$$

#### Step 2: Calculate the Minimum Duty Cycle

The MAX17690 derives the current ( $\Delta I_{LP}$ ) in the primary magnetizing inductance by measuring the voltage ( $\Delta V_{RCS}$ ) across the current-sense resistor ( $R_{CS}$ ) during the on-time of the MOSFET. So:

$$\Delta I_{LP} = \frac{\Delta V_{RCS}}{R_{CS}}$$

$\Delta I_{LP}$  is a maximum at  $d_{MAX}$  and  $V_{IN(MIN)}$  and is a minimum at  $d_{MIN}$  and  $V_{IN(MAX)}$  so:

$$\frac{V_{IN(MIN)}}{L_{P}} = \frac{\Delta V_{RCS(MAX)} \times f_{SW}}{R_{CS} \times d_{MAX}}$$

and

$$\frac{V_{IN(MAX)}}{L_{P}} = \left(\frac{\eta_{max}}{\eta_{min}} \times \frac{\Delta V_{RCS(min)}}{R_{cs}}\right) \times \frac{f_{SW}}{d_{min}}$$

Solving the two equations above, we have:

$$d_{min} = d_{max} \times \frac{\eta_{max}}{\eta_{min}} \times \frac{V_{IN(MIN)}}{V_{IN(MAX)}} \times \frac{\Delta V_{RCS(min)}}{\Delta V_{RCS(max)}}$$

where  $\Delta V_{RCS(MIN)}$  and  $\Delta V_{RCS(MAX)}$  correspond to the minimum current limit threshold (20mV) and the maximum current limit threshold (100mV) of the MAX17690, respectively. So, for  $V_{IN(MIN)}$  = 10V,  $V_{IN(MAX)}$  = 50V, and  $d_{MAX}$  = 0.65, we have:

$$d_{MIN} \approx 0.04$$

## **Step 3: Calculate the Maximum Allowable Switching Frequency**

The isolated no-opto flyback topology requires the primary side MOSFET to constantly maintain switching, otherwise there is no way to sense the reflected secondary-side voltage at the drain of the primary-side MOSFET. The MAX17690 achieves this by having a critical minimum on-time,  $t_{\rm ON(CRIT)}$ , for which it drives the MOSFET. At a given switching frequency  $t_{\rm ON(MIN)}$  corresponds to  $d_{\rm MIN}$ . From the data sheet, the critical minimum on-time  $t_{\rm ON(CRIT)}$  for the MOSFET drive output NDRV is 235ns. We can therefore calculate the maximum switching frequency as follows:

$$f_{SW(MAX)} = \frac{d_{MIN}}{t_{ON(CRIT)}} \approx 171,000Hz$$

Since  $d_{MIN}$  is fixed by  $\Delta V_{RCS(MIN)}$ ,  $\Delta V_{RCS(MAX)}$ ,  $d_{MAX}$ ,  $V_{IN(MIN)}$ , and  $V_{IN(MAX)}$ , we can choose a  $t_{on(MIN)}$ , which is arbitrarily larger than  $t_{ON(CRIT)}$  to allow a reasonable design margin. So, if we choose  $t_{ON(MIN)} = 315$ ns we obtain a new switching frequency as follows:

$$f_{SW} = \frac{d_{MIN}}{t_{ON(MIN)}} \approx 128,000Hz$$

Note that the MAX17690 should always be operated in the switching frequency range from 50kHz to 250kHz and  $t_{\text{ON(MIN)}}$  must be chosen accordingly to ensure that this constraint is met.

## **Step 4: Calculate Primary Magnetizing Inductance** Maximum input power is given by:

$$P_{IN(MAX)} = \frac{P_{O(MAX)}}{\eta_{MAX}} = \frac{V_{O} \times I_{O(CL))}}{\eta_{MAX}}$$

For the discontinuous flyback converter all the energy stored in the primary magnetizing inductance,  $L_P$ , during the MOSFET on-time is transferred to the output during the MOSFET off-time, i.e., the full power transfer occurs during one switching cycle. Therefore, because  $E = P \times t$ , we have:

$$\mathsf{E}_{\mathsf{IN}(\mathsf{MAX})} = \mathsf{P}_{\mathsf{IN}(\mathsf{MAX})} \times \tau_{\mathsf{SW}} = \frac{\mathsf{V}_{\mathsf{O}} \times \mathsf{I}_{\mathsf{O}(\mathsf{CL})}}{\eta_{\mathsf{MAX}} \times \mathsf{f}_{\mathsf{SW}}}$$

The maximum input energy must be stored in  $L_P$  during the on-time of the MOSFET, so:

$$E_{IN(MAX)} = \frac{1}{2} \times L_P \times \Delta I_{LP(MAX)}^2$$

We also know that the peak current in L<sub>P</sub>,  $\Delta I_{LP(MAX)}$  occurs at input voltage  $V_{IN(MIN)}$  and MOSFET on-time  $t_{ON(MAX)}$ . So:

$$V_{IN(MIN)} = L_P \times \frac{\Delta I_{LP(MAX)}}{t_{ON(MAX)}}$$

Rearranging this equation and squaring, we have:

$$\Delta I_{LP(MAX)}^2 = \frac{V_{IN(MIN)}^2 \times t_{ON(MAX)}^2}{L_p^2}$$

and substituting:

$$\mathsf{E}_{\mathsf{IN}(\mathsf{MAX})} = \frac{\mathsf{V}_{\mathsf{IN}(\mathsf{MIN})}^2 \times \mathsf{t}_{\mathsf{ON}(\mathsf{MAX})}^2}{2 \times \mathsf{Lp}}$$

we now have:

$$\frac{V_{IN(MIN) \times}^{2} t_{ON(MAX)}^{2}}{2 \times L_{P}} = \frac{V_{O \times} I_{O(CL)}}{\eta_{MAX} \times f_{SW}}$$

Finally, by rearranging we have an expression for the primary magnetizing inductance L<sub>P</sub>:

$$L_{P} = \frac{\eta_{MAX} \times V_{IN(MIN)}^{2} \times d_{MAX}^{2}}{2 \times V_{O} \times I_{O(CL)} \times f_{SW}}$$

If we estimate the power converter efficiency  $\eta_{MAX}$  = 0.85, then with  $V_{IN(MIN)}$  = 10V,  $d_{MAX}$  = 0.65,  $V_{O}$  = 5V,  $I_{O(CL)}$  = 2.2A, and  $f_{SW}$  = 128,000Hz, we have:

$$L_{P(MAX)} \approx 12.8 \mu H$$

This primary inductance represents the maximum primary inductance since it sets the current-limit threshold. Choosing a larger inductance will set the current-limit threshold at a lower value which would be undesirable. Assuming a  $\pm 10\%$  tolerance for the primary inductance gives:

## Step 5: Calculate the Secondary to Primary Turns Ratio for the Flyback Transformer

Assume we are operating at the border between discontinuous and continuous conduction modes at  $V_{\text{IN(MIN)}}$  and  $P_{\text{O(MAX)}}$ . Under this condition, the primary-side MOSFET is conducting for  $(d_{\text{MAX}} \times \tau_{\text{SW}})$  and the secondary-side synchronous rectifier (or diode) is conducting for  $(1 - d_{\text{MAX}}) \times \tau_{\text{SW}}$ . Ideally, the primary volt-seconds per turn must balance with the secondary volt-seconds per turn; however, in practice, the primary to secondary coupling of the transformer is not perfect (giving rise to uncoupled leakage inductance) and both windings have series resistance. Effectively, this means that to obtain the required

volt-seconds per turn on the secondary winding we need more volt-seconds per turn on the primary winding. We introduce a transformer efficiency factor,  $\eta_T$ , so that:

$$\frac{V_{IN\left(MIN\right)} \times d_{MAX} \times \tau_{SW}}{\eta_{T} \times N_{P}} = \frac{\left(V_{O} + V_{F}\right) \times \left(1 - d_{MAX}\right) \times \tau_{SW}}{N_{S}}$$

and

$$n_{SP} = \frac{N_S}{N_P} = \frac{\eta_T \times (V_O + V_F) \times (1 - d_{MAX})}{V_{IN(MIN)} \times d_{MAX}}$$

Assuming  $\eta_T$  = 0.9 and  $V_F$  = 0.5V (for a synchronous rectifier), then with  $V_O = 5V$ ,  $d_{MAX} = 0.65$ , and  $V_{IN(MIN)} =$ 10V, we have:

$$n_{SP} \approx 0.27$$

Typical values of  $\eta_T$  range from 0.65 for an inefficient transformer design to 0.99 for a very efficient transformer design.

#### Step 6: Calculate the Peak and RMS Currents in the Primary Winding of the Flyback Transformer

The peak primary winding current occurs at V<sub>IN(MIN)</sub> and d<sub>MAX</sub> according to the following equation:

$$\Delta I_{LP\left(MAX\right)} = \frac{V_{IN\left(MIN\right)} \times d_{MAX}}{L_P \times f_{SW}} \approx 4.8A$$

The RMS primary winding current can be calculated from  $\Delta I_{LP(MAX)}$  and  $d_{MAX}$  as follows:

$$I_{LP\left(RMS\right)} = \Delta I_{LP\left(MAX\right)} \times \sqrt{\frac{d_{MAX}}{3}} \approx 2.23A$$

#### Step 7: Calculate the Peak and RMS Currents in the **Secondary Winding of the Flyback Transformer**

Again, assuming we are operating at the border between discontinuous and continuous conduction modes at  $V_{IN(MIN)}$  and  $P_{O(MAX)}$ . The peak secondary winding current is related to  $I_{O(MAX)}$  and  $d_{MAX}$  as follows:

$$\Delta I_{LS(MAX)} = \frac{2 \times I_{O(MAX)}}{(1 - d_{MAX})} \approx 14.28A$$

The RMS secondary winding current can be calculated from  $\Delta I_{LS(MAX)}$  and  $d_{MAX}$  as follows:

$$I_{S\left(RMS\right)} = \Delta I_{LS\left(MAX\right)} \times \sqrt{\frac{\left(1 - d_{MAX}\right)}{3}} \approx 4.9A$$

#### Step 8: Summarize the Flyback Transformer Specification

We now have all the critical parameters of the flyback transformer:

| PARAMETER                                     | SYMBOL               | VALUE     |

|-----------------------------------------------|----------------------|-----------|

| Primary Magnetizing Inductance                | L <sub>P</sub>       | 12µH ±10% |

| Primary Peak Current                          | I <sub>LP(MAX)</sub> | 4.8A      |

| Primary RMS Current                           | I <sub>P(RMS)</sub>  | 2.23A     |

| Turns Ratio (N <sub>S</sub> /N <sub>P</sub> ) | n <sub>SP</sub>      | 0.25      |

| Secondary Peak Current                        | I <sub>LS(MAX)</sub> | 14.3A     |

| Secondary RMS Current                         | I <sub>S(RMS)</sub>  | 4.9A      |

Using the parameters in the table above, a suitable transformer can be designed.

#### **Step 9: Calculate Design Parameters for** Secondary-Side Rectifying Device

Depending on the output voltage and current, a choice can be made for the secondary-side rectifying device. Generally, for output voltages above 12V at low current (less than 1A), a Schottky diode is used, and for voltages less than 12V a synchronous switch is used. The current design is 5V/2A output, so we will outline a procedure for selecting a suitable MOSFET for the synchronous switch.

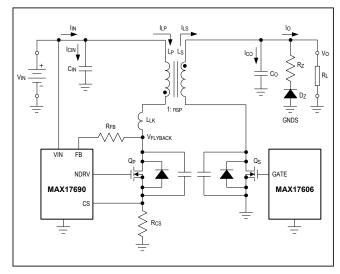

Figure 4 shows a simplified schematic with the synchronous switch Q<sub>s</sub>. The MAX17606 is a secondary-side synchronous driver and controller specifically designed for the isolated flyback topology operating in Discontinuous Conduction Mode (DCM) or Border Conduction Mode (BCM).

The important parameters to consider for the synchronous rectifying device are the same as those of a regular rectifying diode: peak instantaneous current, RMS current, voltage stress, and power losses. Since Q<sub>S</sub> and L<sub>S</sub>

Figure 4. Simplified no-opto flyback schematic with synchronous rectification.

are in series, they experience the same peak and RMS currents, so:

$$I_{QS(MAX)} = \frac{2 \times I_{O(MAX)}}{(1 - d_{MAX})} \approx 14.28A$$

and

$$I_{QS\left(RMS\right)} = I_{QS\left(MAX\right)} \times \sqrt{\frac{\left(1 - d_{MAX}\right)}{3}} \approx 4.9A$$

When  $Q_S$  is off,  $V_{IN}$  reflected to the secondary side of the flyback transformer plus  $(V_O + V_{QS(SAT)})$  is applied across the drain-source of  $Q_S$ , so:

$$V_{QS(MAX)} = n_{SP} \times V_{IN(MAX)} + V_O + V_{QS(SAT)}$$

= 0.25 x 50V + 5V +(14.28A x 32.5m $\Omega$ )

$\approx$  18V

$Q_S$  has both conduction losses due to its  $R_{DS(ON)}$  and switching losses. Allowing for reasonable design margin, Vishay part number SiR836DP was chosen for this design with the following specifications:

| PARAMETER                                           | VALUE  |

|-----------------------------------------------------|--------|

| Maximum D-S Voltage                                 | 40V    |

| Continuous Drain Current                            | 4.1A   |

| Pulsed Drain Current                                | 20A    |

| D-S Resistance at V <sub>GS</sub> = 7.5V            | 32.5mΩ |

| Minimum V <sub>GS</sub> Threshold V <sub>GSTH</sub> | 1.2V   |

| Typical V <sub>GS</sub> Plateau V <sub>GSPL</sub>   | 2.7V   |

| Maximum Q <sub>G(T)</sub>                           | 18nC   |

| Typical Q <sub>GD</sub>                             | 2.1nC  |

| Total Output Capacitance C <sub>OSS</sub>           | 100pF  |

The power losses in the  $Q_{\mbox{\scriptsize S}}$  can be approximated as follows:

$$P_{TOT} = P_{CON} + P_{CDS} + P_{SW} \approx 785 \text{mW}$$

where:

$P_{CON}$  is the loss due to  $I_{QS(RMS)}$  flowing through the drain-source on resistance of  $Q_S$ :

$$P_{CON} = I_{QS(RMS)}^2 \times R_{DS(ON)} \approx 780 \text{mW}$$

$\mathsf{P}_{\mathsf{CDS}}$  is the loss due to the energy in the drain-source output capacitance being dissipated in  $\mathsf{Q}_{\mathsf{S}}$  at turn-on:

$$P_{CDS} = \frac{1}{2} \times f_{SW} \times C_{OSS} \times V_{QS(MAX)}^2 \approx 2mW$$

and  $P_{\text{SW}}$  is the turn-on voltage-current transition loss that occurs as the drain-source voltage decreases and the drain current increases during the turn-on transition:

$$\begin{aligned} P_{SW} &= \frac{1}{2} \times f_{SW} \times I_{QS(t-ON)} \times \\ &\left\{ \frac{V_{GS(PL)} - V_{GS(TH)}}{V_{GS(PL)}} \times \left( \frac{Q_{G(TOT)} + Q_{GD}}{I_{DRV}} \right) \right\} \end{aligned}$$

where  $I_{\text{DRV}}$  is the maximum drive current capability of the GATE output of the MAX17606 and  $I_{\text{QS(t-ON)}}$  is the instantaneous current in  $Q_{\text{S}}$  at turn-on.  $I_{\text{QS(t-ON)}}$  is equal to  $I_{\text{QS(MAX)}}$ .

#### Step 10: Calculate Design Parameters for Primary-Side MOSFET

The important parameters to consider for the primary-side MOSFET ( $Q_P$ ) are peak instantaneous current, RMS current, voltage stress, and power losses. Because  $Q_P$  and  $L_P$  are in series they experience the same peak and RMS currents, so from Step 6:

$$I_{OP(MAX)} = I_{LP(MAX)} \approx 4.8A$$

and

$$I_{QP(RMS)} = I_{LP(RMS)} \approx 2.23A$$

When  $Q_P$  turns off,  $V_O$  reflected to the primary side of the flyback transformer plus  $V_{\text{IN(MAX)}}$  is applied across the drain-source of  $Q_P$ . In addition, until  $Q_S$  starts to conduct, there is no path for the leakage inductance energy to flow through. This causes the drain-source voltage of  $Q_P$  to rise even further. The factor of (1.5) in the equation below represents this additional voltage rise; however, this factor can be higher or lower depending on the transformer and PCB leakage inductances:

$$V_{QP(MAX)} \approx 1.5 \times \left(\frac{V_{O} + V_{QS(SAT)}}{n_{SP}}\right) + V_{IN(MAX)} \approx 83V_{QP(MAX)}$$

Allowing for reasonable design margin, Vishay part number SiR872ADP was chosen for this design with the following specifications:

| PARAMETER                                           | VALUE |  |

|-----------------------------------------------------|-------|--|

| Maximum D-S Voltage                                 | 150V  |  |

| Continuous Drain Current                            | 53.7A |  |

| Pulsed Drain Current                                | 100A  |  |

| D-S Resistance at V <sub>GS</sub> = 7.5V            | 40mΩ  |  |

| Minimum V <sub>GS</sub> Threshold V <sub>GSTH</sub> | 2.5V  |  |

| Typical V <sub>GS</sub> Plateau V <sub>GSPL</sub>   | 6V    |  |

| Maximum Q <sub>G(T)</sub>                           | 47nC  |  |

| Typical Q <sub>GD</sub>                             | 10nC  |  |

| Total Output Capacitance C <sub>OSS</sub>           | 327pF |  |

The power losses in the  $Q_{\text{p}}$  can be approximated as follows:

$$P_{TOT} = P_{CON} + P_{CDS} + P_{SW} \approx 310 \text{mW}$$

where:

$P_{CON}$  is the loss due to  $I_{QP(RMS)}$  flowing through the drain-source on resistance of  $Q_P$ :

$$P_{CON} = I_{QP(RMS)}^2 \times R_{DS(ON)} \approx 200 \text{mW}$$

$P_{\text{CDS}}$  is the loss due to the energy in the drain-source output capacitance being dissipated in  $Q_{\text{P}}$  at turn-on:

$$P_{CDS} = \frac{1}{2} \times f_{SW} \times C_{OSS} \times V_{QP(MAX)}^2 \approx 110 \text{mW}$$

And P<sub>SW</sub> is the turn-on voltage-current transition loss that occurs as the drain-source voltage decreases and the drain current increases during the turn-on transition:

$$\begin{split} P_{SW} &= \frac{1}{2} \times f_{SW} \times I_{QP(t-ON)} \times \\ &\left\{ \frac{V_{GS(PL)} - V_{GS(TH)}}{V_{GS(PL)}} \times \left( \frac{Q_{G(TOT)} + Q_{GD}}{I_{DRV}} \right) \right\} \approx 0 mW \end{split}$$

where  $I_{DRV}$  is the maximum drive current capability of the NDRV output of the MAX17690 and  $I_{QP(t\text{-ON})}$  is the instantaneous current in  $Q_P$  at turn-on. Since the flyback converter is operating in Discontinuous Conduction Mode,  $I_{QP(t\text{-ON})}$  is zero and therefore  $P_{SW}$  is also zero.

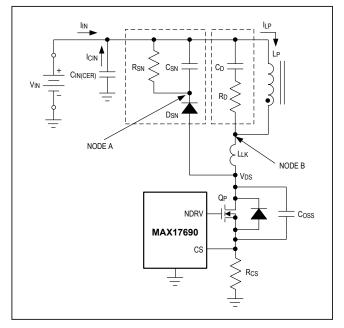

#### Step 11: Select the RCD Snubber Components

Referring to Figure 5, when  $Q_P$  turns off,  $I_{LP}$  charges the output capacitance,  $C_{OSS}$ , of  $Q_P$ . When the voltage across  $C_{OSS}$  exceeds the input voltage plus the reflected secondary to primary voltage, the secondary-side diode (or synchronous switch) turns on. Since the diode (or synchronous switch) is now on, the energy stored in the primary magnetizing inductance is transferred to the secondary; however, the energy stored in the leakage inductance will continue to charge  $C_{OSS}$  since there is nowhere else for it to go. Since the voltage across  $C_{OSS}$  is the same as the voltage across  $Q_P$ , if the energy stored in the leakage inductance charges  $C_{OSS}$  to a voltage level greater than the maximum allowable drain-source voltage of  $Q_P$ , the MOSFET fails.

One way to avoid this situation arising is to add a suitable RCD snubber across the primary winding of the transformer. In Figure 5, the snubber is labelled  $R_{SN}$ ,  $C_{SN}$ , and  $D_{SN}$ . In this situation, when  $Q_P$  turns off, the voltage at Node A is:

$$V_{NODEA} = V_{CSN} + V_{IN}$$

When the secondary-side diode (or synchronous switch) turns on, the voltage at Node B is:

$$V_{NODEB} = V_{IN} + \frac{V_O + V_F}{n_{SP}}$$

Figure 5. RCD snubber circuit.

So, the voltage across the leakage inductance is:

$$\begin{aligned} &V_{LLK} = V_{CSN} + V_{IN} - \left(V_{IN} + \frac{V_O + V_F}{n_{SP}}\right) \\ &= V_{CSN} - \left(\frac{V_O + V_F}{n_{SP}}\right) = L_{LK} \times \frac{\Delta I_{SN}}{\Delta t_{SN}} \end{aligned}$$

So:

$$\Delta t_{SN} = \frac{L_{LK} \times \Delta I_{SN}}{V_{CSN} - \left(\frac{V_O + V_F}{n_{SP}}\right)}$$

The average power dissipated in the snubber network is:

$$P_{SN} = V_{CSN} \times \frac{\Delta I_{SN} \times \Delta t_{SN}}{2 \times \tau_{SW}}$$

Substituting  $\Delta t_{SN}$  into this expression we have:

$$P_{SN} = \frac{1}{2} \times L_{LK} \times \Delta I_{SN}^2 \times \frac{V_{CSN}}{V_{CSN} - \left(\frac{V_O + V_F}{n_{SP}}\right)} \times f_{SW}$$

The leakage inductance energy is dissipated in  $R_{SN}$ , so from:

$$P_{SN} = \frac{V_{CSN}^2}{R_{SN}}$$

www.maximintegrated.com Maxim Integrated | 9

We can calculate the required R<sub>SN</sub> as follows:

$$R_{SN} = \frac{{V^2_{CSN}}}{\frac{1}{2} \times L_{LK} \times \Delta I^2_{SN} \times \frac{V_{CSN}}{V_{CSN} - \left(\frac{V_O + V_F}{n_{SP}}\right)} \times f_{SW}}$$

Over one switching cycle we must have:

$$I_{SN} = \frac{V_{CSN}}{R_{SN}} = C_{SN} \times \frac{\Delta V_{SN}}{\tau_{SW}}$$

So, we can calculate the required  $C_{SN}$  as follows:

$$C_{SN} = \frac{V_{CSN}}{\Delta V_{CSN} \times R_{SN} \times f_{SW}}$$

Generally,  $\Delta V_{CSN}$  should be kept to approximately 10% to 30% of  $V_{CSN}$ . Figure 6 illustrates  $V_{CSN}$ ,  $\Delta I_{SN}$ , and  $\Delta t_{SN}$ . The voltage across the snubber capacitor,  $V_{CSN}$ , should be selected so that:

$$V_{CSN} < Q_{P(DSMAX)} - V_{IN(MAX)}$$

Choosing too large a value for  $V_{CSN}$  causes the voltage on the drain of  $Q_P$  to get too close its maximum allowable drain-source voltage, while choosing too small a value results in higher power losses in the snubber resistor. A reasonable value should result in a maximum drain voltage on  $Q_P$  that is approximately 75% of its maximum allowable value. The worst-case condition for the snubber circuit occurs at maximum output power when:

$$\Delta I_{SN} = I_{LP(MAX)}$$

Assuming the leakage inductance is 2.5% of the primary inductance, then choosing  $V_{CSN} = 63V$  and  $\Delta V_{CSN} = 18V$ , we get the following approximate values:

$$P_{SN} = 810 \text{mW}$$

$R_{SN} = 5 \text{k}\Omega$

$C_{SN} = 4.7 \text{nF}$

Finally, we consider the snubber diode,  $D_{SN}$ . This diode should have at least the same voltage rating as the MOSFET,  $Q_P$ . Although the average forward current is very low, it must have a peak repetitive current rating greater than  $I_{LP(MAX)}$ .

### Step 12: Calculate the Required Current-Sense Resistor

From Step 4 we have the maximum input power given by:

$$P_{IN\left(MAX\right)} = \frac{P_{O}\left(MAX\right)}{\eta} = \frac{V_{O} \times I_{O}\left(MAX\right)}{\eta}$$

For the discontinuous flyback converter all the energy stored in the primary magnetizing inductance,  $L_P$ , during the MOSFET on-time is transferred to the output during the MOSFET off-time, i.e., the full power transfer occurs during one switching cycle. Therefore, since  $E = P \times t$ , we have:

$$E_{IN(MAX)} = P_{IN(MAX)} \times \tau_{SW} = \frac{V_O \times I_{O(MAX)}}{\eta \times f_{SW}}$$

The maximum input energy must be stored in  $L_P$  during the on-time of the MOSFET, so:

$$E_{IN(MAX)} = \frac{1}{2} \times L_P \times \Delta I_{LP(MAX)}^2$$

Figure 6. RCD snubber circuit waveforms.

Therefore:

$$\frac{1}{2} \times L_P \times \Delta I_{LP(MAX)}^2 = \frac{V_O \times I_O(MAX)}{\eta \times f_{SW}}$$

and

$$\Delta I_{LP} = \sqrt{\frac{2 \times V_O \times I_{O}(\text{MAX})}{\eta \times L_P \times f_{SW}}}$$

From Step 2 we have:

$$\Delta I_{LP} = \frac{\Delta V_{RCS}}{R_{CS}}$$

SO

$$R_{CS} = \Delta V_{RCS} \times \sqrt{\frac{\eta \times L_P \times f_{SW}}{2 \times V_O \times I_{O(MAX)}}}$$

Substituting values for  $\Delta V_{RCS},~\eta,~L_P,~f_{SW},~V_O,$  and  $I_{O(MAX)}$ we have:

$$R_{CS} \approx 21 \text{m}\Omega$$

where  $\Delta V_{RCS}$  = 100mV, the maximum CS current-limit threshold of the MAX17690. We can choose a standard  $20m\Omega$  resistor for R<sub>CS</sub>.

#### **Step 13: Calculate and Select the Input Capacitors**

Figure 7 shows a simplified schematic of the primary side of the flyback converter and the associated current waveforms. In steady-state operation, the converter draws a pulsed high-frequency current from the input capacitor, C<sub>IN</sub>. This current leads to a high-frequency ripple voltage across the capacitor according to the following expression:

$$I_{CIN} = C_{IN} \times \frac{\Delta V_{CIN}}{\Delta t}$$

It is the ripple voltage arising from the amp second product through the input capacitor.

During the  $Q_P$  on-time interval from  $t_0$  to  $t_1$ , the capacitor is supplying current to the primary inductance LP of the flyback transformer and its voltage is decreasing. During the Q<sub>P</sub> off-time time interval from t<sub>1</sub> to t<sub>2</sub>, no current is flowing in L<sub>P</sub>, and current is being supplied to capacitor from the input voltage source. According to the charge balance law, the decrease in capacitor voltage during time to t1 must equal the increase in capacitor voltage during time  $t_1$  to  $t_2$ . So:

$$I_{CIN[t_1tot_2]} = C_{IN} \times \frac{\Delta V_{CIN}}{(t_2 - t_1)} = \frac{V_O \times I_O}{\eta \times V_{IN}}$$

And finally, since:

$$\frac{1}{(t_2-t_1)} = \frac{f_{SW}}{(1-d)}$$

we have:

$$C_{IN} = \frac{V_O \times I_O}{\eta \times V_{IN}} \times \frac{1}{\Delta V_{CIN}} \times \frac{(1-d)}{f_{SW}}$$

For maximum high-frequency ripple voltage requirement  $\Delta V_{CIN}$ , we can now calculate the required minimum  $C_{IN}$ .

An additional high-frequency ripple voltage occurs at the input due to the ESR of the input capacitor. This ripple voltage is generally much smaller than the amp second product voltage ripple and can be minimized by choosing a capacitor with low ESR.

There is high-frequency AC current flowing in CIN, as shown in the center waveform of Figure 7. The selected capacitor must be specified to tolerate this maximum RMS current, I<sub>CIN(RMS)</sub>. From the simplified schematic:

$$I_{LP} = I_{IN} + I_{CIN}$$

Therefore:

$$I_{CIN(RMS)} = \sqrt{I_{LP(RMS)}^2 - I_{IN(RMS)}^2}$$

where:

$$I_{IN\left(RMS\right)} = \frac{V_O \times I_O}{\eta \times V_{IN}}$$

and from Step 6:

$$I_{LP(RMS)} = \Delta I_{LP} \times \sqrt{\frac{d}{3}}$$

So:

$$I_{CIN(RMS)} = \sqrt{\frac{d}{3} \times \Delta I_{LP}^2 - \frac{V_o^2 \times I_o^2}{\eta^2 \times V_{IN}^2}}$$

The maximum RMS current in the input capacitor occurs at  $d_{MAX}$ ,  $\Delta I_{LP(MAX)}$ ,  $I_{O(MAX)}$ , and  $V_{IN(MIN)}$ .

An additional high-frequency ripple voltage is present due to the RMS current flowing through the ESR of the capacitor. Ceramic capacitors are generally used for limiting high-frequency ripple due to their high AC current capability and low ESR.

Figure 7. Primary-side circuit and currents.

In addition to using a ceramic capacitor for high-frequency input ripple-voltage control as described above, an electrolytic capacitor is sometimes inserted at the input of a flyback converter to limit the input voltage deviation when there is a rapid output load change. A 100% load change gives rise to an input current transient of:

$$\Delta I_{IN(MAX)} = \frac{V_O \times I_{O(MAX)}}{\eta \times V_{IN(MIN)}}$$

During this transient, there is a voltage drop across any series stray inductance,  $L_{\text{IN}(\text{STRAY})}$ , that exists between the input voltage source and the input capacitor of the power supply. So from:

$$\frac{1}{2} \times C_{IN} \times \Delta V^{2}_{CIN} = \frac{1}{2} \times L_{IN(STRAY)} \times \Delta I^{2}_{IN}$$

we have:

$$C_{IN} = L_{IN(STRAY)} \times \frac{\Delta I_{IN(MAX)}^{2}}{\Delta V_{CIN}^{2}}$$

We now have two values for C<sub>IN</sub>. One for input high-frequency ripple-voltage control:

$$C_{IN(CER)} = \frac{V_o \times I_o}{\eta \times V_{IN}} \times \frac{1}{\Delta V_{CIN}} \times \frac{(1-d)}{f_{SW}}$$

and a second for transient input voltage control:

$$C_{IN(ELE)} = L_{IN(STRAY)} \times \frac{\Delta l_{IN(MAX)}^2}{\Delta V_{CIN}^2}$$

If  $C_{\text{IN(ELE)}} > C_{\text{IN(CER)}}$ , both ceramic and electrolytic capacitors must be used at the input of the power supply and  $\Delta V_{\text{CIN}}$  should be limited to approximately 75mV to keep the AC current in the ESR of the electrolytic capacitor within acceptable limits. Otherwise,  $C_{\text{IN(ELE)}}$  is not required. In this case, the value of  $C_{\text{IN(CER)}}$  can be significantly reduced since there is no longer any requirement to limit  $\Delta V_{\text{CIN}}$  to less than 75mV. Based on the current design specification, we have:

$$C_{IN(CER)} \approx 54 \mu$$

And:

$$C_{IN(ELE)} \approx 23\mu$$

Since  $C_{\text{IN(ELE)}} < C_{\text{IN(CER)}}$ , an electrolytic capacitor is not required. We can now recalculate  $C_{\text{IN(CER)}}$  based on a  $\Delta V_{\text{CIN}} = 400 \text{mV}$ :

$$C_{IN(CER)} \approx 10\mu$$

If we allow for a capacitor tolerance of  $\pm 10\%$  and a further reduction of capacitance of 70% due to the DC bias effect (operating an 80V ceramic capacitor at 50V), our final nominal value is:

$$C_{IN(CER)} \approx 30 \mu$$

We can achieve this by placing six  $4.7\mu F$  ceramic capacitors (Murata GRM32ER71K475KE14) in parallel. The AC current in each capacitor is:

$$\frac{I_{CIN}(RMS)}{6} \approx 0.27ARMS$$

which is well within specification for the selected capacitor.

#### Step 14: Calculate and Select the Output Capacitor

High-frequency ripple voltage requirements are also used to determine the value of the output capacitor in a flyback converter.

Figure 8 shows a simplified schematic of the secondary side of the flyback converter and the associated current waveforms.

In steady-state operation, the load draws a DC current from the secondary side of the flyback converter. By examining the secondary current waveforms, we see that  $C_{\rm O}$  is supplying the full output current  $I_{\rm O}$  to the load during the time interval from  $t_2$  to  $t_3$ . During this time interval, the voltage across  $C_{\rm O}$  decreases. At time  $t_3$ ,  $Q_{\rm P}$  has just turned off and the secondary rectifying diode DFR (or the secondary synchronous switch  $Q_{\rm S}$ ) starts to conduct supplying current to the load and to  $C_{\rm O}$ . The charging and discharging of  $C_{\rm O}$  leads to a high-frequency ripple voltage at the output according to the following expression:

$$I_{CO} = C_O \times \frac{\Delta V_{CO}}{\Delta t}$$

Again, as with the input capacitor, this is the ripple voltage arising from the amp second product through the output capacitor.

By the capacitor charge balance law, the decrease in capacitor voltage during time  $t_2$  to  $t_3$  must equal the increase in capacitor voltage during time  $t_1$  to  $t_2$ . When the capacitor is discharging, we have:

$$I_{CO[t_2 to t_3]} = C_O \times \frac{\Delta V_{CO}}{(t_3 - t_2)} = I_O$$

Finally, since:

$$\frac{1}{(t_3-t_2)} = \frac{f_{SW}}{d}$$

We have:

$$C_O = I_O \times \frac{1}{\Delta V_{CO}} \times \frac{d}{f_{SW}}$$

At maximum output current, the discontinuous flyback converter should ideally operates on the border between discontinuous and continuous conduction modes and so  $d_{\text{MAX}}$  should be substituted in the above equation.

For maximum high-frequency ripple voltage requirement  $\Delta V_{CO},$  we can now calculate the required minimum  $C_{O}.$

$$C_O \approx 220 \mu F$$

As with the input capacitor, an additional high-frequency ripple voltage occurs at the output due to the output capacitor's ESR and can be minimized by choosing a capacitor with low ESR.

Figure 8. Secondary-side circuit and currents.

Also, as with the input capacitor, there is high-frequency AC current flowing in  $C_{\rm O}$  as shown in the center waveform of Figure 8. The selected capacitor must be specified to tolerate this maximum RMS current,  $I_{\rm CO(RMS)}$ . From the simplified schematic:

$$I_{LS} = I_O + I_{CO}$$

Therefore:

$$I_{CO(RMS)} = \sqrt{I^2_{LS(RMS)} - I^2_{O(RMS)}}$$

where:

$$I_{O(RMS)} = I_{O}$$

and from Step 6:

$$I_{LS(RMS)} = \frac{2 \times I_O}{(1-d)} \times \sqrt{\frac{(1-d)}{3}}$$

SO:

$$I_{CO(RMS)} = \sqrt{\frac{1-d}{3} \times \left(\frac{2 \times I_0}{1-d}\right)^2 - I_0^2}$$

The maximum RMS current in the output capacitor occurs at  $d_{MAX}$ ,  $\Delta I_{LS(MAX)}$ ,  $I_{O(MAX)}$ ,  $V_{IN(MIN)}$ , so:

If we allow for a capacitor tolerance of ±10% and a further reduction of capacitance of 50% due to the DC bias effect (operating a 6.3V ceramic capacitor at 5V), our final nominal value is:

$$C_{O} = \frac{110\mu F}{90\% \times 50\%} \approx 500\mu$$

We can achieve this by placing five 100µF ceramic capacitors (Murata GRM32EE70J107ME15) in parallel. The AC current in each capacitor is:

$$\frac{I_{CO(RMS)}}{5} \approx 0.84ARMS$$

which is well within specification for the selected capacitor.

#### **Step 15: Summarize the Power Component Design**

We have now made a first pass at calculating all the power components in the no-opto flyback converter using the MAX17690. Referring to the schematic we have:

| POWER COMPONENT                 | QTY | DESCRIPTION                                                                                                                                                                                                      |  |

|---------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| T1                              | 1   | FLYBACK TRANSFORMER PRI. INDUCTANCE = 12µH SEC-PRI TURNS RATIO = 0.25 PEAK PRI. CURRENT = 4.8A PEAK SEC. CURRENT = 14.3A MAX. PRI. RMS CURRENT = 2.23A MAX. SEC. RMS CURRENT = 4.9A SWITCHING FREQUENCY = 128kHz |  |

| C2, C3,<br>C18-C21              | 6   | INPUT CAPACITORS CAPACITOR; SMT (1210); CERAM- IC CHIP; 4.7µF; 80V; 10%; X7R MURATA GRM32ER71K475KE14                                                                                                            |  |

| C10, C11,<br>C22, C22A,<br>C22B | 5   | OUTPUT CAPACITORS CAPACITOR; SMT (1210); CERAM- IC CHIP; 100µF; 6.3V; 20%; X7U MURATA GRM32EE70J107ME15                                                                                                          |  |

| R12                             | 1   | CURRENT-SENSE RESISTOR<br>RESISTOR; 0805; 0.02 OHM; 1%;<br>75PPM; 0.25W; THICK FILM<br>VISHAY DALE WSL0805R-<br>0200FEA18                                                                                        |  |

| Q1                              | 1   | PRIMARY-SIDE MOSFET TRAN; N-CHANNEL 150V (D-S) MOSFET; NCH; SO-8; PD-(104W); I-(53.7A); V-(150V) VISHAY SILICONIX SIR- 872ADP-T1-GE3                                                                             |  |

| Q2                              | 1   | SECONDARY-SIDE SYNCHRO-<br>NOUS MOSFET<br>TRAN; N-CHANNEL 40 V (D-S)<br>MOSFET; NCH; SO-8; PD-(15.6W)<br>I-(21A); V-(40V)<br>VISHAY SILICONIX SIR836DP-T1-<br>GE3                                                |  |

## Part II: Setting Up the MAX17690 No-Opto Flyback Controller

#### Step 16: Setting Up the Switching Frequency

The MAX17690 can operate at switching frequencies between 50kHz and 250kHz (subject to the considerations in Step 3). A lower switching frequency optimizes the design for efficiency, whereas increasing the switching frequency allows for smaller inductive and capacitive components sizes and costs. A switching frequency of 128kHz was chosen in Step 3. R9 sets the switching frequency according to the following expression:

www.maximintegrated.com Maxim Integrated | 14

$$R9 = \frac{5 \times 10^6}{f_{SW}} \approx 51 k\Omega$$

where R9 is in  $k\Omega$  and  $f_{SW}$  is in Hz.

#### Step 17: Setting Up the Soft-Start Time

The capacitor C6 connected between the SS pin and SGND programs the soft-start time. A precision internal 5µA current source charges the soft-start capacitor C6. During the soft-start time, the voltage at the SS pin is used as a reference for the internal error amplifier during startup. The soft-start feature reduces inrush current during startup. Since the reference voltage for the internal error amplifier is ramping up linearly, so too is the output voltage during soft-start. The soft-start capacitor is chosen based on the required soft-start time (10ms) as follows:

$$C6 = 5 \times t_{SS} \approx 50 \text{nF}$$

where C6 is in nF and  $t_{\text{SS}}$  is in ms. A standard 47nF capacitor was chosen.

#### Step 18: Setting Up the UVLO and OVI Resistors

A resistor-divider network of R1, R3, and R2 from V<sub>IN</sub> to SGND sets the input undervoltage lockout threshold and the output overvoltage inhibit threshold. The MAX17690 does not commence its startup operation until the voltage on the EN/UVLO pin (R3/R2 node) exceeds 1.215V (typical). When the voltage on the OVI pin (R1/R3 node) exceeds 1.215V (typical), the MAX17690 stops switching, thus inhibiting the output. Both pins have hysteresis built in to avoid unstable turn-on/turn-off at the UVLO/EN and OVI thresholds. After the device is enabled, if the voltage on the UVLO/EN pin drops below 1.1V (typical), the controller turns off; after the device is OVI inhibited, it turns back on when the voltage at the OVI pin drops below 1.1V (typical). Whenever the controller turns on, it goes through the soft-start sequence. For the current design R1 =  $10k\Omega$ , R2 =  $365k\Omega$ , and R3 =  $40.2k\Omega$  give rise to an UVLO/EN threshold of 9V and an OVI threshold of 51V.

### Step 19: Placing Decoupling Capacitors on $V_{\mbox{\scriptsize IN}}$ and $\mbox{\scriptsize INTVCC}$

As previously discussed, the MAX17690 no-opto flyback controller compares the voltage  $V_{\text{FLYBACK}}$  to  $V_{\text{IN}}$ . This voltage difference is converted to a proportional current that flows in R5. The voltage across R5 is sampled and compared to an internal reference by the error amplifier. The output of the error amplifier is used to regulate the output voltage. The  $V_{\text{IN}}$  pin should be directly connected to the input voltage supply. For robust and accurate operation, a ceramic capacitor (C14 = 1µF) should be placed between  $V_{\text{IN}}$  and SGND as close as possible to the IC.

$V_{\text{IN}}$  powers internal low dropout regulator of the MAX17690. The regulated output of the LDO is connected to the INTVCC pin. A ceramic capacitor (C4 = 2.2 $\mu$ F min) should be connected between the INTVCC and PGND pins for

the stable operation over the full temperature range. Place this capacitor as close as possible to the IC.

#### Step 20: Setting Up the Feedback Components

$R_{\text{SET}}$ ,  $R_{\text{FB}}$ ,  $R_{\text{RIN}}$ ,  $R_{\text{VCM}}$ , and  $R_{\text{TC}}$  are all critically important to achieving optimum output voltage regulation across all specified line, load and temperature ranges.

**R**<sub>SET</sub> **resistor:** This resistor value is optimized based on the IC's internal voltage to current amplifier and should not be changed.

$$R5 = R_{SET} = 10k\Omega$$

**R**<sub>FB</sub> **resistor:** The feedback resistor is calculated according to the following equation:

$$\begin{split} R_{FB} = & \frac{R_{SET}}{n_{SP} \times V_{SET}} \times \\ \left\{ V_O + V_{DFR} + V_{TC} \times & \frac{\delta V_{DFR}}{\delta T} \times \frac{\delta T}{\delta V_{TC}} \right\} \end{split}$$

Since we are using a synchronous MOSFET for rectification on the secondary side, we can assume that  $\delta V_{DFR}/\delta T=0$ , so:

$$R_{FB} = \frac{R_{SET}}{n_{SP} \times V_{SET}} \times \{V_O + V_{DFR}\} \approx 204 k\Omega$$

From the MAX17690 data sheet,  $V_{SET}=1V$ . The two resistors R4 =  $200k\Omega$  and R15 =  $3.92k\Omega$  form R<sub>FB</sub>. Using one high value resistor and one low value resistor in series allows slight adjustment to the series resistance combination so that the output voltage can be fine-tuned to its required value, if necessary.

$R_{RIN}$  resistor: The internal temperature compensation circuitry requires a current proportional to  $V_{IN}$ .  $R_{RIN}$  is calculated according to the following equation:

$$R_{RIN} \approx 0.6 \times R_{FB}$$

$R_{VCM}$  resistor: The MAX17690 generates an internal voltage proportional to the on-time volt-second product. This enables the device to determine the correct sampling instant for  $V_{FLYBACK}$  during the  $Q_P$  off-time. Resistor R6 is used to scale this internal voltage to an acceptable internal voltage limit in the device. To calculate the resistor, we must first calculate a scaling constant as follows:

$$K_C = \frac{(1 - d_{MAX}) \times 10^8}{3 \times f_{SW}} = 120$$

where  $d_{MAX}$  = 0.65 and  $f_{SW}$  = 128,000. After  $K_C$  is calculated, the R6 value can be selected from the table below by choosing the resistance value that corresponds to the next largest  $K_C$ .

www.maximintegrated.com Maxim Integrated | 15

| K <sub>C</sub> | R6    |

|----------------|-------|

| 640            | 0Ω    |

| 320            | 75kΩ  |

| 160            | 121kΩ |

| 80             | 220Ω  |

| 40             | Open  |

In the present case, R6 =  $121k\Omega$ .

$\boldsymbol{R}_{\text{TC}}$  resistor: The value of  $\boldsymbol{R}_{\text{TC}}$  can then be calculated using the previous expression, restated below:

$$R_{TC} = -R_{FB} \times n_{SP} \times \frac{\delta T}{\delta V_{DFR}} \times \frac{\delta V_{TC}}{\delta T}$$

Since we are using a synchronous MOSFET for secondary-side rectification, we can assume that the temperature coefficient  $\delta V_{DFR}\!/\!\delta T$  is zero so  $R_{TC}$  should be infinite (i.e., open circuit).

This completes the setup of the MAX17690 no-opto flyback controller.

#### Part III: Closing the Control Loop

#### Step 21: Determine the Required Bandwidth

The bandwidth of the control loop determines how quickly the converter can respond to changes at its input and output. If we have a step change in output current the voltage across the output capacitor decreases as shown in Figure 9.

The control loop detects this reduction in output voltage and increases the duty cycle of Q<sub>P</sub> to supply more current to the output capacitor. The amount of time required by the control loop to increase the duty cycle from its min-

Figure 9. Output load step response.

imum value to its maximum value is the response time,  $\tau_{RES}$ , of the control loop. For the MAX17690 we have:

$$\tau_{RES} \approx \left\{ \frac{1}{3 \times f_C} + \frac{1}{f_{SW}} \right\}$$

where f<sub>C</sub> is the bandwidth of the power converter. If we apply a switching load step of amplitude  $\Delta I_{\text{STEP}},$  at a frequency of  $(1/\tau_{RES})$  and a 50% duty cycle then, to limit the output voltage deviation to  $\pm \Delta V_{O(STEP)}$  we must have a minimum output capacitance of:

$$C_{O(MIN)} = \frac{\Delta I_{STEP} \times \left(\frac{\tau_{RES}}{2}\right)}{\Delta V_{O(STEP)}}$$

Combining the two previous equations, we have:

$$f_{C} = \frac{\frac{1}{3} \times f_{SW} \times \Delta I_{O(STEP)}}{2 \times f_{SW} \times C_{O(MIN)} \times \Delta V_{O(STEP)} - \Delta I_{O(STEP)}}$$

It is normal to specify  $\Delta V_{O(STEP)}$  for a load step from 50% to 100% of the maximum output current. We have already calculated  $C_{O(MIN)}$  = 220 $\mu F$  in Step 14,  $f_{SW}$  = 128,000Hz, so based on a 3% maximum  $\Delta V_{O(STEP)}$ :

$$f_C \approx 4.3Hz$$

#### **Step 22: Calculate the Loop Compensation**

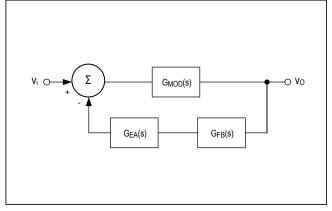

The MAX17690 uses peak current-mode control and an internal transconductance error amplifier to compensate the control loop. The control loop is modelled, as shown in Figure 10, by a power modulator transfer function  $G_{MOD(s)}$ an output-voltage feedback transfer function GFB(s) and an error amplifier transfer function G<sub>EA(s)</sub>.

The power modulator has a pole located at f<sub>p(MOD)</sub> determined by the impedance of the output capacitor Co and the load impedance  $R_L$ . It also has a zero at  $f_{z(MOD)}$ determined by the impedance of Co and the ESR of Co. The DC gain of the power modulator is determined by the

Figure 10. Model of control loop.

peak primary current  $\Delta I_{LP}$  and the current-sense resistor  $R_{CS}.$  So:

$$G_{MOD(dc)} = \frac{1}{\Delta I_{LP} \times R_{CS}}$$

$$f_{p(MOD)} = \frac{1}{2\pi \times C_O \times R_L} = \frac{I_{O(MAX)}}{2\pi \times C_O \times V_O}$$

and:

and:

$$f_{z(MOD)} = \frac{1}{2\pi \times C_O \times ESR_{CO}}$$

The output voltage feedback transfer function  $G_{FB(S)}$  is independent of frequency and has a DC gain determined by  $V_{IN}$ ,  $V_{FLYBACK}$ , and  $V_{set}$  as follows:

$$G_{FB(DC)} = \frac{V_{SET}}{V_{Flyback} - V_{IN}} = \frac{V_{SET} \times n_{SP}}{V_{O} + V_{DFR}}$$

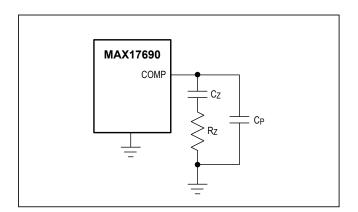

The transconductance error amplifier of the MAX17690 should be set up in a configuration to compensate for the pole at  $f_{p(MOD)}$  and the zero at  $f_{z(MOD)}$  of the modulator. This can be achieved by type II transconductance error amplifier compensation shown in Figure 11.

This type of compensation scheme has a low frequency pole at  $f_{\text{p-lf}(\text{EA})}$  due to the very large output resistance  $R_O$  (30m $\Omega$  - 50M $\Omega$ ) of the operational transconductance amplifier (OTA). It has a zero at  $f_{z(\text{EA})}$  determined by  $C_Z$  and  $R_Z$  of the compensation network, and it has an additional pole at  $f_{p(\text{EA})}$  determined by  $C_P$  and  $R_Z$  of the compensation network. So:

$$f_{P-If(EA)} = \frac{1}{2\pi \times C_z \times (R_O + R_Z)}$$

$$f_{z(EA)} = \frac{1}{2\pi \times C_z \times R_Z}$$

$$f_{p(EA)} = \frac{1}{2\pi \times C_P \times R_Z}$$

Figure 11. Type II compensation for OTA.

To achieve stable operation, we must ensure that:

$$f_{p(MOD)} \ll f_C < f_{SW} / 20$$

Set the closed loop gain at f<sub>C</sub> equal to 1:

$$G_{MOD(fc)} \times G_{FB(fc)} \times G_{EA(fc)} = 1$$

Place the zero in the error amplifier network at the same frequency as the pole in the power modulator transfer function:

$$f_{Z(EA)} = f_{p(MOD)}$$

$$\frac{1}{2\pi \times C_Z \times R_Z} = \frac{I_{O(MAX)}}{2\pi \times C_O \times V_O}$$

Place the pole in the error amplifier network at the same frequency as the zero in the power modulator transfer function:

$$f_{p(EA)} = f_{z(MOD)}$$

$$\frac{1}{2\pi \times C_P \times R_z} = \frac{1}{2\pi \times C_O \times ESR_{CO}}$$

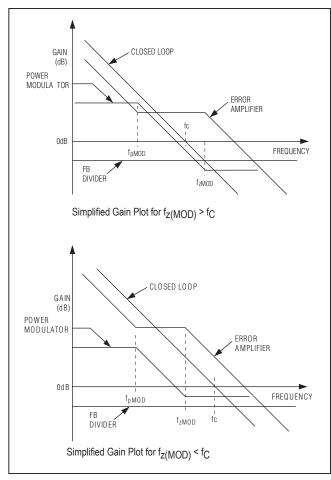

The frequency  $f_{z(\text{MOD})}$  at which the zero occurs in the power modulator transfer function depends on the ESR of  $C_O$ . If ceramic capacitors are used for  $C_O$ ,  $f_{Z(\text{MOD})}$  will generally be much higher than  $f_C$ . However, if the ESR of  $C_O$  is large,  $f_{Z(\text{MOD})}$  could be lower than  $f_C$ . This is a very important point since both the gain of the power modulator at  $f_C$ , and the gain of the error amplifier at  $f_C$  depend on whether  $f_{Z(\text{MOD})}$  is greater than or less than  $f_C$ . This is illustrated in Figure 12.

By examining the gain plots in Figure 12, we see that:

For  $f_{Z(MOD)} > f_C$ :

$$G_{MOD(fc)} = G_{MOD(DC)} \times \left(\frac{f_{p(MOD)}}{f_{C}}\right)$$

$$G_{EA(fc)} = g_{m(EA)} \times R_Z$$

and for  $f_{Z(MOD)} < f_C$ :

$$G_{MOD(fc)} = G_{MOD(DC)} \times \left( \frac{f_{p(MOD)}}{f_{z(MOD)}} \right)$$

$$G_{EA(fc)} = g_{m(EA)} \times R_Z \times \left(\frac{f_{Z(MOD)}}{f_C}\right)$$

Figure 12. Simplified gain plot.

For the current design, we have:

$$f_{p(MOD)} = \frac{I_{O}}{2 \times \pi \times V_{O} \times C_{O}} \approx 370 \text{Hz}$$

and:

$$f_{Z(MOD)} = \frac{1}{2 \times \pi \times esr_{CO} \times C_O} \approx 2.7MHz$$

where  $C_O$  = 220 $\mu$ F as calculated in Step 14 and esr $_{CO}$  = 200 $\mu\Omega$  for five MURATA GRM32EE70J107ME15 capacitors in parallel.

Since  $f_{Z(MOD)} > f_C$ :

$$G_{MOD(fc)} = G_{MOD(DC)} \times \left(\frac{f_{P(MOD)}}{f_{C}}\right) = \frac{1}{\Delta I_{LP} \times R_{CS}} \times \left(\frac{f_{P(MOD)}}{f_{C}}\right)$$

$$G_{EA(fc)} = g_{m(EA)} \times R_Z$$

and since G<sub>FB</sub> is independent of frequency, we have:

$$G_{FB(fc)} = G_{FB(DC)} = \frac{V_{SET} \times n_{SP}}{V_O + V_{DFR}}$$

We can now set the closed-loop gain equal to 1 as follows:

$$G_{MOD(fc)} \times G_{FB(DC)} \times G_{EA(FC)} = 1$$

$$\frac{1}{\Delta I_{LP} \times R_{CS}} \times \left(\frac{f_{P(MOD)}}{f_{C}}\right) \times \frac{V_{SET} \times n_{SP}}{V_{O} + V_{DFR}} \times g_{m(EA)} \times R_{Z} = 1$$

Rearranging we can calculate:

$$R_{Z} = \frac{1}{g_{m(EA)}} \times \frac{(V_{O} + V_{DFR})}{V_{SET} \times n_{SP}} \times \left(\frac{f_{C}}{f_{p(MOD)}}\right) \times R_{CS} \times \Delta I_{LP}$$

Substituting  $\Delta I_{LP}$  from Step 12:

$$R_Z = \frac{1}{g_{m(EA)}} \times \frac{(V_O + V_{DFR})}{V_{SET} \times n_{SP}} \times \left(\frac{f_C}{f_{p(MOD)}}\right) \times R_{CS} \times \sqrt{\frac{2 \times V_O \times I_{O(MAX)}}{\eta \times L_P \times f_{SW}}}$$

$$R_z = 12k\Omega$$

Finally, we can calculate the remaining components,  $C_Z$  and  $C_P$ , in the error amplifier compensation network as follows:

$$C_Z = \frac{1}{2\pi \times f_{p(MOD)} \times R_Z} = 47nF$$

and:

$$C_P = \frac{1}{2\pi \times f_{Z(MOD)} \times R_Z} = 5pF$$

#### **Design Resources**

Download the complete set of **Design Resources** including the schematics, bill of materials, PCB layout, and test files.

#### **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 10/17    | Initial release | _       |

Maxim Integrated www.maximintegrated.com

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.