TNJ-069 : CMOS デジタル信号はなぜ正しく伝送できているのか 当たり前と思われる信号伝送も理論と比べてみると疑問が生じる

はじめに

アナログ・デバイセズ株式会社では、ほぼ毎年新卒採用をおこなっており、この記事を執筆している2019年も新入社員が入社しました。その今年は私の部署が新人受け入れを担当し、半年間の新人教育を行いました(「た」で過去形であり、本ノート脱稿時点では、すでに配属部署に巣立っていきました)。

その新人がある日、「同軸ケーブルにステップ信号を加えると…」という伝送線路(伝送線路とは同軸ケーブルや、高速信号伝送でのプリント基板のパターンなど、その媒体を信号が「波動」として伝わる(伝搬する)状態を考えるべき伝送媒体。もっと簡単にいえば「配線」です)ネタの質問をしてきました。

その質問は「おお!これはあまりにも高度だ!」とはじめは思いました。そこでそのネタをこの「回路設計WEBラボ」で紹介しようと思いましたが、実はそこには別の条件があったことが判明し、難なくクローズ(汗)。

そこで折角でもあり、かつ最近重要な伝送線路ネタを何か書こうと思い、「そうだ、昔からの自分自身の疑問があったな」と、タイトルに示したような話題をまとめてみることにしました。

〔本題に早く到達したい方は読み飛ばしてください〕自らの回路設計経験とCMOSデジタル伝送

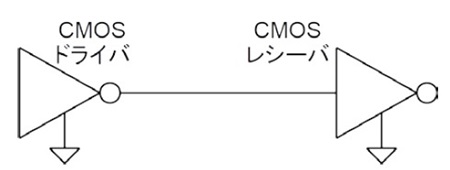

図1のようなCMOS信号伝送回路は当たり前のように設計しているものです。5Vを送り5Vで受け(3.3Vや1.8Vもありますね)、デジタル信号を伝送します。

私も駆け出しのころ、フォトダイオード・アンプ(OPアンプ回路)の設計とあわせて、デジタル・システムのプリント基板設計も行っていました。最初はZ80マイコン基板の改版から始まり、途中からはFPGAを用いたシステムなども含めて、結構な数のアートワーク設計を行っていました(最初は「手張りアートワーク」だなんて、現代の若い読者の方には考えられない基板設計も経験しました)。ここではCMOS信号伝送が主だったわけですが、当たり前のように「5Vを送り5Vで受ける回路」として設計していました。

そしてそのころは両面基板での設計でした。別の部署では片面の紙フェノール基板などを使っており、「両面なんてコスト高くて使えないよ」とその部署の人にも言われたものです。

両面基板から4層基板に代わっていく時代にふと思った「特性インピーダンス」

私は産業用機器の設計だったので両面基板が使えたのですが、ときとともに高密度化の要求から4層基板、6層基板と多層に代わっていきました。こうすると内層の2層目(L2)をグラウンドとして、表面層(L1)に信号パターンを形成することになります。

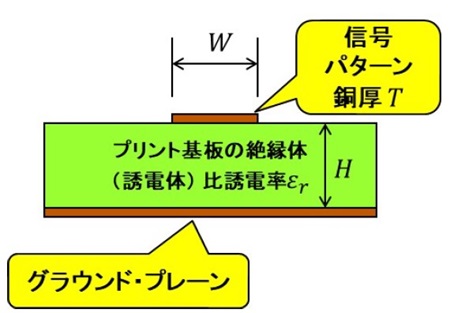

そしてその前後(もしくはもっと前だったかも)に図2のような高周波・高速信号伝送用に用いられる「マイクロストリップ・ライン」を知りました。マイクロストリップ・ラインは誘電体をはさんで下側にグラウンド面を用意し、その上に信号パターンを形成して、「特性インピーダンス」を定義して信号伝送する伝送線路です。

そのときに思うわけです。「これまで設計してきた4層基板はL2がグラウンドで、その表面にデジタル信号のパターンが形成されている。これはまるでマイクロストリップ・ラインと同じではないか」、「オレの設計してきた4層基板のパターンでは、特性インピーダンスはどれほどなのか?」。

それでも(当時は簡単に計算できるWebツールもなく)忙しさにかまけて、その疑問はずっと放置したままでした。だって「作った CMOSデジタル回路は、5Vを送れば、ちゃんと5Vが受けられるじゃん。あたりまえじゃん」だったからです。

さらに以降に多重反射という概念を知る

早い(若い)ころから以下に示す伝送線路と、以降に示す「反射係数」の概念は知っていたものの、だいぶ日が経たとある日、「多重反射」という概念を知りました。よく考えてみれば反射係数がしっかり分かっていれば、多重反射もその延長で分かるはずだと気づき、自らの修行不足を恥じたものでした。

![図3.大学のときの電気回路Ⅱの教科書[1]](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_03.jpg?la=en&w=450&rev=072e466a253c4fb79b29e5b95ffdd147)

大学のとき「電気回路Ⅱ」という授業がありました。これが過渡現象を扱うもので、とても高度でした。たぶん中盤以降はほとんどついていけなかったと思います。教科書はまだとってありましたので、折角なので図3に示します[1]。

あるときこの教科書をパラパラとめくってみました。なんと「伝送線路と多重反射」についての説明があるではありませんか!自分の学んでいた教科書に多重反射が示されていたのです…。教科書の後半だったのでたぶん授業では解説していなかったと思いますが、それでも40歳すぎてそれ(教科書自体とその記述)を見つけたときには苦笑いしてしまいました。

そしてその時にあらためて驚いたこととして、この書籍の初版が1965年(私が2歳!)で、私が使ったのが1983年前後だったということです。かなり古く、かつ長く活用された教科書だったということです(現在は絶版のようです)。

多重反射とこれまで設計してきたCMOS信号伝送との関係はどうなる

多重反射は以降に示すように、伝送線路の特性インピーダンスと信号源抵抗/終端抵抗の大きさが異なると、それぞれの抵抗のところで信号が反射し、反射波が線路内を行き来しながら反射を繰り返すというものです。

CMOS信号伝送はご存知のように、低いCMOSドライバ出力インピーダンスで送出し、非常に高いCMOSレシーバ入力抵抗値で受信する方式です。このCMOS回路を4層プリント基板上に形成すれば、途中には「たんに繋げただけのパターン」が存在します。このパターンが(どうやら)何らかの特性インピーダンスをもつ伝送線路になり、「出力と入力の間で多重反射が形成されるのではないか」という疑問が生じるわけでした。

しかし「ふつうに作ったCMOSデジタル回路は、5Vを送れば、ちゃんと5Vが受けられるじゃん。あたりまえじゃん」でした。この違いはなんなのでしょうか。

これを今回、ステップ・バイ・ステップで考えてみましょう。実は以降の説明(とくに結果)は、技術ノートTNJ-039[2]でも「さらり」と説明されていたのでした。

(イントロダクションはここまで)

考察その1:4層基板で形成される特性インピーダンスはいかほどか

その前に…特性インピーダンスとはなにものか

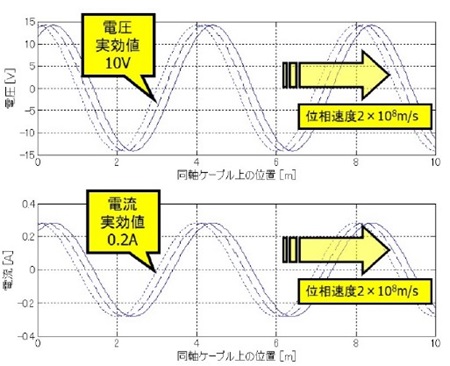

図4のように伝送線路の中を電圧𝑉と電流𝐼は波動として伝搬していきます(特性インピーダンス50Ωをもつ同軸ケーブルの例)。特性インピーダンス𝑍0はこの電圧𝑉と電流𝐼の比率で

として決まるものです。「伝送線路内に抵抗素子(成分)」があるというものではありません。

![図5.4層プリント基板の層構成の例。L1~L2間が0.2mmになっている(ピーバンドットコム「リジッド多層板層構成参考表」[3]から転載)](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_05.jpg?la=en&w=450&rev=f3cdc4d30d154062ba458b4c9897fd05)

![図7.Web上にある特性インピーダンス計算ツールの例[4]](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_07.jpg?la=en&w=450&rev=6ab7dde58cb14fc698d94a585897a667)

また図2のマイクロストリップ・ラインでは、図中に示したそれぞれのパラメータから特性インピーダンスが決まります。以降でそのパラメータからweb上のツールを使って計算してみた例を示します。

4層プリント基板の層構成(厚さ)を確認してみる

4層基板の層構成の一例として図5にピーバンドットコムの「リジッド多層板層構成参考表[3]」から転載したものを示します。

基板厚がt=1.6mmでも表面L1と内層L2、内層L3と裏面L4の間はなんと0.2mmになっています。L1-L2、L3-L4間は、L2-L3間と比べても「薄い」ことになります。

このL1-L2、L3-L4間は、「プリプレグ」と呼ばれる柔らかいシート状の絶縁物から構成されています。図6にプリプレグの例を示します(ピーバンドットコムご提供)。これを1枚から2枚重ねて、0.1mmから0.2mm程度の絶縁厚みを作ります。ともあれかなり薄い絶縁厚さということが分かります。

内層L2をグラウンド層(グラウンド・プレーン)として、表面層L1にCMOS信号伝送パターンを引くと、そこはここまで説明してきた、マイクロストリップ・ラインの構造になるわけです。

なーんにも考えずに設計していた4層基板のパターンは意外な特性インピーダンスになっていた!

図7に示すWeb上にある特性インピーダンス計算ツールのひとつ[4]を使って、「なーんにも考えずにL2をグラウンド層にして、そのうえにCMOS信号伝送パターンを引いた」構造物(実際はマイクロストリップ・ライン)の特性インピーダンスを計算してみます。

なんとパターン幅0.2mm=63.81Ω、パターン幅0.3mm=51.78Ωとなっています(層間厚は図5に従い0.2mm、比誘電率𝜖𝑟= 4.6、 パターン厚は銅張18μmに対して銅めっき20μmで38μmとして計算)。もし層間厚が0.15mmなら、パターン幅0.2mm= 53.62Ωです!特性インピーダンス50Ωの同軸ケーブルとほとんど同じです!

最近のデジタル信号のパターン幅は0.1mmから0.3mm程度でしょうから、「なーんにも考えずに引いたCMOS伝送パターン」は、なんと「ほぼ50Ωの特性インピーダンス(同軸ケーブルとほとんど同じ!)が形成されていた」ことになるわけです。

考察その2:4層プリント基板のパターンで生じる信号反射(信号源抵抗50Ωのケース)

信号反射のその前に…反射係数とはなにものか

特性インピーダンス𝑍0をもつ伝送線路の中を伝搬する電圧𝑉もしくは電流𝐼は、その伝送線路の負荷端(受端)の負荷抵抗𝑅𝐿が𝑍0≠𝑅𝐿であれば、この負荷端で電圧・電流が反射します。この反射する率が「反射係数」と呼ばれるもので

として決まります。電圧/電流はこの比率で信号源側に戻ってきます。

伝送線路の受端で反射するようすをLTspiceでシミュレーションしてみる(信号源抵抗は50Ω)

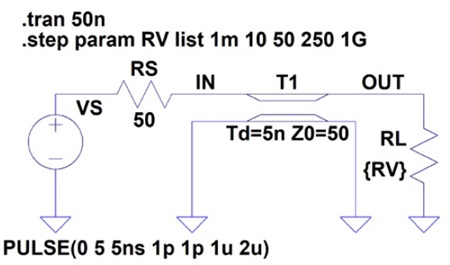

この反射のようすを、LTspiceを用いてシミュレーションしてみましょう。図8は50Ω伝送線路(ここまでの説明からすれば、なーんにも考えずにCMOS信号伝送として引いたパターンにも相当すると言えます)の受端に設置した負荷抵抗の大きさを変えて、信号の反射するようすをシミュレーションする回路です。

信号源抵抗𝑅𝑆は伝送線路の特性インピーダンスと等しい50Ωに設定し、伝送線路を伝搬する時間を5nsとしています(同軸ケーブルなら1mに相当)。信号源はt=5ns時に立ち上がります。

シミュレーションでは負荷抵抗値𝑅𝐿を1mΩ、25Ω、50Ω、250Ω、1GΩと変えています。

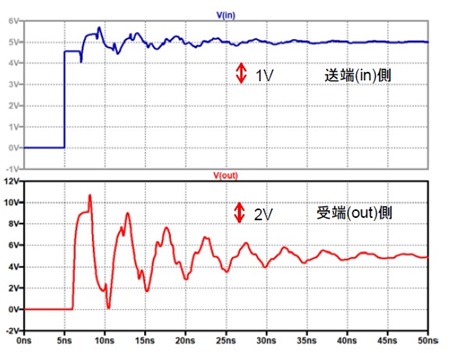

図9はその結果です。図9の上側が信号源側(送端)、下側が負荷抵抗側(受端)です。

![図9.図8で伝送線路受端の負荷抵抗を変えて信号の反射するようすをシミュレーションしてみた[上側が信号源側(送端)、下側が負荷抵抗側(受端)。𝑅𝐿=1GΩ≅∞がCMOSレシーバ入力に相当する]](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_09.jpg?la=en&w=450&rev=f4bece5cc7e64ef4b05910b6d4d3724d)

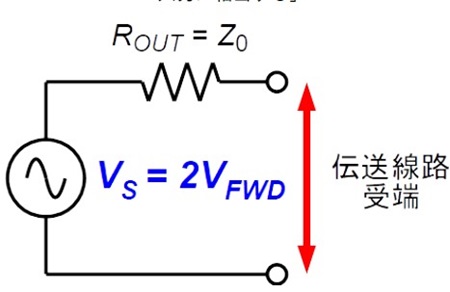

信号源側から受端側に伝搬する電圧の考え方は

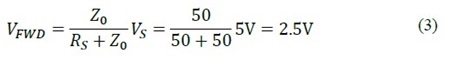

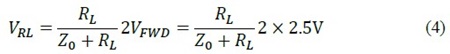

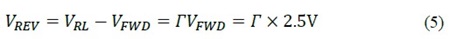

この図9の上側の信号源側(送端)において、立ち上がりt=5nsで最初に決まる電圧は2.5Vになっています。これが伝送線路の中を負荷抵抗(受端)側に伝搬する電圧𝑉FWDになります(Voltage-Forward)。この電圧が決まる関係式は、信号源抵抗𝑅𝑆(送端)は𝑍0と等しく𝑅𝑆=𝑍0=50Ωなので

伝送線路の受端で反射するようすと反射係数

図9の下側が負荷抵抗側(受端)の波形です。信号源抵抗𝑅𝑆=50Ωの条件で、伝送線路の中を受端側に伝搬してきた電圧𝑉FWD= 2.5Vが、受端において信号源側(送端)の変化から5ns後に、負荷抵抗の大きさごとで異なる電圧𝑉RLとして

が生じます。図9の下側の波形からも、負荷抵抗の大きさごとで異なる電圧が生じていることが分かります。上記の式(4)で「2×」となっている理由は、図10のとおり、伝送線路の負荷抵抗(受端)から伝送線路側を見た等価回路は、この図のように、𝑉𝑆=2𝑉FWD = 5Vの電圧源と50Ωの出力抵抗𝑅OUT(=信号源抵抗𝑅𝑆=伝送線路の特性インピーダンス𝑍0)でモデル化されるからです。式(3)のように5Vが送端側で1/2に、2.5Vになっているからだともいえます。

受端の電圧𝑉RLのうち、𝑉FWD=2.5Vとの差分が信号源側(送端)に反射する大きさになります。この反射波𝑉REV(Voltage- Reverse)の大きさは

になります。𝛤は式(2)に示す電圧/電流が反射する率、「反射係数」です。この式により𝑉REVが信号源側(送端)に反射波として戻ってきます。そして最終的に信号源側(送端)に、信号源側(送端)の変化から10ns経過後に反射波𝑉REV=𝛤𝑉FWDが現れ、送端と受端が最終値で決まることになります。このときの信号源側(送端)の電圧最終値𝑉INは

となります。このあたりのストーリーに関する話しは[2]もご参照ください。

考察その3:4層プリント基板のパターンで生じる「多重反射」(CMOS信号伝送のケース)

つづいて「なーんにも考えずに設計してきた」CMOS信号伝送の条件、つまり信号源(送端)抵抗であるCMOSドライバ出力インピーダンスが非常に低く(𝑅𝑆≈0。以降では5Ωを例とします)、負荷(受端)抵抗であるCMOSレシーバ入力インピーダンスがほぼ無限大(𝑅𝐿≈∞、以降では図11の定数)の条件で、多重反射の発生するようすを示していきます。

LTspiceでシミュレーションしてみる回路図を図11に示します。CMOSドライバ・レシーバを模倣するため、信号源抵抗𝑅𝑆=5Ω、負荷抵抗𝑅𝐿=1MΩにし、CMOSレシーバ寄生入力容量に相当する5pFも接続しています。信号の立上り時間は非常に高速にして1ps、また伝送線路を伝搬する時間を1nsとし、同軸ケーブルであれば20cm、プリント基板上のマイクロストリップ・ラインだと15~18cm程度に相当する長さとします。実際によくありそうなCMOS信号伝送パターン長で考えてみます。

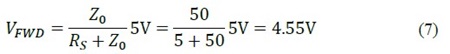

多重反射が生じており「これでは5Vを送っても、ちゃんと5Vとして受けられないぞ!」となっている

シミュレーション結果を図12に示します。上がCMOSドライバ側(送端)、下がCMOSレシーバ側(受端)です。とくに下の受端側で大きな波形の暴れが確認できます。最初のほうなどは2.5Vのスレッショルドを割る勢いです。これが「多重反射」による暴れです。

このようにCMOS信号伝送では、多重反射が発生するのです。そうすると「これではCMOSで5Vを送っても、ちゃんと5Vとして受けられないぞ!」という事態に陥ってしまうわけです。ここで一旦心を落ち着けて、まずは「多重反射」が生じているようすを考察してみましょう…。

CMOSドライバから受端側に伝搬する電圧の考え方は

CMOSドライバ出力インピーダンス(信号源抵抗)を𝑅𝑆=5Ωとしたとき、受端側に伝搬する電圧𝑉FWDは(CMOS電源電圧を5Vと仮定して)

が形成されます。これは図12のシミュレーション結果からも確認できます(上側の送端信号が立ち上がった5nsの時間)。

CMOSレシーバ入力端(受端)での反射は全反射

受端側のCMOSレシーバ入力の入力インピーダンスは(図11では1MΩと5pFと設定していますが)ほぼ無限大ですから、𝑅𝐿≈∞となり

で全反射する状態になります。これが図12の6nsの時点で発生しています(5pFの容量があるので鈍っていますが)。𝑉FWD=4.55Vで、これが全反射するため反射波は

となります。これがCMOSドライバ(送端)側にパターン上を伝搬して(戻って)きます。

受端の等価回路を考える(パターンを伝搬する電圧は大きくなり、応じて等価回路の電圧源も大きくなる)

この条件での、パターン受端から伝送線路側を見た等価回路を考えてみましょう。それにより図12の6ns時点の受端の電圧値を求めてみます。

また図10に戻ってみます。式(4)で「2𝑉FWD」となっていますが、図11での𝑅𝑆=5Ωの条件、𝑉FWD=4.55Vであっても、図10 の等価回路は2𝑉FWDで同じになります。つまり𝑉𝑆=2×4.55V=9.09Vの電圧源と50Ωの出力抵抗𝑅OUT(=パターンの特性インピーダンス𝑍0)でモデル化されるのです。

直観的には不思議ですが、𝑉FWD=4.55V(と𝐼FWD=91mA)が伝搬するのは、特性インピーダンス𝑍0をもつ媒体であり、2.5Vのケースとは「伝搬する電圧値が異なっている(大きくなっている)だけ」といえるからです。別の視点では「パターン(伝送線路)内で過渡現象が生じることで𝑉FWDが伝搬する」と考えることができ、それをモデル化すると図10において、𝑉𝑆=9.09Vとなるわけです。

これから図12の6nsの時点の電圧値𝑉RLは(受端が開放なので)

受端に𝑉FWD=4.55Vが到達したら4.55Vが全反射し、受端の電圧自体はその2倍の9.09Vになります。

CMOSドライバ出力側(送端)でも反射係数にしたがい戻ってきた反射波の再反射が生じる

CMOSドライバ側(送端)に戻ってきた反射波𝑉REVからすれば、ドライバ出力インピーダンス𝑅𝑆が「負荷抵抗𝑅𝐿」に相当します。そうすると信号源側(送端)において、反射波𝑉REVに対しては

で反射係数が決まります。図11はCMOSドライバ出力インピーダンス(信号源抵抗)を𝑅𝑆=5Ωにしています(CMOSICでは実際は5Ωから10Ω程度が存在します)。そうするとここでも反射係数𝛤𝑆はゼロにならず、CMOSドライバ側(送端)でも反射係数にしたがい反射波の再反射が生じることになります。

そしてさらにこれが負荷抵抗側(受端)に向かい、受端でまた反射が生じます。反射波が線路を行き来し、送端と受端で何度も反射を繰り返すことになります。これが「多重反射」です。

考察その4:なぜ従来のCMOS信号伝送4層プリント基板で多重反射の問題が生じなかったのか

しかしその一方で、最初に示したように「4層基板でCMOS信号を伝送したとき、なぜ多重反射の問題が生じなかったのか」という疑問が生じてくることでしょう。

図11の信号源の立上り時間は1psでした。これはCMOSドライバの本来の立上り時間からすれば非常に速いものです。

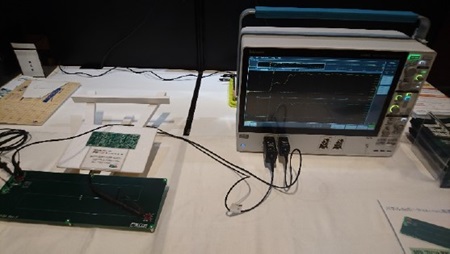

従来のCMOS伝送では立ち上がり時間が遅いから問題が生じない

信号の立ち上がり時間を、よりCMOSゲートに近いものとして5ns(VHCMOSシリーズ相当)と遅くしてみましょう。

![図13.図11のシミュレーション回路の立ち上がり時間を5ns、伝搬時間を1nsとしてみたシミュレーション結果[上側が信号源側(送端)、下側が負荷抵抗側(受端)]](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_13.jpg?la=en&w=450&rev=2a51a9d97d4246feac9dc0db11a77839)

図11の回路をこの条件に修正し、シミュレーションしてみたものを図13に示します。伝搬時間は1nsです。図12で見えていた CMOSレシーバ側(受端)での多重反射による大きな波形の暴れがなくなっています。それこそ、実際のプリント基板上のCMOSデジタル信号をオシロスコープで観測したときにみる波形にかなり近くなっています。受端での暴れも(5V伝送でも)1V以下になっています。ここから分かることは

- デジタル信号の立上り時間が、送端から受端の伝搬時間と比べて長ければ

- 逆にみると、送端から受端の信号の伝搬時間と比べて、デジタル信号の立上り時間がゆっくりならば

多重反射の問題は顕著に現れなくなる、ということです。多重反射は信号の立上り時間のうちで収まってしまうとも言えます。

Dr. Eric Bogatinの書籍でも

TNJ-040[5]の図21でもご紹介しましたが、高周波・高速プリント基板設計に関するコンサルタントの双璧として、Dr. Eric BogatinとDr. Howard Johnsonのおふたりがいます。

このうちEric Bogatinの書籍[6]の邦訳版においてp.266に「大まかな経験則として(中略)伝搬遅延が立上り時間の20%以下の場合は、リンギングは問題とならない…」と記載があります。それ以降に式(8-13)として、

が示されています。𝐿enmaxはインチで示されるパターン長、RTはnsで示される信号立ち上がり時間です。

これはRT=1nsにおいて𝐿enmax=25.4mm以下という長さです。信号伝搬を、先に図11のところで示した「プリント基板上であれば 1nsで15~18cm程度(概略)」だと仮定すれば、往復する(多重反射となる)距離30cm~36cm(300mm~360mm)の10%以下と理解することができます。

また同じような計算ですが、プリント基板上のパターン15cm~18cmは、上記の式(12)においてRT=5.9~7.1nsと計算できます。 それぞれ図13での波形と式(12)とが整合していることも分かります。

ところで「10%」という率は、いろいろな場面でも経験則として使われるものですから、式(12)は合点のいく式でもあります。この「経験則」のことを英語では「Rule of Thumb(親指の法則)」とよびますが、これも概略値で考えるということです。

実は式(12)からRule of Thumbまでのこの展開は、私が勤めさせていただいたセミナーにおいて、受講された方から質問があったものです。質問は式(12)の考え方(なりたち)についてでした。その時は式(12)自体を(書籍は保有していたわけですが)把握していませんでしたが、式の考え方について、そこでRule of Thumbを使って回答させていただいたものでした。

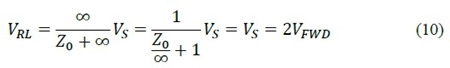

アナログ技術セミナー2019でのデモ風景

ここまで説明した多重反射と立ち上がり時間については、アナログ技術セミナー2019の展示会場において、ピーバンドットコム・ブースでそのデモを行いました。このようすを図14に示します。

ここでは図15のような900mm長の伝送線路(マイクロストリップ・ライン)を製作し、ここに高速なVHCMOSと低速な4000シリーズCMOSを用いて立ち上がり時間を変えて、レシーバ端の波形を実測しました。その例を図16と図17に示します。ここまでの説明がそのまま生じていることが分かります。

なお使用したオシロスコープはテクトロニクスのMSO64、プローブは差動プローブTAP1500というものです。今回のデモのために同社からお借りしました。この場を借りて私からも、テクトロニクス社の関係者の皆様にお礼申し上げます。

Dr. Howard Johnsonのリタイヤ後の生き方

もう一方の信号伝送コンサルタント、Dr. Howard JohnsonはSignal Consulting,Inc.という会社を経営しています。ウェブサイトは [7]で見ることができます。

現在はそのHPでは氏の会社(実際はご自宅と思われますが)の住所は掲載されていませんが、HPを初めてみたときには住所が掲載されており、何となくその住所をGoogle mapで調べてみました。

![図16.高速なVHCMOSで実験した結果[上側が信号源側(送端)、下側が負荷抵抗側(受端)]](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_16.jpg?la=en&w=450&rev=3286500bda3a45948f6aeab3dc8696be)

![図17.低速な4000シリーズCMOSで実験した結果[上側が信号源側(送端)、下側が負荷抵抗側(受端)]](/jp/_/media/analog/jp/education/web-lab/tnj069/tnj069_17.jpg?la=en&w=450&rev=6304646e46ea492bb166a4ac12808aab)

それは驚きでした。ワシントン州の海側から山脈(大きな国立公園)を挟んだ反対側の片田舎、近隣の都市からは数100km、近隣の町から10数kmくらい、また近くの小さい集落ともいえるところからも1kmほど離れた傾斜地(丘)にお住まいでした。たぶん電気も通っていないと思われます。通りというか谷あいの町々をつなぐ山岳道から分かれ、お住まいに至る小径は「Signal Hill Rd (Road)」と名付けられています。

HPによると、すでにリタイヤされているとのこと。美しい山並みを見ながらのリタイヤ生活なのだろうなと思いました。とはいえその集落には(なんと!)飛行場があるので、都市への外出となれば自家用機で(所有しているとおみうけしましたが)ひとっ飛びなのでしょう。

現在はHPには住所は掲載されていませんが、いまでもGoogle使って頑張れば「そこ」は探しだすことができます(笑)。なお探し方を知りたい方はお問合せください…。「田舎でリタイヤ」。それこそテレビで高い視聴率を得ている、朝日放送テレビ制作の『ポツンと一軒家』[8]の世界でしょうか。

著者について

デジタル回路(FPGAやASIC)からアナログ、高周波回路まで多...

この記事に関して

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}