要約

このアプリケーションノートは、結合インダクタの主な利点および従来の非結合インダクタ動作との違いについて説明します。個別インダクタによる既存の設計を結合インダクタにアップグレードする手順を示し、予想される改善を推定します。

同様の記事が2014年11月29日に「EDN」に、2014年12月1日に「EE Times Europe」に掲載されました。

はじめに

マキシム・インテグレーテッドは、最近Volterra Semiconductorを買収しました。これによって、非常に広範囲のお客様がさまざまアプリケーションで結合インダクタの利点を使用することが可能になります。結合インダクタは、しばしば多相トポロジで相間の磁気結合による電流リップル相殺を利用するために使用されます。通常、電流リップル相殺は、標準的な個別インダクタを使用する場合に多相バックコンバータの出力でのみ発生します。これらのインダクタが磁気的に結合されると、回路の全素子(MOSFET、インダクタ巻き線、PCBトレース)に電流リップル相殺が適用されます。1-6これによって、全位相からのスイッチングが個々の単一位相に影響するため、電流リップルの振幅が減少し周波数が逓倍されます。波形のRMSの減少によってパワーコンバータの効率の向上が可能になり、あるいはそれと引き替えに磁性体の小型化、過渡の高速化、およびそれに伴う出力容量の小型化が可能になります。

結合インダクタと従来のインダクタ設計

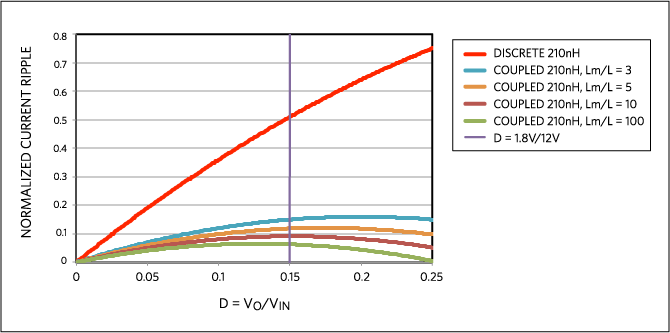

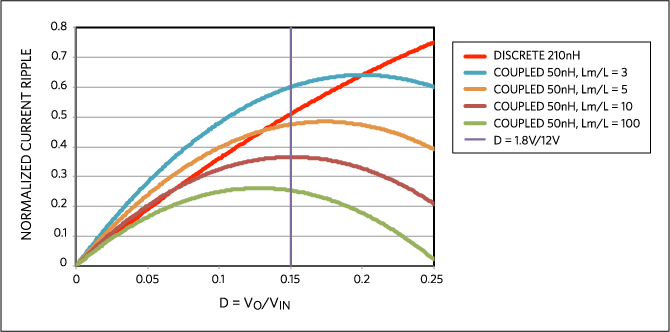

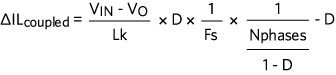

従来の非結合バックコンバータのピーク間電流リップルは、式1で表すことができます。ここで、VINは入力電圧、VOは出力電圧、Lはインダクタンス値、Dはデューティサイクル(バックコンバータの場合D = VO/VIN)、Fsはスイッチング周波数です。

結合インダクタを使用するバックコンバータの場合、電流リップルはD < 1/Nphasesで式2に変わります。ここで、ρ = Lm/Lkは結合係数(Lmは磁化または相互インダクタンス、Lkは漏れインダクタンス)、Nphasesは結合される位相の数です。6この特定の式はD < 1/Nphasesの場合に限られますが、VIN = 12Vからコア(0.5V~2.5V)など、多くのアプリケーションではこの条件でほぼ十分です。式2によって、ユーザーは回路および磁性体のパラメータが電流リップル相殺に与える影響を容易に理解することができます。

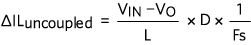

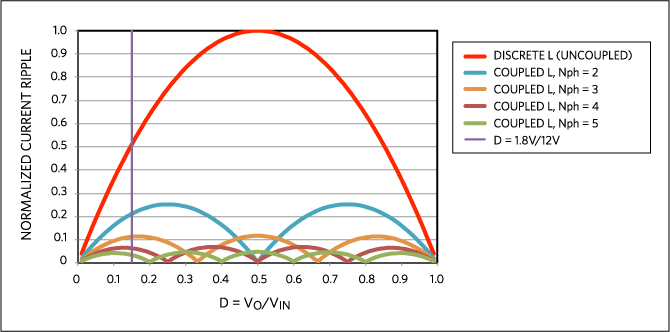

式1と比較して式2で追加されている乗数項は、アプリケーションの条件によって決まり、デューティサイクル、結合、および結合される位相の数によって変化します。図1は、4相バックコンバータでの210nHの個別インダクタおよび結合インダクタの正規化した電流リップルを示します。この電流リップルは、最大電流リップル、すなわちD = 0.5での個別インダクタのリップルによって正規化されています(したがって、個別インダクタの正規化した電流リップルはD = 0.5で1になります)。12Vから1.8Vへの標準アプリケーションは、グラフ上に示したようにD = 0.15に相当します。

図1. 4相バックコンバータの正規化した電流リップル(210nHの個別インダクタおよびさまざまな結合係数Lm/Lの210nHの結合インダクタ)

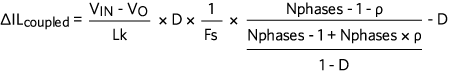

図2. 4相バックコンバータの正規化した電流リップル(210nHの個別インダクタおよびさまざまな結合係数Lm/Lの50nHの結合インダクタ)

図1は、結合インダクタによってすべての電源回路で電流リップルが大幅に相殺されることを示しています。約D = 0.15の場合よりも大幅に利点が大きいデューティサイクル値があることに注意してください。数種類の結合インダクタのプロットは結合係数Lm/Lの影響を示し、実用的なLm/L = 3~7の範囲の結合と、10や100のような理想化された非現実的な値のLm/Lを含んでいます。個別インダクタによる当初の設計が妥当で、電流リップルが許容範囲だったと想定すると、結合インダクタのインダクタンス値を低減して目標領域のD = 0.15付近でほぼ同じ電流リップルを達成するのは理にかなっています。50nH/phaseという値は、この条件で210nHの個別インダクタと同様の電流リップルを提供します(図2)。

同じピーク間電流リップルに対しては、同じ電流波形のRMSを予想することができます。これは、すべての回路分岐にわたって同様の導通損失とスイッチング損失につながり、したがって効率も同程度になります。しかし、大きい利点として、50nHのインダクタは210nHより過渡性能が4倍以上優れています。この利点によって、大型で信頼性が低く、高コストで扱いにくい出力コンデンサを通常は完全に排除することができます。高性能セラミックコンデンサ(すでに使用しているもの)のみが残ります。

高速過渡変化のあるアプリケーションでは、常にセラミックコンデンサが必要であることに注意してください。これは、低ESRおよびESLのコンデンサのみが高速負荷ステップの瞬間に必要な過渡性能を提供することができるためです。個別インダクタの場合、低速な電流スルーレートおよびそれに伴うエネルギー蓄積に対処するため、通常はバルクコンデンサが追加されます。はるかに高速な結合インダクタの場合、関連しているはるかに小さいエネルギー蓄積への対処として、通常はセラミックコンデンサの容量のみで十分です。

結合インダクタの利点は、それで終わりではありません。結合インダクタは負結合で設計されているため、全位相が電流を等しく共有するとき、すべての巻き線からの磁束が互いに相殺します。全位相の電流が等しいという条件は、多相アプリケーションでは(特に電流モード制御の場合)一般的なものです。結合インダクタでは漏れ磁束のみがエネルギーを蓄積するため、図2に示した例のエネルギー蓄積は210nH/phaseではなく50nH/phaseと関連付けられています。このことから、個別インダクタと比べて結合インダクタは基本的に小型であるか、電流飽和定格が高いか、またはその両方であると考えられます。

マイクロプロセッサへの給電に使用される12Vから1Vへのアプリケーションでの標準的な4相ソリューション用の磁性体の2つの選択肢を比較してみます。既製品の、高効率個別インダクタのFP1308R3-R21-Rと、50nH結合インダクタのCL1108-4-50TR-Rです。関連するデータシートはオンラインで入手可能です。7-8 PCB上での個別インダクタ間の距離を0.5mm (min)と想定すると、個別インダクタはマザーボード上で約722mm2を占めます。すでに大幅に優れた性能を提供することが分かっている結合インダクタは、必要な面積がわずか約396mm2です。これを図3に示します。それと同時に、個別インダクタが室温(+25℃、より高い温度では当然さらに悪化)でISAT = 80Aであるのに対し、結合インダクタは+105℃において110A/phase以上で飽和します。1.8倍以上の面積の削減と1.5倍以上の飽和の改善が同時に達成されます。

結合インダクタのサイズをより良く理解するため、この4相ソリューションに対して個別インダクタ(物理的には大幅に狭いもの)の検討も可能であることに注意してください。しかし、それらのインダクタを使用すると、飽和定格が低下するか、または目標の210nHより小さい値が必要になります。後者の場合、電流リップルの増大と効率の低下につながります。

理想的結合(つまり、非常に高いLm/Lk)を想定すると、式2で磁性体結合による電流リップルの減少を表している乗数項を簡素化することができます。その場合、式2は式3に簡約されます。3明らかに、この結合からほぼNphasesに相当する利点が期待されますが、デューティサイクルによってはさらに利点が大きくなる可能性があります。より正確には、デューティサイクルがD = 0またはD = 1の領域から離れているアプリケーションほど、さらに大きい優位性を達成することが可能です。

図3. 4相12V-1Vソリューション用の同等の効率の磁性体。4つの210nHの個別インダクタと、1つの50nHの結合インダクタ。画像提供はEaton Electronics社。

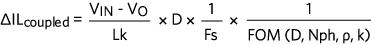

次に、結合インダクタを利用するための一般化された方法を示します。結合インダクタでの電流リップル相殺を示す式2は、式4のように一般化することができます。

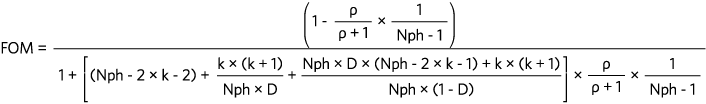

式4の性能指数(FOM)は、見慣れた、より便利なパラメータを使用することによって、参考文献[9]から式5のように導くことができます。

式5のこのFOMの式は、

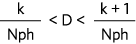

という特定の範囲のデューティサイクルDに対して有効です。ここで、インデックスkは0 < k < (Nph - 1)の範囲で変化します。

図4は、デューティサイクルの全範囲でさまざまな数の位相について電流リップルの減少を示します。理想的結合および同じ値のLを前提として電流リップルをグラフ化しています。結合される位相の数を増やすことには明らかに利点があります。

所定の出力電流に対して位相の数を故意に増やすことは、ディスクリート部品を使用する標準的ソリューションにとってコストとサイズの面で非効率的な方法であることに注意してください。この方法は、複数のスイッチング位相が1つのチップに内蔵されている市販の高集積ソリューションの場合に非常に魅力的です。これはマキシム・インテグレーテッドの電力技術および方針と完全に一致します。

>図4. 理想的結合およびさまざまな位相の数に対する多相バックコンバータの正規化した電流リップル

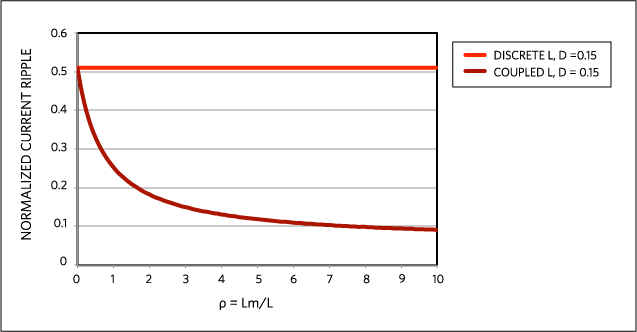

図4でも、D = 0.15という特定のデューティサイクルに目印が付けてあり、これはVIN = 12Vに対してVO = 1.8Vという実際的な例に相当します。この条件は、結合係数ρ = Lm/Lkの選択が電流リップル相殺にどのように影響するかを示す図5のグラフで使用しています。図4を見ると、個別インダクタの正規化された電流リップルはD = 0.15で約0.5となっており、これは図5でも赤い曲線で示されています。4相結合インダクタは、結合が非常に低い場合、これと同じ条件で同じ電流リップルを示し、結合の増大とともに電流リップルが大幅に低減します。図5を参照してください。電流リップルが、最初は非常に急速に減少した後、大きい値の結合係数で平坦な領域に到達していることに注意してください。この振る舞いから、大まかに3~5の範囲の結合係数が推奨されます。この方法を使うと、最大の電流リップル相殺の利点が実現しますが、収穫逓減の曲(つまり、利点がほとんどまたはまったくない過大な磁性体)を回避することができます。

図5. D = 0.15 (VO = 1.8V、VIN = 12Vのアプリケーション)での結合係数ρ = Lm/Lkの関数としての多相バックコンバータの正規化した電流リップル

簡潔なガイドライン

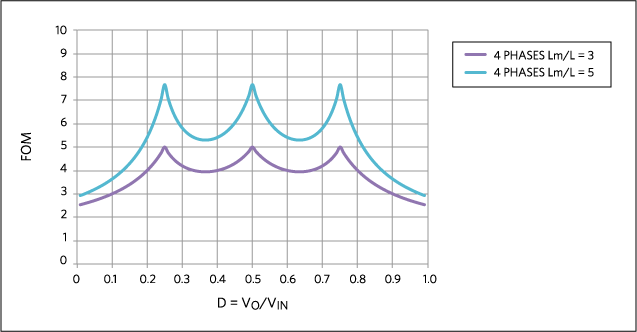

個別インダクタを使用した妥当な多相バックコンバータ設計から始めます。目標は、結合インダクタでシステム性能を向上させることです。個別インダクタによる当初の設計は妥当な電流リップルを備え、コンバータの効率はお客様の期待に適合すると想定します。実際的な結合係数の値を持つ4相バックコンバータについて、式5で予想されるFOMのグラフを図6に示します。

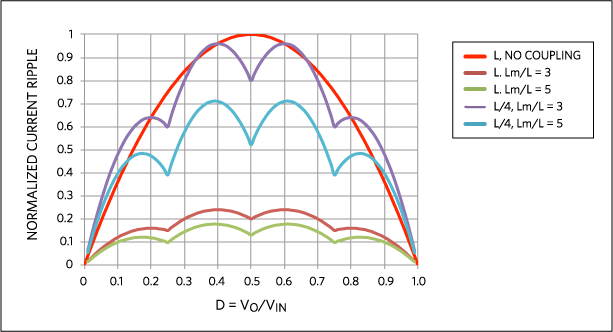

図6を参照し、Dが約0.15の付近を対象にすると、FOM = 4を設計目標と考えることができます。図7は、結果の電流リップルを示します。赤い曲線は、個別インダクタLの当初のリップルを示します。次の2つの曲線は、Lで結合が異なる場合の電流リップルを示します。最後の2つの曲線は、L/4の場合です。予想通り、Dが約0.15付近の電流リップルは、個別インダクタLと結合インダクタL/FOM = L/4で同程度になります。

図6. デューティサイクルの関数としての結合インダクタを使用した4相バックコンバータのFOM

図7. 4相バックコンバータの正規化した電流リップル(個別L、結合L、および結合L/4)

アプリケーションによっては、目標のデューティサイクル範囲が異なり、選択するFOMはDが約0.15の例で示した値より高くなる場合があることに注意してください。ここで選択したFOM = 4は、標準的な企業アプリケーションで、図3のように高効率210nH個別インダクタを50nH結合インダクタに置き換える場合に該当します。予想されるように、はるかに小さいインダクタンス値でアプリケーションの飽和定格の要件を満たす必要があるため、結合インダクタのサイズは従来のソリューションより大幅に小さくなります。また、選択したFOM = 4は、4倍高速な過渡時の電流スルーレートにもつながり、したがって大まかに4分の1の出力容量が期待されます。

ここで示したガイドラインは、任意の数の結合された位相に適用することができます。選択するFOMは、過渡性能に対してのみ適用する必要はないことに注意してください。アプリケーションの条件とお客様の優先事項に応じて、たとえば一定のFOMと直接引き替えにする形で電流リップルを低減し、それによって回路内のあらゆる場所の導通損失を低減させることが可能です。たとえば、選択したFOM = 4と引き替えにするインダクタンス値の低減(および関連する過渡の改善)を2.6倍のみとし、残りで電流リップルの低減と効率の向上の両方を1.5倍とすることが可能です。

結合インダクタが各種の電力アプリケーションに広まるとともに、さまざまな分野の多数のお客様が確実にこの独自技術の利点を享受することになります。

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}