フェーズド・アレイの OTAパターンの測定、32素子に対応するハイブリッド・ビームフォーミングの実力を探る

概要

本稿では、32素子から成るフェーズド・アレイ・アンテナの受信性能の評価結果を示します。評価の対象とするのは、サブアレイあたり8つのアンテナ素子を備える市販のデモ用ボード(デモンストレータ)です。同ボードでは、4つのデジタル・チャンネルにより、ハイブリッド・ビームフォーミングを実行できるようになっています。本稿では、まず評価用のセットアップ、キャリブレーションの方法、その方法によって達成される精度について説明します。また、振幅のテーパリングを含めて電子的にステアリングした様々なビーム位置に対応する形で、アンテナ・アレイによる3次元の放射パターン(ビーム・パターン)を示すことにします。

はじめに

フェーズド・アレイ・システムは、航空宇宙/防衛分野だけでなく、一般的な商用分野のアプリケーションでも使われるようになりました。現在では、そうした用途も対象として、数多くの専用ICの開発が進められています。その結果、集積度の高いソリューションを採用した実用的な実装が行えるようになっています。ただ、最終的な製品を製造するまでには様々な作業を実施しなければなりません。ハードウェアの検証とソフトウェアの開発を進めるためには、プロトタイピングや開発作業を段階的に実施する必要があります。そうした状況を受けて、フェーズド・アレイ製品の開発を効率的に進められるようにするために、マルチチャンネルの完全なデモ用ボードが市販されるようになりました1、2。本稿では、アナログ・デバイセズ製のデモ用ボードを対象とした特性評価の結果を示すことにします。それらの結果は、アーキテクチャを定義する段階で活用することが可能です3、4、5。

本稿で対象とするのは、ハイブリッド・ビームフォーミングを採用したフェーズド・アレイです。完全な特性評価を行えるように構築されたデモ用ボードを使用し、レシーバー側のアンテナ・パターンを評価した結果を示します。そのボード(ハードウェア・プラットフォーム)を利用すれば、リアルタイムのハイブリッド・ビームフォーミングに適用する信号処理の開発に容易に着手できます。また、プロトタイピングにかかる時間を節約することが可能になります。電子回路全体の特性評価を事前に実施し、それと並行してソフトウェアの開発を行えば、ハードウェアの開発はリパッケージの作業になります。その結果、製品を市場に投入するまでにかかる時間を短縮することが可能になります。

本稿で取り上げるプラットフォームは、以下に挙げるような注目すべき特徴を備えています。

- C バンドに対応する最新の D/A コンバータ(DAC)と A/D コンバータ(ADC)を搭載しています。これらと組み込みDSP と併用することで、商用レベルのダイレクト・サンプリングを実現できます。また、従来は FPGA で実行していた機能を、IC上の専用ハードウェアである組み込みDSPにオフロードすることが可能です。

- デジタル・アップコンバータ(DUC)

- デジタル・ダウンコンバータ(DDC)

- NCO(Numerically controlled oscillator)による周波数と位相の制御

- 周波数チャネライザ

- X バンドに対応する商用ビームフォーマ IC(以下、BFIC)を搭載しています。

- 送信と受信の両方について、振幅と位相の独立した制御を実現できます。

- Xバンドの格子間隔内で、BFICと送信/受信モジュール(TRM:Transmit/Receive Module)が統合されています。

- MATLAB® による制御が行えます。そのため、アプリケーションに固有の無線信号に対するデジタル処理の評価に向けて、フェーズド・アレイの完全なテスト環境を迅速に構築できます。

このプラットフォームを利用すれば、完全なシステムをベースとするテスト環境でICを直接検証することができます。つまり、コンポーネントを統合する際の互換性を検証することが可能です。また、性能の見積もりも容易に実施できます。更に、得られた教訓を次世代のICに反映する機会がもたらされます。

デモ用ボードの詳細

本稿で例にとるデモ用ボードは、プロトタイピング用のプラットフォームとして使用できます。32素子を搭載しており、ハイブリッド・ビームフォーミングの機能が実装されています。図1に示したのが、そのシグナル・チェーンです1。4×8の平面アンテナ・アレイは、マイクロストリップ・パッチ・アンテナで構成されています。各パッチ・アンテナは45°の直線偏波に対応しており、各素子の間隔は10GHzの波長の1/2に設定されています。また、フロント・エンドの電子回路は32個のTRMと8個のアナログBFICで構成されています。2個のBFICの出力を組み合わせることにより、8素子のサブアレイを4組構成しています。4組のサブアレイは、マイクロ波に対応する4チャンネルのDUC/DDCに接続されています。それらのDUC/DDCは、4個のADCと4個のDACを備えるデジタイザICに接続されています。ADCのサンプル・レートは4GSPS、DACのサンプル・レートは12GSPSです。

特性評価に使用したマイクロ波の周波数は8GHz~12GHzです。局部発振器(LO)は、中心周波数が4.5GHz、固定IFのハイサイドLOとして使用しました。このIFに対応し、ADCは第3ナイキスト・ゾーンでサンプリングを行い、DACは第1ナイキスト・ゾーンでサンプリングを実行することになります。

データのキャプチャには市販のFPGAボードを使用しました。MATLABをベースとしたコンピュータ制御用のインターフェースを開発し、シミュレーション用の信号波形を使用して実際のハードウェアで迅速に特性評価を行えるようにしました。データの解析は、MATLABを使って後処理として実施します。

テスト環境のセットアップ

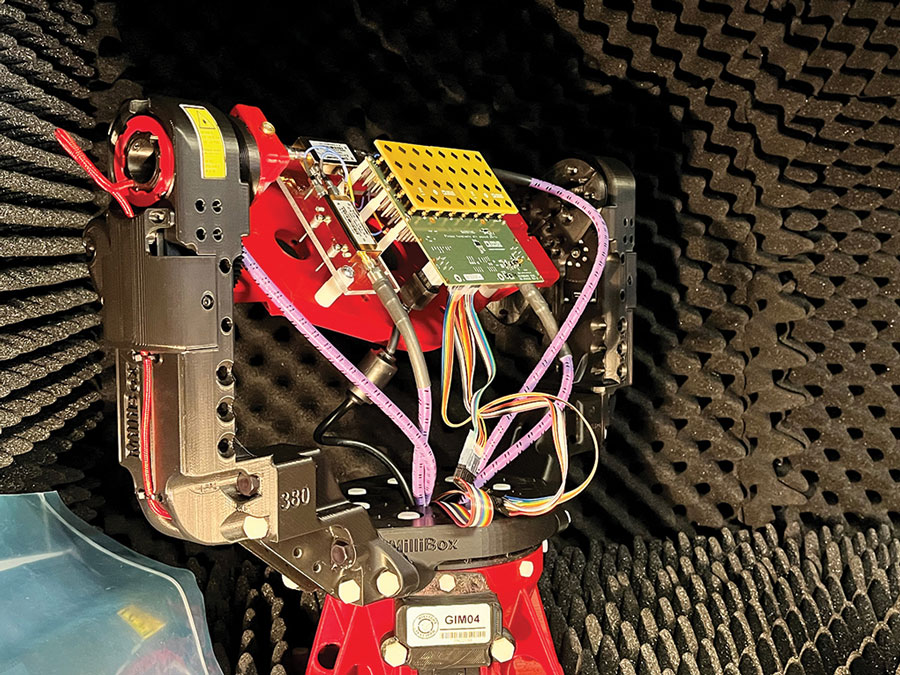

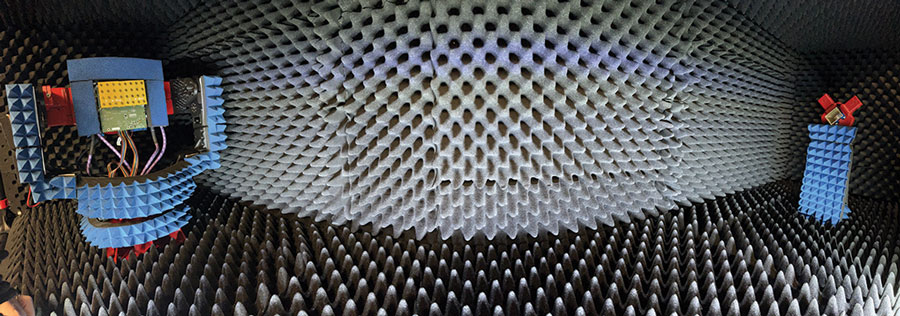

放射パターンの測定には、10フィート(約3.0m)の実験台に配置した電波暗室「MilliBox MBX33」を使用しました6。その環境を簡単に示したものが図2aです。一方、図2bにはカスタムのアダプタ・プレートを示しました。これを使って、3軸アンテナ用のポジショナ(ジンバル)「GIM04-380」にアンテナ・アレイ、アナログ・ビームフォーミング・ボード、マイクロ波スプリッタを取り付けます。RFケーブルは、ジンバルのPassThru™チャンネルを介してマイクロ波対応のDUC/DDCまで配線します。シグナル・チェーンのその他の部分は電波暗室の下に配置します。デジタル制御用のケーブルとDC電源用のケーブルも、PassThruチャンネルを介してFPGAベースのコントローラと電源まで配線しました。

アンテナ・アレイの遠方界には、Xバンド対応のホーン・アンテナを配置します。同アンテナには、電波暗室の下に置いた信号発生器を接続しました。最小遠方界は約1mであり、送信側のホーン・アンテナは1.55mの位置にあります。コントローラとしては、MATLABが稼働するPCを使用します。つまり、ハイブリッド・ビームフォーミングに対応するプラットフォーム、信号発生器、ジンバル・ポジショナはすべてMATLABで制御することになります。また、本稿で紹介するキャリブレーションと測定にもMATLABを使用します。

受信側の放射パターンを測定するために、ホーン・アンテナは連続波信号をアレイに向けて送出します。すべての素子について振幅と位相のキャリブレーションを行う場合には、アレイが-5dBFS~-10dBFSの範囲の公称電力を受信できるように信号発生器からの送信電力を調整します。アンテナ・アレイを方位角面と仰角面の両方で±90°から1°のステップで機械的に回転させながら、角度位置ごとに、FFT処理によって算出した振幅のピーク値を記録します。放射パターンは、アンテナ・アレイの角度位置に対するピーク値のプロットを基にして作成します。

図2cに示したのは、電波暗室の内部の様子です。ジンバルと被試験デバイス(DUT)が左側に配置されており、ホーン・アンテナが右側に配置されています。アレイのパッチ・アンテナは、45°の直線偏波に対応するように設計されています。送信用のホーン・アンテナは、同じく45°の直線偏波に対応するように取り付けることでパッチ・アンテナの偏波方向と一致させています。機械治具には、RF信号を吸収するフォームも追加で取り付けています。それにより、測定結果に歪みとして現れる反射を低減します。

キャリブレーション手法の詳細

すべての測定において、データの解析を行う前にキャリブレーションを実施します。このシステムは、32個のアンテナ素子、8個のBFIC、4個のADCと4個のDACを搭載した1個のデジタイザICで構成されています。デジタイザICが内蔵する4個のADCのシグナル・チェーンには、それぞれハードウェア化されたDSPブロックが含まれています。それらのDSPブロックはDDCの機能を実現します。また、各DDCはNCOを備えています。これを使用すれば、デジタル化された4つのチャンネルのそれぞれに対してサブアレイのレベルで位相シフトを適用することができます。このシステムでは、8個のアンテナ素子によって1つのサブアレイが構成されており、ADCとDSPに共通のシグナル・チェーンが共有されています。システム内では、位相と振幅の調整を行うことができます。BFICによるアナログ領域の調整と、NCOとPFIR(Programmable Finite Impulse Response)ブロックによるデジタル領域の調整の2つを組み合わせて実行します。

本稿で紹介するキャリブレーション手法は、以下に示す3つのステップから成ります。

- BFICの 可 変 ゲ イ ン ア ン プ(VGA:Variable Gain Amplifier)により、電力が最も小さい素子を基準にして振幅を正規化します。

- NCOの位相シフタ(PS:Phase Shifter)により、サブアレイごとの自然基準素子に対してサブアレイ全体としての位相をデジタル的に揃えます。

- BFICのPSにより、サブアレイごとの基準素子に対して各サブアレイ内の位相をアナログ的に揃えます。

アナログ領域では、BFICのVGAを使用してアレイ全体の振幅を揃えます(アライメント処理)。また、サブアレイ内の位相を揃える処理にはBFICのPSを使用します。一方、デジタル領域では、NCOのPSを使用することにより各サブアレイ全体で位相を揃えます。図3に示した簡略化したブロック図をご覧ください。この図を見れば、アナログ領域とデジタル領域がどのように分割されているのかがわかります。また、この図では、キャリブレーションを適切に行うためにシグナル・チェーンで使用するコンポーネントを強調表示しています。

キャリブレーションを実施する前には、受信する平面波が垂直に入射するようアレイ面の位置を調整します。それによって、各アンテナ素子が同じ電力レベルを同時に受信するようにします。キャリブレーションは、サブアレイごとに1つのアナログ・チャンネルをイネーブルにし、各サブアレイで、デジタル化された信号の複素FFT処理を行うことから始めます。具体的な例を挙げると、まずサブアレイ1~4のチャンネル1をイネーブルにし、計4つの信号をデジタイザICの4個のADCで同時にデジタル化します。次のデータ・キャプチャの段階では、各サブアレイのチャンネル1をディスエーブルにしてチャンネル2をイネーブルにします。その状態で新たなデータのキャプチャを同時に行います。このような手順でデータの同時キャプチャを更に6回繰り返します。それにより、32素子のすべてについて計8回のデータ・キャプチャを実施できます。その上でデータの後処理を行い、BFICのVGAを使用して、受信電力が最も小さいチャンネルに対して全チャンネルの振幅が等しくなるよう調整します。

各チャンネルの振幅が等しくなったら、位相を揃えるためにデータの同時キャプチャの処理を繰り返します。最初に、サブアレイ1のチャンネル1を自然基準として選択し、それに基づいて他の全チャンネルの位相を揃えます。その際には、サブアレイ1のチャンネル1と、サブアレイ2~4のチャンネル1の間の相対的な位相オフセットの値を計算します。続いて、デジタル領域でNCOのPSを使用し、サブアレイ間の相対的な差を補正します。

サブアレイ間の相対位相を揃えたら、サブアレイ内の相対位相の値を決定し、BFICのPSを使用して補正を行います。このプロセスは、サブアレイ1のチャンネル1に対するサブアレイ2~4のチャンネル2の位相差を測定することから始めます。そして、この処理をサブアレイ2~4のチャンネル8まで繰り返します。最後に、サブアレイ1の残りの素子に対する補正を行うために、サブアレイ2のチャンネル1など、新たにキャリブレーションされた基準を使用して同じ処理を繰り返します。このようなプロセスを経ることで、キャリブレーションが完了します。つまり、BFICによるアナログ位相調整によってサブアレイ内の位相誤差を補正し、ADCのシグナル・チェーン上のDSPが備えるNCOのPSによってサブアレイ間の位相誤差を補正するということです。

キャリブレーションが完了したら、振幅と位相の誤差を測定します。得られた値は、品質に関する指標として使用することが可能です。その測定にあたっては、振幅と位相それぞれのオフセットをハードウェアに適用し、キャリブレーション手法を繰り返し実施します。得られた誤差の値は、アンテナの放射パターンにキャリブレーションが与える影響を評価するためにも使用します。表1、表2は、それぞれキャリブレーションの実施後に振幅と位相の誤差を測定した結果を示したものです。いずれの表も、4×8の平面アレイ内にあるアンテナ素子の物理的な位置に対応するようにまとめてあります。

| –0.19 | –0.83 | –0.55 | –0.89 | –0.34 | –0.44 | 0.21 | –0.67 |

| –0.48 | –0.49 | –0.47 | 0.5 | –0.14 | –0.59 | 0.25 | 0.01 |

| –0.5 | –0.69 | –0.5 | –0.58 | –0.16 | 0.2 | –0.42 | –0.2 |

| –0.26 | –0.41 | –0.29 | –0.55 | –0.09 | –0.06 | –0.34 | –0.07 |

表1は、振幅の基準チャンネルが線形インデックスの30の位置にある場合の誤差を表しています。BFICのVGAの分解能はチャンネルあたり0.5dB未満です。システムの振幅誤差としては公称±0.70dBのばらつきがあり、-0.20dBの偏りがあると言えます。一方、表2は、位相の基準チャンネルが線形インデックスの2の位置にある場合の誤差を表しています。BFICのPSの公称位相分解能は2.8°です。システムの位相誤差については公称±2.5°のばらつきがあり、-1.79°の偏りがあると言えます。振幅と位相の誤差は、BFICのVGAとPSの分解能から考えて限界に近い値です。言い換えると、このハードウェアの能力によって、これ以上誤差を低減するのは難しいということです。

| –1.98 | –0.81 | –0.18 | –3.49 | –1.48 | –2.25 | –3.2 | –3.17 |

| 0 | –2.11 | –1.13 | –1.14 | –0.13 | –1.89 | –3.62 | –1.16 |

| 0.6 | –0.24 | –1.5 | –1.18 | –1.65 | –0.89 | –2.16 | –2.58 |

| –0.06 | –1.24 | –4.29 | –2.13 | –0.09 | 0.72 | –3.72 | –1.17 |

OTAのビーム・パターンの測定

続いて、OTA(Over-the-Air)のビーム・パターンの測定について説明します。その測定では、振幅に対する2種類のテーパ・プロファイルを使用します。また、10GHzの周波数を使用する4つのテスト・ケースを対象とし、キャリブレーションを行った後に測定を実施します。まず、各テーパ・プロファイルに対応して2つのステアリング角度位置で測定を実施します。その後、データセット間で直接比較を行います。それらのテスト・ケースを基に判断を行い、このデモ用ボードにおけるアレイの性能を示すことにします。データセット間の比較が容易になるように、すべての振幅のデータはテスト・ケース1のメインローブのピーク電力を使用して正規化することにします。表3は、各テスト・ケースにおける振幅のテーパ・プロファイルとステアリング角度の詳細についてまとめたものです。

| テスト・ケース | 振幅のテーパ | 方位角ステアリング角〔°〕 | 仰角ステアリング角〔°〕 |

| 1 | なし | 0 | 0 |

| 2 | テイラー | 0 | 0 |

| 3 | なし | 30 | 0 |

| 4 | テイラー | 30 | 0 |

実測を行う前に、MATLABの「Phased Array System Toolbox」を使用してシミュレーションを実施しました。周波数が10GHzという条件で、単一のパッチ・アンテナ素子のパターンとハイブリッド・アレイ全体の動作/特性を確認しました。モデルに対するシミュレーションによって得られた結果は、実測データと比較する上での基準値として利用できます。シミュレーションでは、各素子のエレメント・ファクタがcosine0.5、PSの分解能が2.8°になるように設定しました。アレイのモデルも、ハードウェアの構成に適合するようハイブリッド・アレイの形に分割しました。

図4~図7は、各テスト・ケースについてシミュレーションと実測によって得た3Dのビーム・パターン、方位角スライス、仰角スライスを示したものです。それぞれの方位角と仰角の矩形(直交座標)プロットは、モデルのデータ(モデルを使ったシミュレーションによって得たデータ)と実測データを比較できるようにしています。具体的には、モデルのエレメント・ファクタ、モデリングによる放射パターン、実測した放射パターンを重ね合わせて表示しています。表4は、各テスト・ケースにおけるフェーズド・アレイの主要な性能についてまとめたものです。

図4aに示したのは、テスト・ケース1の条件で測定した3D放射パターンです。振幅の重みはすべての素子で等しい値に設定しています。また、受信ビームは電子的にブロードサイドにステアリングされています。ここで言うブロードサイドは、0°の方位角と0°の仰角に向けたステアリング角として定義されます。メインローブのピークの振幅は-6.97dBFSです。また、図4b、図4cを見ると、第1サイドローブのレベルは約-13dBcとなっており、期待される値が得られていることがわかります。テスト・ケース1では、モデルのデータと実測データが非常によく一致しています。例えば、ヌルの位置は±1°以内に収まっています。図4bに示した8素子のアレイについては、実測されたサイドローブのレベルが35°と-55°の軸外の位置でモデルのデータ(予測値)から外れ始めています。それでも、全体としては想定される放射パターンを維持しています。図4cに示した仰角の実測データも、約±35°の軸外位置まではモデルによる予測値と非常によく一致しています。

図5aは、テスト・ケース2の条件で測定した3D放射パターンです。テスト・ケース2の振幅については30dBのテイラー・テーパで重み付けしてあります。また、受信ビームは電子的にブロードサイドにステアリングしています。図5b、図5cを見ると、振幅の重み付けの典型的な効果を確認することができます。サイドローブには30dBの低減が見られますが、これには予想されたメインローブの広がりとアレイのゲインの低下という代償が伴っています。実測データは、約±40°付近の軸外位置でモデルのデータから外れ始めます。加えて、図5bでは-50°においてサイドローブの顕著なピークが生じています。

図6aに示したのは、テスト・ケース3の条件で測定した3D放射パターンです。振幅の重みは等しい値に設定し、受信ビームについては方位角が30°、仰角が0°という設定で電子的にステアリングしています。メイン・ビームの振幅は、エレメント・ファクタに等しい比率で減少します。その値は、ブロードサイドにステアリングした場合の-6.97dBFSに対し、-7.04dBFSになっています。

図7aには、テスト・ケース4の条件で測定した3D放射パターンを示しました。振幅の重みは、サイドローブのレベルを30dB低減するテイラー・テーパに設定しています。受信ビームは、方位角が30°、仰角が0°という設定で電子的にステアリングしています。この図にも図5で見られたのと同様の効果が現れています。図7bの方位角スライスでは、サイドローブのレベルはメインローブのピークより約30dB低くなっています。また、仰角スライスのメインローブが更に広がっている点と、サイドローブのレベルが非対称である点が目立ちます。

| テスト・ケース | メインローブのピークの振幅〔dBFS〕 | 方位角の3dBビーム幅〔°〕 | 仰角の3dBビーム幅〔°〕 | 方位角の第1サイドローブの強度〔dBc〕 | 仰角の第1サイドローブの強度〔dBc〕 |

| 1 | –6.97 | 13 | 26 | –13.52 | –16.3 |

| 2 | –12.83 | 16 | 33 | –31 | –27 |

| 3 | –7.04 | 13.5 | 30 | –12 | –14.5 |

| 4 | –14.15 | 18 | 40 | 28.2 | –25 |

実測データとモデルのデータを比較すると、ずれがあることがわかります。その原因としては、小型アレイの相互結合によるエッジ効果やキャリブレーション上の誤差などが考えられます。非常に大型のアレイの場合、中央にある素子のパターンは、エレメント・ファクタとして似たような応答を示す傾向があります。一方、アレイのエッジ付近にある素子の場合、環境が非対称になります。その環境が原因で、中央の素子とは異なる影響を受けることになります。結果として、エッジの素子の放射パターンは、全体のアンテナ・パターンに対して支配的な中央の素子の放射パターンとは異なるものになります。現在も相互結合の効果を軽減するための技術が開発されていますが、本稿執筆の時点では十分な結果は得られていません10、11。

素子はすべて等しい振幅を実現し、素子間の位相シフトはすべて等しいという仮定が成立すれば、理想的なフェーズド・アレイの放射パターンを得ることができます。上では、キャリブレーションの誤差の測定結果を示しました。それを考慮して、誤差項がビーム・パターンに与える影響について把握するにはどうすればよいでしょうか。それにはモンテカルロ解析が役に立ちます。例えば、テスト・ケース3の方位角スライスと仰角スライスの両方について、±0.7dBのランダムな振幅誤差と±2.8°のランダムな位相誤差を前提としてシミュレーションを実行するといった具合です。本稿の例では、計100回にわたり反復的な解析を実施しました。その結果を図8、図9として示します。

ご覧のように、テスト・ケース3に対するモンテカルロ解析の結果を見ると、振幅誤差と位相誤差が放射パターン全体に大きな影響を及ぼすことがわかります。図8、図9において、理想的なアレイのモデルは黒いトレース、アレイの実測値は紫色のトレースで示してあります。その他のトレースはモンテカルロ手法による反復解析の結果です。どちらの図でも、振幅誤差と位相誤差がメインローブに及ぼす影響は無視できるほど小さいことがわかります。一方、最も厳しい条件のサイドローブのレベルは約-20dBcに達することが見てとれます。

モデルによる結果、実測結果、モンテカルロ解析の結果を比較すると、方位角の方向の実測結果は理想的なビーム・パターンとよく一致していることがわかります。他のデータと比べると、図6cと図7cのアンテナ・パターンでは、モデルによる結果と実測値のずれが大きくなっていることがわかります。なお、仰角スライスの実測値におけるメイン・ビームの広がりについては、取得済みのデータから明確な結論を得ることはできません。

ビーム・スクイント

ビーク・スクイントは、広帯域に対応するアンテナとPSを組み合わせて使用するフェーズド・アレイ・システムでよく見られる現象です。メインのビームのステアリングにかかる遅延時間は、周波数に対して線形な位相シフトの関数になります。そのため、狭帯域のシステムでは、あるビーム位置を実現するために必要な遅延時間には、特定の周波数における位相シフトで対応できます。それに対し、メインのビームの角度位置は、高い周波数で動作させる場合には低くなり、低い周波数で動作させる場合には高くなります7、8、9。

本稿で取り上げたデモ用ボードが備えるアンテナの帯域幅は10GHzを中心とする約1GHzです。ビーム・スクイントの影響を確認するために、テスト・ケース3の条件で方位角の方向の放射パターンを9GHz、10GHz、11GHzで測定しました。ビーム・スクイントの影響は予想が可能であり、直接計算することができます(図10)。

図10を使用すると、10GHzにおけるキャリブレーションでメインローブを30°にステアリングした場合に、ビームの角度のずれは9GHzにおいて約3.75°、11GHzにおいて-3°になることがわかります。図11に示すように、メインローブのピーク角度の測定値は9GHzでは33°、11GHzでは27°です。角度の測定値の分解能が1°であることに留意すれば、ずれの実測値と予測値は非常によく一致していることがわかります。

ビーム・スクイントの影響を排除するにはどうすればよいのでしょうか。広帯域に対応するアレイでそれを実現するためには、すべての素子に真の時間遅延回路を設ける必要があります。ただ、サブアレイのレベルのアナログPSとデジタル・レベルの真の時間遅延ユニットを利用すれば、ハイブリッド・ビームフォーミングにおけるビーム・スクイントをある程度軽減することが可能です。完全な対策だとは言えませんが、複雑さとのトレードオフという観点から見て妥当な結果を得ることができるはずです。

まとめ

本稿では、32素子から成るフェーズド・アレイ・アンテナの受信性能の評価結果を示しました。評価の対象としたのは、サブアレイあたり8つの素子が実装された市販のデモ用ボードです。同ボードでは、4つのデジタル・チャンネルにより、ハイブリッド・ビームフォーミングを実現できるようになっています。このボードを使用し、レシーバーにおけるOTAの放射性能を確認しました。測定にあたっては、複数の素子のキャリブレーションを実施するために、同期/同時のデータ・キャプチャを利用しました。その独自のキャリブレーション手法を活用することで、キャリブレーション時間の短縮を図りました。キャリブレーションに使用するオフセットは、サブアレイのレベルのアナログPSとアナログVGAによって実現しました。このボードでは、高速デジタイザが備えるハードウェア化されたDSPを使用することにより、サブアレイ全体でデジタル・ビームフォーミング機能を利用できるようになっています。本稿で示したとおり、モデルによる結果と実測結果はよく一致しています。このことから、本稿で紹介したキャリブレーション手法とデモ用ボードが備えるハイブリッド・ビームフォーミング機能は優れた結果をもたらすものであるということが確認できました。

著者について

この記事に関して

産業向けソリューション

技術ソリューション

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}