LTC4226 Hot Swap回路の並列MOSFET

良い例、悪い例、最悪例

はじめに

Hot Swap™回路で複数のMOSFETを並列に使用することは多くの場合望ましく、ときには不可欠ですが、安全動作領域(SOA)の注意深い解析が欠かせません。並列MOSFETを回路に追加する毎に、電圧降下、電力損失、およびアプリケーションに付随する温度上昇が改善されます。ただし、並列MOSFETは必ずしもトランジェントに対する回路の電力能力を改善しません。それぞれのMOSFETが独立した制御ループによって駆動されない限り、負荷の初期ターンオンや、短絡フォルトに対する電流制限などの一時的高電力事象により、1個のMOSFETへ電力が集中する傾向があります。

そのことを確認した上で、各MOSFETのSOAがトランジェント事象全体を包含できる場合に限り、MOSFETを並列に接続し、単一の制御ループを使って全体の抵抗値を減らすのが安全です。

良い例

良いSOA:独立した制御ループを備えた並列MOSFETを使用

「MOSFET Safe Operating Area and Hot Swap Circuits」の記事の中の12V/18A LTC4226アプリケーション回路は、2つの制御ループを使って2個のMOSFETを駆動しています。LTspiceのGOOD SOA simulation exampleを実行すると、SOAthermモデルがMOSFETの接合部温度を表示してSOAを検証します。このシミュレーションでは、出力がグランドに短絡してから1秒でワーストケース状態に達します。2V電圧源を一方のMOSFETのゲートに直列に接続して、しきい値の不整合をシミュレートします。(これは、温度の不整合や熱暴走によって生じるしきい値のシフトとともに、メーカーのプロセスのばらつきも表します。)回路シミュレーションを実行すると、Tj-GOOD1およびTj-GOOD2とラベル付けされているシミュレートされたMOSFETの接合部温度が、MOSFETの175°Cの最大定格接合部温度を超えないことが分かります。

良い例

悪い例

悪いSOA:並列MOSFETと単一制御ループ(18Aの代わりに9A)

BAD SOA simulation exampleは2個の並列MOSFETと5mΩの電流検出抵抗を備えています。したがって、電流制限は上の18Aに比べて9Aに減少します。Tj-BAD1とTj-BAD2のノードのシミュレートされたMOSFETの接合部温度は、最初の回路のTj-GOOD1およびTj-GOOD2と同じ温度を示します。MOSFETが損傷を受けるからこれらにBADというラベルを選択したわけではなく、最初の回路のシミュレーションではMOSFETのSOA能力がフルに利用されており、負荷への電流の2倍を安全に流すことができるからです。

悪い例

最悪例

最悪のSOA:並列MOSFETと単一制御ループ(Tj > 175°C)

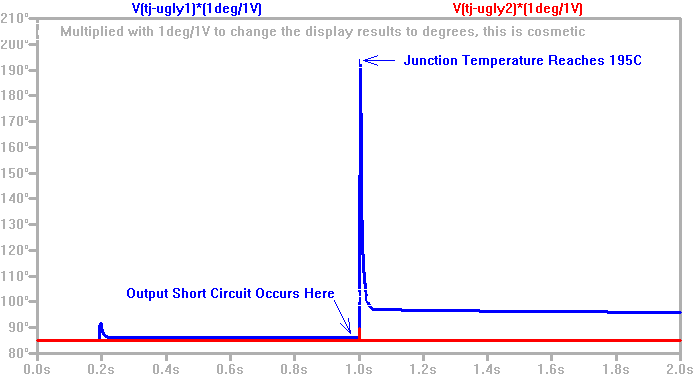

最後に、UGLY SOA simulation exampleは、最初の良い回路の2個の別々の制御ループの代わりに単一の制御ループによって駆動される2個の並列接続されたMOSFETを示しています。この場合、出力がグランドへ短絡されると、1秒後にはMOSFETの一方がトランジェント事象からの全電力を受け取り、MOSFETの175°Cの最大温度を超えます。実際の回路では、MOSFETがこの状態を耐え抜くかどうかは偶然によります。それらのしきい値が整合しており、たまたま等量の電流を分担すれば、回路は見かけ上正常に動作します。しかし、運がなければ、MOSFETの片方がより多くの電力を担い始めます。その温度が上昇し始めると、そのしきい値が下がり、まもなく全ての電力を消費するようになり、他方のMOSFETには何も残しません。そのとき、事態は明らかに最悪になります。

最悪例

まとめ

良い設計者はソリューションのコストを最少に抑え、全てのMOSFETがそれらのSOAリミットを超えないように保護します。良くない設計者は利用可能なSOAを放棄して必要以上に金を浪費します。ただし、煙と消える回路を作成して、他の設計者たちが良く見えるようにする設計者こそ最悪の設計者です。

著者について

Linear Technologyでのキャリアは、電源トラッキング・コントローラ「LTC2923/LTC2925」、高電圧に対応するデュアル理想ダイオードOR「LTC4355」...

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}