次世代絶縁型シグマ・デルタ・モジュレータによるシステムレベルの電流測定改善

はじめに

本稿では、まずコモンモード過渡耐圧(CMTI)の仕様と、システムにおけるその重要性を紹介します。更に、新しい絶縁型シグマ・デルタ(ΣΔ)モジュレータ・ファミリとその性能、そしてこれらのモジュレータがどのようにシステム電流の測定精度(特にオフセット誤差とオフセット誤差ドリフト)を改善するのかを説明します。そして、最後に推奨回路ソリューションを紹介します。

絶縁型モジュレータは、高精度の電流測定と電気的絶縁が必要とされるモータやインバータに広く使われています。モータ/インバータ・システムでは高集積化と高効率化が進んでおり、SiCおよびGaN FETがMOSFETやIGBTに取って代わりつつあります。これは、SiCおよびGaN FETの方が小型でスイッチング周波数も高く、熱放出も小さいといった利点を備えていることによります。ただし、絶縁コンポーネントには高いCMTI能力が求められます。また、より精度の高い電流測定を行う必要もあります。次世代の絶縁型モジュレータはCMTI能力を大幅に増加させ、測定精度自体も向上します。

コモンモード過渡耐圧とは

コモンモード過渡耐圧は、絶縁境界を越えて印加されるトランジェント・パルスの立上がりと立下がりのレートを規定するものです。これを超えると、クロックまたはデータが破損します。パルスの変化率と絶対コモンモード電圧(VCM)の両方が記録されます。

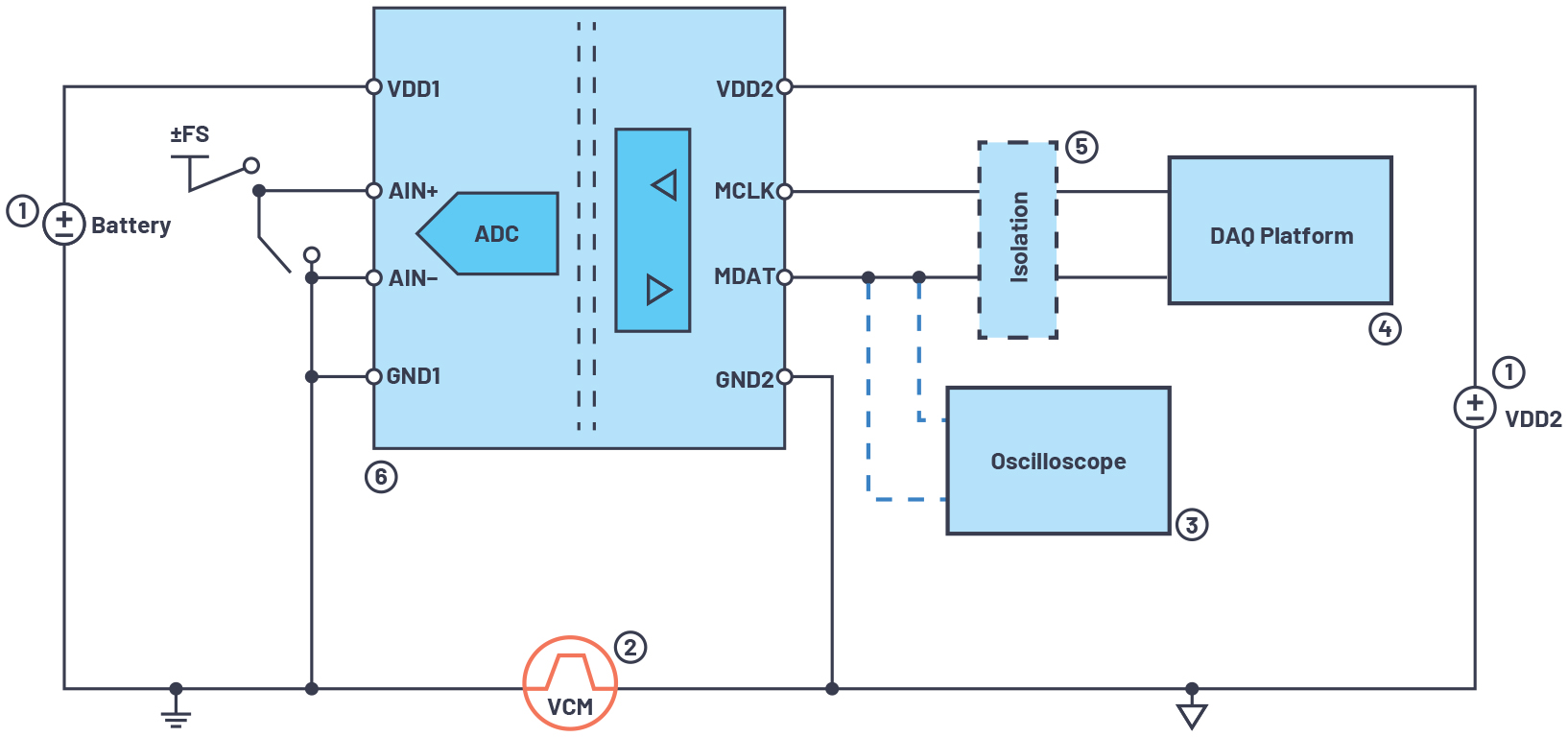

新しい絶縁型モジュレータは、静的および動的両方のCMTI条件下で試験されています。静的試験では、デバイスからのシングルビット誤差が検出されます。動的試験では、CMTIパルスをランダムに印加した際のノイズ性能の変動について、フィルタ処理されたデータ出力がモニタされます。試験の簡略ブロック図を図1に示します。

図1. CMTI試験の簡略ブロック図

高スルー・レート(高周波数)のトランジェントは絶縁バリア越しに伝送されるデータを破損させる可能性があるので、CMTIは重要な指標です。これらのトランジェントからの影響の受けやすさを理解し、それを測定することは非常に重要です。アナログ・デバイセズの試験方法は、磁気カプラのコモンモード過渡耐圧(CMTI)の測定方法などを定めたIEC 60747-17規格に基づいています。

ベンチ上で絶縁型モジュレータのCMTI特性を評価する方法

簡易CMTI試験プラットフォームには、図1に示すように以下の品目が含まれます。

- VDD1/VDD2用バッテリ電源。

- 高コモンモード電圧パルス発生器。

- データ・モニタ用オシロスコープ。

- データ解析に使用するデータ・アクイジション・プラットフォームと、絶縁型モジュレータに使用する256デシメーションsinc3フィルタ。

- 絶縁モジュール(通常は光学絶縁を使用)。

- 絶縁型モジュレータ。

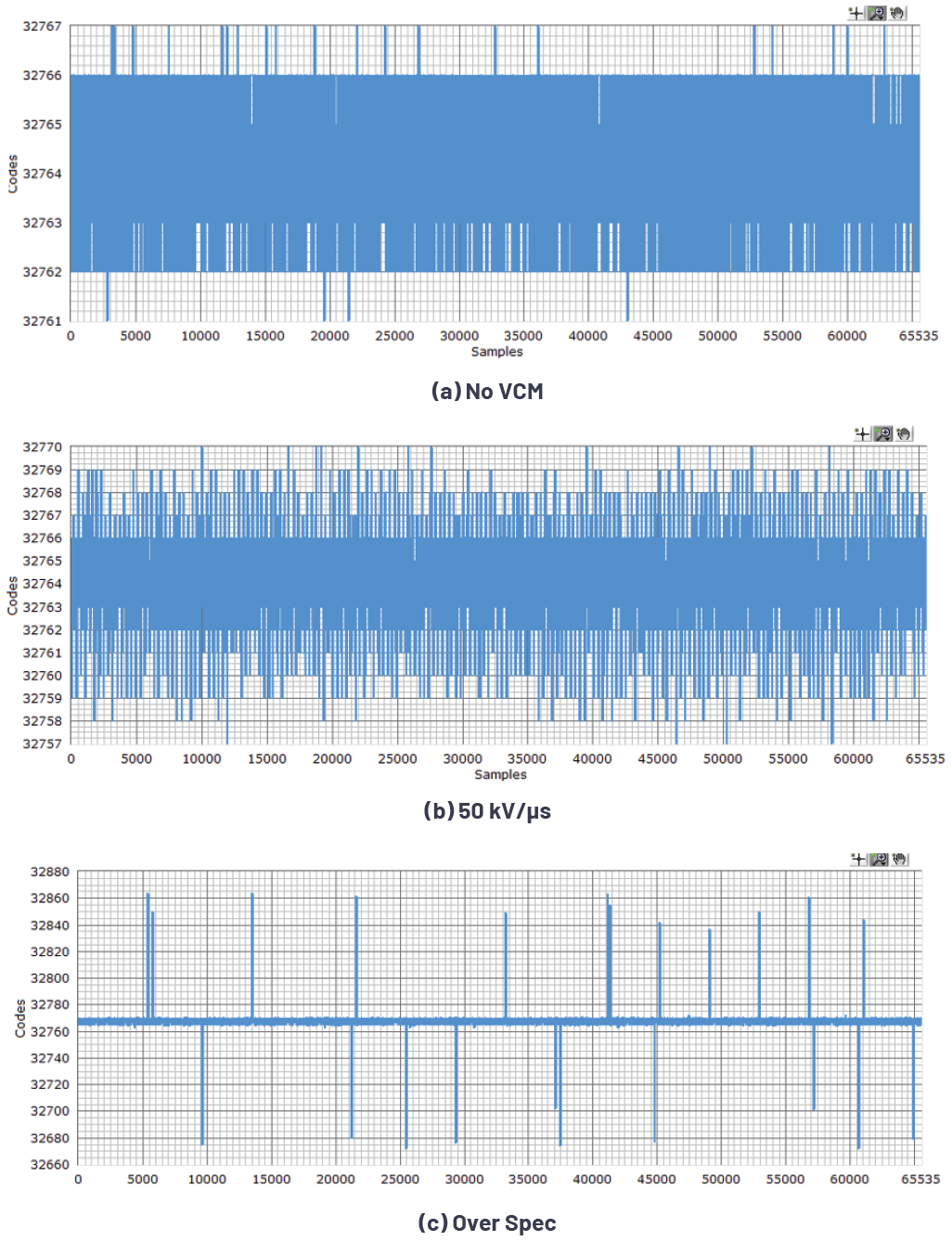

静的および動的CMTI試験には同じプラットフォームが使われます。異なるのは入力信号だけです。このプラットフォームは、他の絶縁製品のCMTI性能の試験にも使用できます。絶縁型モジュレータでは、1ビットのストリーム・データにデシメーションとフィルタ処理を行い、それをモータ・コントロール・システムの制御ループに転送するので、より包括的で有効な動的CMTI試験性能が得られます。図2と図3に、異なるCMTIレベルにおける時間領域と周波数領域のCMTI動的試験性能を示します。図2からは、同じ絶縁型モジュレータに大きいVCMトランジェント信号を加えると、スプリアスが大きくなることが分かります。VCMトランジェント信号が絶縁型モジュレータの仕様を超えると、時間領域で非常に大きいスプリアスが発生します(図2cを参照)。モータ・コントロール・システム内でモジュレータを使用する場合、これは深刻な結果をもたらし、大きいトルク・リップルを発生させます。

図2 時間領域の動的CMTI性能

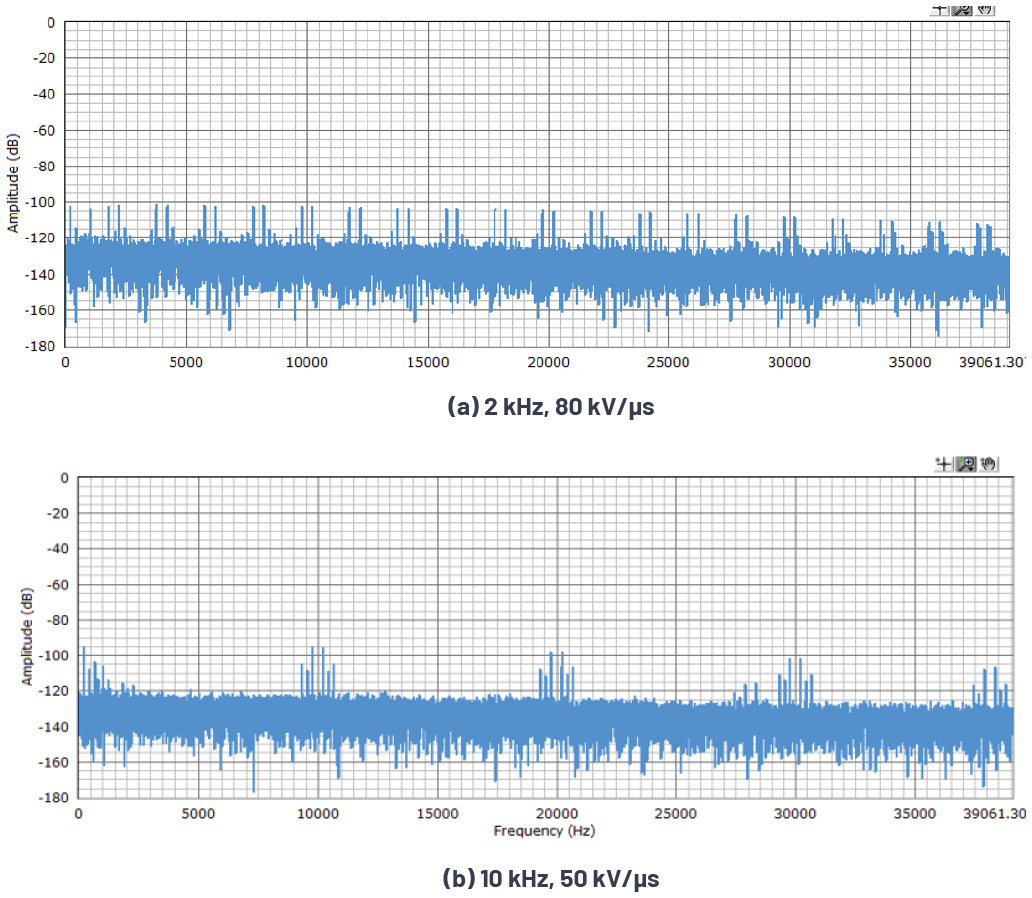

図3 周波数領域の動的CMTI性能

図3は、異なる周波数トランジェント(これはトランジェント時間を変化させることによってVCMトランジェント・レベルを維持することを意味します)におけるFFT領域の性能を示しています。図3の結果は、高調波とトランジェント周波数の間に強い関連性があることを示しています。したがって、絶縁型モジュレータのCMTI能力が高いほど、FFT解析におけるノイズ・レベルは低くなります。前世代の絶縁型モジュレータと比較して、次世代のADuM770xデバイスでは、表1に詳細を示すようにCMTI能力が25kV/µsから150kV/µsに向上しており、それによってシステムの過渡耐圧が大幅に増加します。

| 主な仕様 | ADuM7701/ ADuM7703 | ADuM7702/ ADuM7704 | AD7403 | AD7401 | |

| 絶縁 |

動作電圧(VPK) | 1270 | 1270 | 1250 | 891 |

| CMTI(kV/µs)(最小値) |

150 | 150 | 25 | 25 |

|

| 性能 |

オフセット誤差(mV最大値) |

±0.18 | ±0.18 | ±0.75 | ±0.6 |

| オフセット・ドリフト(µV/ºC最大値)、50mV時 | — | ±0.25 (16ピン)±0.6(8ピン) | — | — | |

| オフセット・ドリフト(µV/ºC max)、250mV時 | ±0.6 | — | 3.8 | 3.5 | |

| ゲイン誤差(%FSR最大値) | ±0.2 | ±0.2 | ±1.2 | ±0.3 | |

| ゲイン・ドリフト(ppm/ºC)、50mV時 | — | ±15.6 (typ)±31.3 (max) | — | — | |

| ゲイン・ドリフト(ppm/ºC )、250mV時 | ±12.5 (typ)±28 (max) | — | 65 (typ)95 (max) | 36 (typ) | |

| ENOB(ビット)、50mV時 | — | 14.2 (typ)13.1 (min) | — | — | |

| ENOB(ビット)、250mV時 | 14 (typ)13.3 (min) | — | 14.2 (typ)13.1 (min) | 11.5 (typ) | |

| 内蔵 |

LDO |

なし | あり | なし | なし |

| パッケージ | 8ピンおよび16ピン | 8ピンおよび16ピン | 8ピンおよび16ピン | 16ピン | |

システムレベルの補償およびキャリブレーション手法

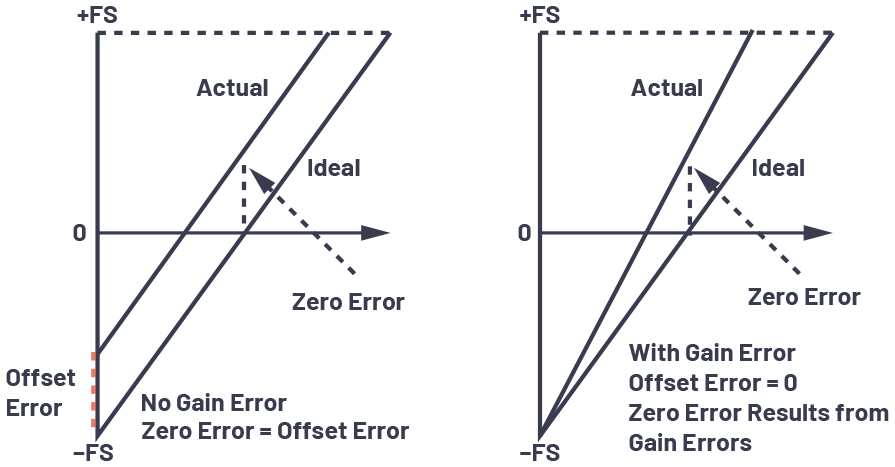

モータ・コントロール・システムやインバータ・システムでは、電流データの精度が高いほどシステムの安定性と効率が向上します。オフセット誤差とゲイン誤差は、ADCの一般的なDC誤差源です。図4に、オフセット誤差とゲイン誤差がADCの伝達関数にどのように影響するのかを示します。これらの誤差は、トルク・リップルや回転数リップルとしてシステムに影響を与える可能性があります。ほとんどのシステムでは、システムに対する誤差の影響を抑えるために、室温でこれらの誤差を補正する場合があります。

図4 ADC伝達関数のオフセット誤差とゲイン誤差

全温度範囲にわたってオフセット・ドリフト誤差とゲイン誤差を補正するのは室温での補正より難しいので、室温以外ではこれらの誤差が問題となります。システム温度が分かっている場合、ドリフト・プロファイルが直線的で予測可能なコンバータであれば、そのオフセット誤差とゲイン誤差のドリフト補正は、プロファイルに補正係数を加えて、オフセット・ドリフト・プロファイルをできるだけフラットにすることにより行うことができます(ただしコストと時間がかかります)。この補正方法の詳細は、アプリケーション・ノートAN-1377に示されています。この方法を用いれば、AD7403/AD7405のデータシートに仕様規定されたドリフト値を、オフセット・ドリフトについては最大30%、ゲイン誤差ドリフトについては最大90%減らすことができ、更にオフセット誤差とゲイン誤差のドリフトをシステムレベルで改善したい場合は、他のコンバータ・コンポーネントにもこれを適用することができます。

チョッピング手法の使用法

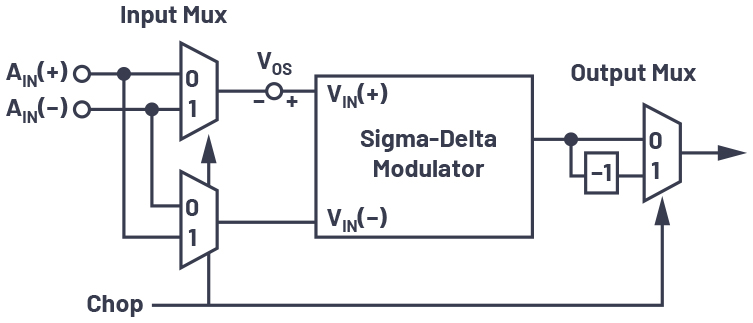

この他にも、システム設計者がより効率的で便利に使用できる、チョッピング手法と呼ばれる着想があります。チョッピング機能は、オフセット誤差とゲイン誤差のドリフトを最小限に抑えるために、シリコン自体に組み込むことも可能です。チョッピング方式の概要を図5に示します。この例では、1個のADCに実装されたソリューションが、アナログ・シグナル・チェーン全体をチョッピングして、オフセット誤差と低周波数帯の誤差を除去します。

図5 チョッピング

モジュレータへの入力は入力マルチプレクサで交互に反転され(チョップされ)、チョッピング(マルチプレクサを「0」または「1」の状態に切り替える)の各フェーズでADC変換が行われます。モジュレータのチョッピングは、出力信号をデジタル・フィルタへ渡す前に出力マルチプレクサ内で反転されます。

ΣΔモジュレータのオフセットをVOSとすると、チョップが0のときの出力は (AIN(+) − AIN(−)) + VOS、チョップが1のときの出力は −[(AIN(−) − AIN(+)) + VOS] となります。誤差電圧VOSはデジタル・フィルタでこれら2つの結果を平均することによって除去され、(AIN (+) − AIN (−)) となります。これは、オフセット項のない差動入力電圧と同じです。

最新の絶縁型モジュレータは、内部のアナログ設計を最適化して最新のチョッピング手法を使用することにより、オフセット誤差とゲイン誤差に関係する性能を向上します。これによってシステム設計が大幅に簡略化され、キャリブレーション時間も短縮されます。最新のADuM770xデバイスは最も高い絶縁レベルと最良のADC性能を備えています。LDOバージョンを使用することもできるので、システム用の電源設計が容易になります。

推奨される回路およびレイアウト設計

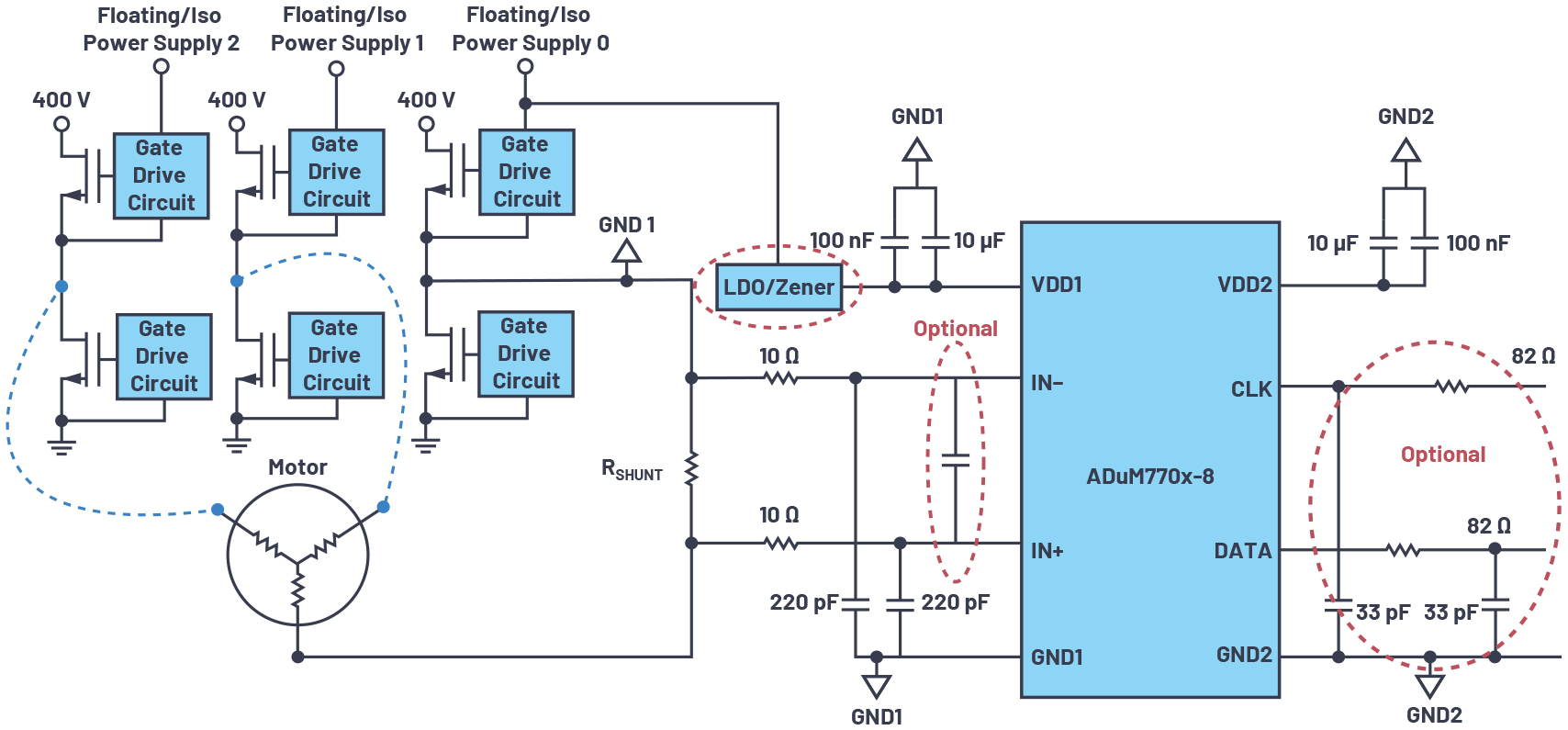

モータ・システムの代表的な電流測定回路を図6に示します。システムには3つの相電流測定回路が必要ですが、ブロック図に示したのは1つだけです。他の2つの相電流測定回路も同様の構成で、これらは青い破線で示されています。この相電流測定回路では、RSHUNT抵抗の一方の側がADuM770x-8の入力に接続されていることが分かります。もう一方の側は、高電圧FET(IGBTまたはMOSFETを使用可能)とモータに接続されます。高電圧FETのステータスが変化すると、常に過電圧状態、低電圧状態、またはその他の電圧不安定状態が生じます。これに応じてRSHUNT抵抗の電圧変動がADuM770x-8に伝達され、これに関係するデータがDATAピンに出力されます。レイアウトとシステム絶縁の設計は不安定な電圧状態を改善することもあれば悪化させることもあり、その結果は位相電流の測定精度に影響します。

図6. モータ・システムの代表的電流測定回路

図6に示す推奨回路セットアップの注意事項を以下に示します。

- VDD1/VDD2をデカップリングするためには10µF/100nFのコンデンサが必要で、これらのコンデンサは対応するピンにできるだけ近付けて配置する必要があります。

- 10Ω/220pFのRCフィルタが必要です。

- シャントによるノイズの影響を減らすために、オプションの差動コンデンサを使用することを推奨します。コンデンサはIN+/IN–ピンの近くに配置してください(0603パッケージを推奨)。

- デジタル出力ラインが長い場合は、82Ω/33pFのRCフィルタを推奨します。良好な性能を得るには、シールドされたツイスト・ペア・ケーブルの使用を検討する必要があります。

- より高い性能が求められる場合は、4端子シャント抵抗の使用を検討してください。

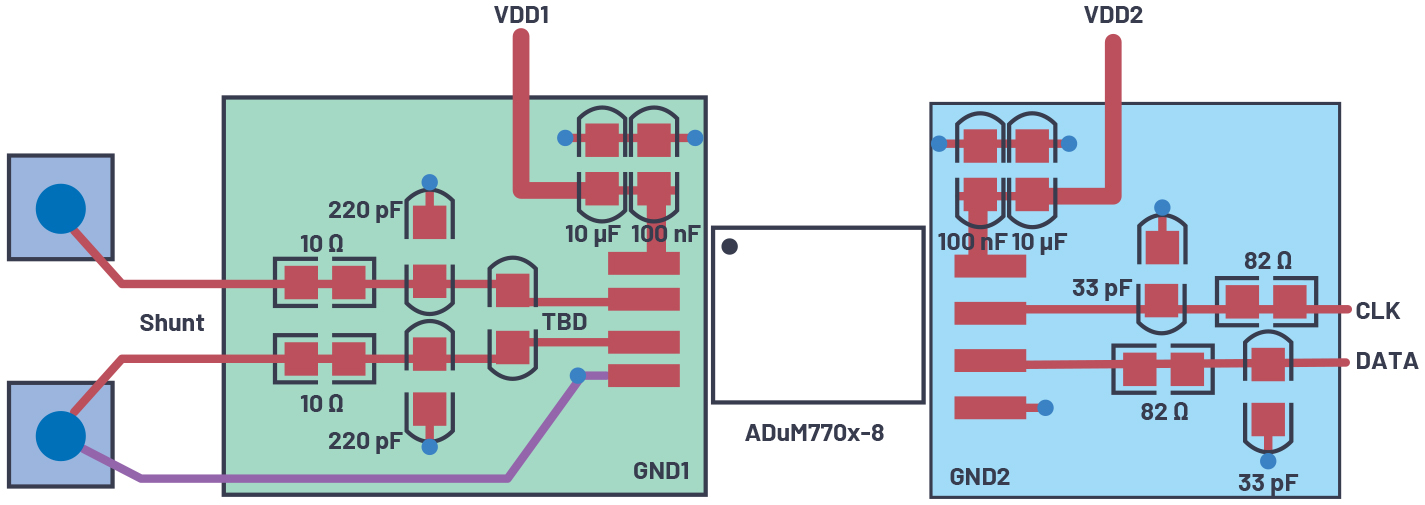

最良の性能を実現するには良好なレイアウトも必要です。推奨レイアウトを図7に示します。同相ノイズ除去能力を向上させるために、シャント抵抗からIN+/IN–入力ピンへの配線には差動ペア線を使うことを推奨します。10Ω/220pFフィルタは、IN+/IN–入力ピンにできるだけ近付けて配置する必要があります。10µF/100nFのデカップリング・コンデンサも、VDD1/VDD2電源ピンにできるだけ近付けて配置してください。パーシャル・グランド・プレーンのGND1は、信号を安定させるために入力関連回路の下に配置することを推奨します。電源電流の変動の影響を緩和するために、シャント抵抗からADuM770x-8 GNDピンへスター接続された独立のGND1ライン(差動ペア配線ラインと並列に紫で示されたライン)が必要です。

図7. ADuM770x-8回路の推奨PCBレイアウト

まとめ

最新のADuM770x絶縁型ΣΔモジュレータではCMTIが150kV/µsのレベルまで向上しており、温度ドリフト性能も改善されています。これは、電流測定アプリケーションにとって大きな利点です。また、推奨される回路とレイアウトを使用すれば、設計段階の大きな助けとなります。

著者について

この記事に関して

製品

シグマ・デルタ変調器、絶縁型

シグマ・デルタ変調器、16ビット、絶縁型

16ビット絶縁型シグマ・デルタ・モジュレータ

産業向けソリューション

製品カテゴリ

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}