絶縁型高周波プッシュプル DC/DC コンバータの設計方法

デューティ・サイクルが 50%に固定されたシンプルなプッシュプル DC/DC コンバータは、主に低ノイズのトランス・ドライバとして通信システム、医療機器、分散型電源に使われています。このシンプルな方式では電圧レギュレーションを行わないため、レギュレーションには低ドロップアウト(LDO)のポスト・レギュレータが必要となりますが、この組み合わせは深刻な問題を引き起こすおそれがあります。第一に、50%固定のデューティ・サイクルでドライバの入力電圧が大きく変動すると LDO 前後の電圧差が増大し、LDO に著しい電力損失と温度上昇が生じる可能性があります。第二に、低スイッチング周波数では比較的大きなトランスが必要となり、場合によってはコンバータ・スペースの 30%~50%を占めてしまうことがあります。

LT3999 モノリシック DC/DC プッシュプル・ドライバは、2 つの重要な特徴であるデューティ・サイクル制御と高周波数動作によって、これらの問題を回避します。

- デューティ・サイクル制御は、標準的な固定デューティ・サイクルのトランス・ドライバでは望めない幅広い VIN の変動を補償して、入力範囲が広い場合でも LDO の損失を大幅に減らします。

- 最大 1MHz の高スイッチング周波数は、より小さいトランスの使用を可能にして出力リップルを減らします。

LT3999 は、これら 2 つの特徴と、36V の高入力電圧および 1A の入力電流を組み合わせることで、高出力で柔軟な低ノイズのプッシュプル・コンバータ IC を実現しています。

本稿では、2 つの段階的設計手順を示します。1 つは広い入力範囲を持つプッシュプル DC/DC コンバータの設計手順で、もう1つは固定入力電圧のコンパクトな高周波トランス・ドライバの設計手順です。

広い入力範囲に対応したプッシュプル DC/DC コンバータの設計

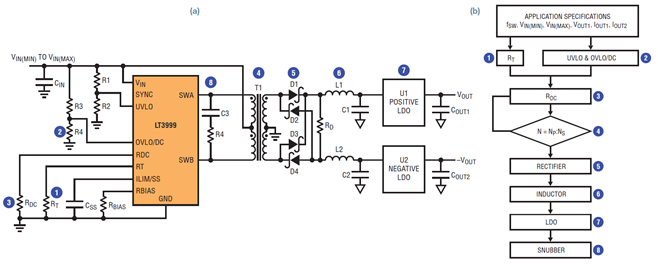

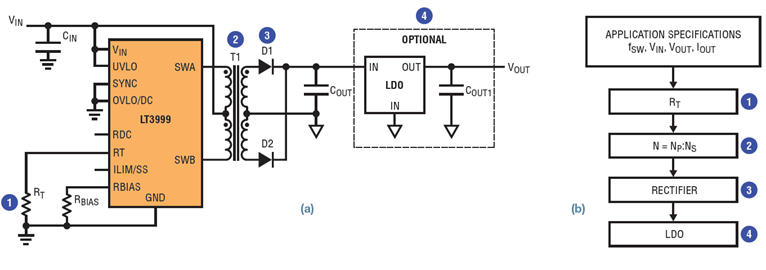

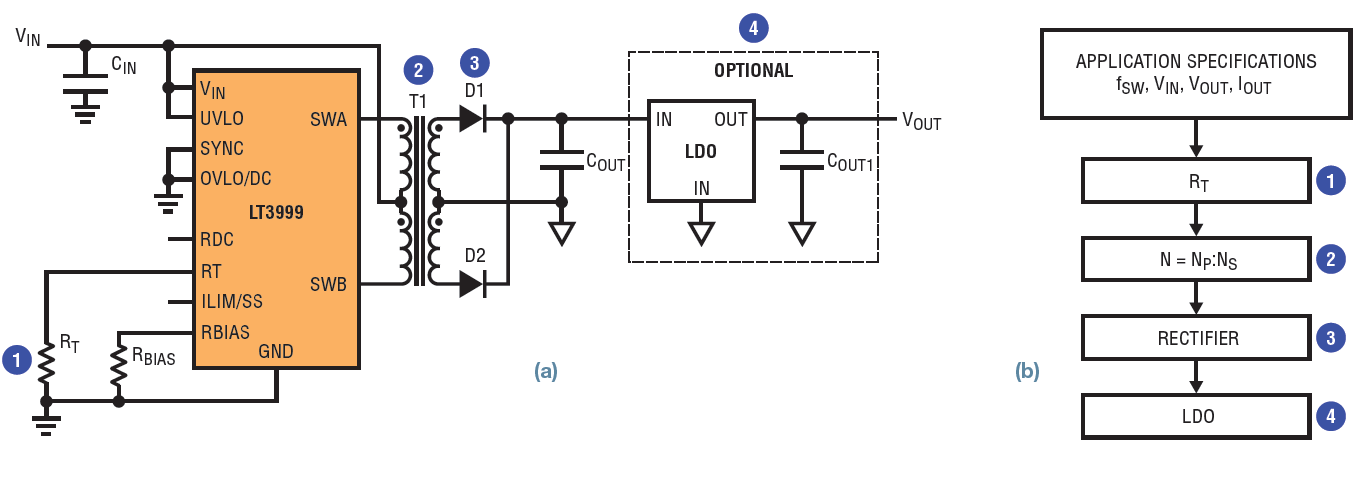

図 1b のフローチャートは、8 つの簡単なステップでプッシュプル・コンバータを設計する方法を示しています。図 1a に示す LT3999 プッシュプル・コンバータ(10V~15V 入力、±12V 出力、200mA、1MHz)は、このステップに従って作成されています。

図 1.(a) 広い入力範囲を持つデューティ・サイクル制御可能な LT3999 プッシュプル DC/DC コンバータ (b) 簡単な 8 ステップのプッシュプル・コンバータ設計

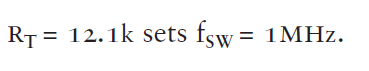

ステップ 1:スイッチング周波数(RT)の設定

最初に、RT(LT3999 のデータシートの表1 から選択した値)を使ってスイッチング周波数を設定します。

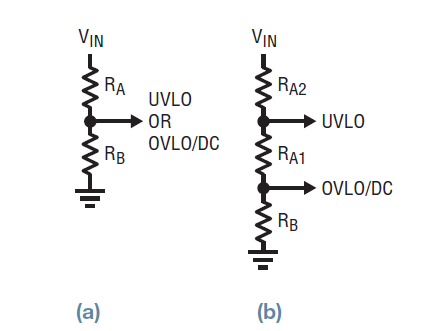

ステップ 2:入力電圧範囲(UVLO、OVLO/DC)の設定

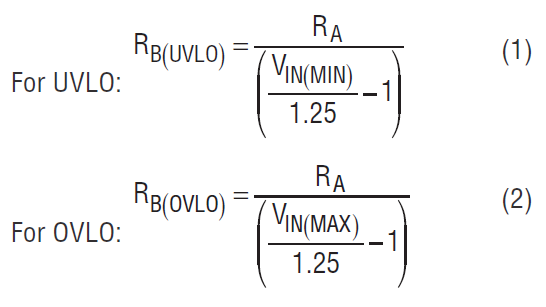

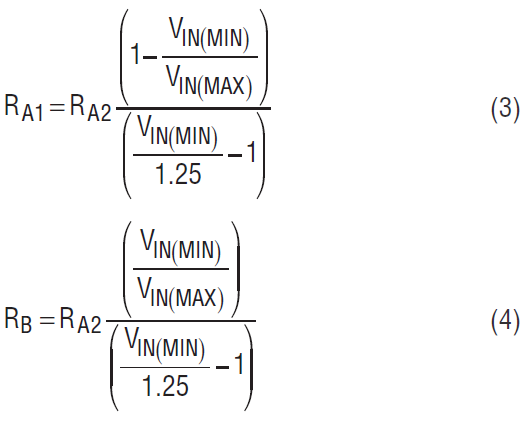

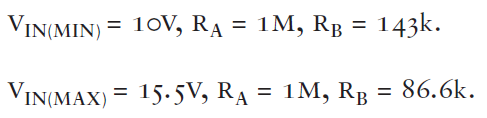

UVLO(低電圧ロックアウト)およびOVLO/DC(過電圧ロックアウト/デューティ・サイクル)ピンを使って、入力電圧範囲を設定します。2 抵抗法と 3 抵抗法のどちらも使用できます。図 2a に示す 2 抵抗法の場合は、UVLO には式 1 を、OVLO/DC には式 2 を使って RBを計算します。損失を低く抑えるために、RA = 1MΩと仮定できます。

図 2b に示す 3 抵抗法の場合は、UVLO には式 3 を、OVLO/DC には式 4 を使って、RA1と RBを計算します。RA2には約 1MΩの値を選択できます。

図 1a に使用されている 2 抵抗法の場合は、次のようになります。

ステップ 3:最大デューティ・サイクル(RDC(MAX))の設定

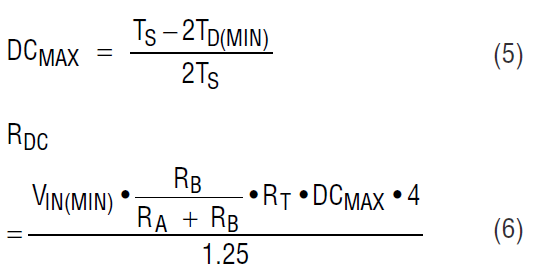

最大デューティ・サイクル(DCMAX)は、式 5 に示すように、スイッチング周期(TS = 1/fSW)と、2 つのパワー・スイッチ間の非オーバーラップ時間(TD(MIN))によって決まります。2 抵抗法では、RDCは式 6 で計算します。3 抵抗法の場合は、式 6 のRA を RA1 + RA2に置き換えます。

図 1(a)の例では、TS = 1µs、TD(MIN) = 70ns(データシートの代表値)、VIN(MIN) = 10V、RA = 1M、RB = 143k です。式 5 と式 6 を計算すると、DCMAX = 0.43、RDC = 13.3kとなります。

ステップ 4:トランス(T1)の選択

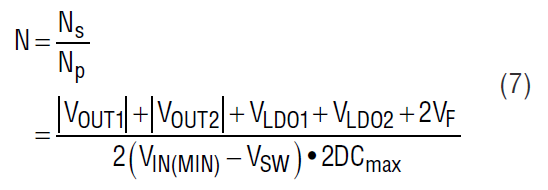

トランスの巻数比は、式7で表されます。

VSW は内部スイッチのスイッチ飽和電圧、VF は整流ダイオードの順方向電圧です。VLDO1と VLDO2は、正電圧 LDO と負電圧 LDOのドロップアウト電圧です。およその目安となる値は、VSW = 0.4V、VF = 0.7V、VLDO1 = VLDO2 = 0.8V です。計算した巻数比とまったく同じ巻数比の市販トランスが見つからない場合は、近い値のものを選び、その値に応じて式 7 から DCMAXを計算します。次に、新しい DCMAXに基づいて、式 6 から RDCを計算します。

図 1(a)の例では、VOUT1 = −VOUT2 = 12V、VIN(MIN) = 10V なので、DCMAX = 0.43 に対して Wurth 750314781(N = 2)を選択します。

ステップ 5:整流器(D1、D2、D3、D4)の設計

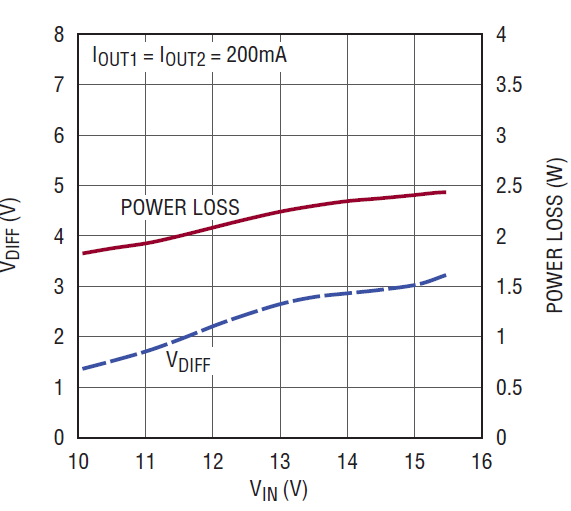

整流器ブリッジにかかるピーク電圧は、トランスの 2 次側電圧(VSEC)とリンギング電圧スパイクから成ります。VSEC は式8 を使って計算します。しかし、リンギング電圧スパイクはループ抵抗、トランスの漏れインダクタンス、および整流器の接合容量に依存するので、その値を予測するのは困難です。原則として、整流器の電圧定格(VREC)は、トランスの巻数比に最大入力電圧を乗じた値の1.5倍以上にする必要があります。ここでは、整流器ブリッジを介して 2 つの 2 次巻線が接続されているので2倍にする必要があり、次のような整流器電圧定格の式が得られます。

整流器の電流定格(IREC)は、負荷電流より大きくする必要があります。

VIN(MAX) = 15.5V、N = 2、VREC ≥ 93V、IREC ≥200mA の場合は、Central CMSH1-200HE(200V、1A)がこれらの条件を満たします。

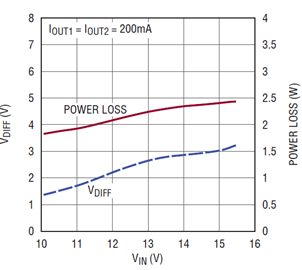

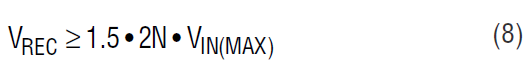

図 3. LDO(U2)の入出力電圧差 VIN − VOUTおよび電力損失と入力電圧の関係

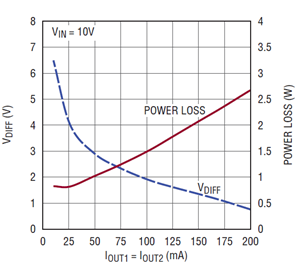

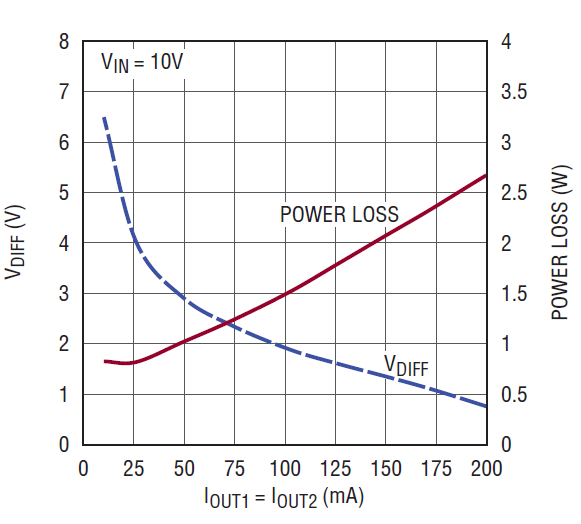

図 4. LDO(U2)の入出力電圧差 VIN − VOUTおよび電力損失と負荷の関係

ステップ 6:インダクタ(L1、L2)の選択

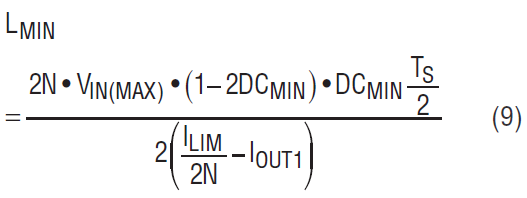

最小インダクタ値(LMIN)は、式 9 に示すように内部スイッチャのピーク電流制限値(ILIM)によって設定されます。

インダクタンスが大きいほどレギュレーションは良くなり電圧リップルは低くなりますが、それに応じて、より大きな部品が必要になります。最適なインダクタ値は、出力ノイズとソリューション・サイズの両方の要求を考慮した上で決定します。

VIN(MAX) = 15.5V、DCMIN = 0.28、TS = 1µs、N = 2、ILIM = 1A、IOUT1 = IOUT2 = 200mA、LMIN = 38.3µH の場合は、 Coilcraft XFL3012-393MEC(39.3µH)がこれらの条件を満たし、不必要にサイズが大きくなることもありません。

ステップ 7:低ドロップアウト・リニア電圧レギュレータ(U2、U3)の選択

LDO の最大電圧は、無負荷、最大入力電圧で VSEC = VIN(MAX) • N のときに発生します。LDO の電流定格は負荷電流より大きくする必要があります。

VIN(MAX) = 15.5V、N = 2 のときの LDO の電圧定格は 31V および−31V とする必要があり、これらの条件はそれぞれ LT3065(45V、500mA)と LT3090(−36V、400mA)によって満たすことができます。

ステップ 8:スナバ(CSと RS)の追加

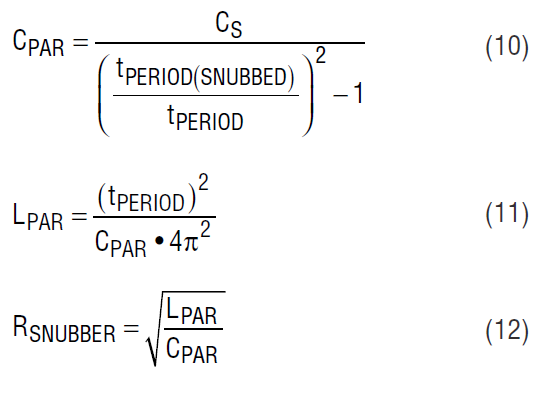

RC スナバ(図 1 の CS と RS)の設計に推奨されるアプローチは、スナバなしの状態で、LT3999 のスイッチャがオフになるときにその SWA ピンと SWB ピンにおけるリンギングの周期を測定して、リンギング周期が 1.5 倍~2 倍になるまで容量を増やしていく方法です(100pF 程度のものから始めます)。

この周期の変化が寄生容量(CPAR)の値を決定し、さらにこれを使って最初の周期から寄生インダクタンス(LPAR)を決定することができます。同様に、データシートに記載されているスイッチ容量とトランスの漏れインダクタンスの値を使い、初期値を予測することができます。

ドレイン・ノードの容量とインダクタンスの値が分かれば、スナバ容量に直列抵抗を追加して電力を消費し、リンギングを大幅に減衰させることができます。測定した周期(tPERIODおよび tPERIOD (SNUBBED))とスナバ容量(CS)を使って、最適な直列抵抗を求めるための式を下に示します。詳細については LT3748 のデータシートを参照してください。

結果

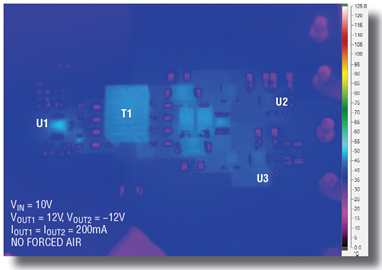

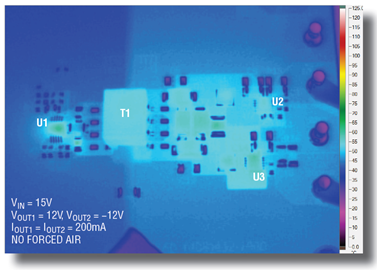

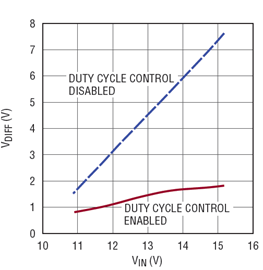

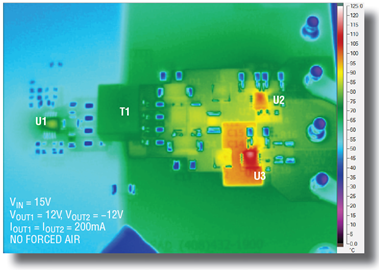

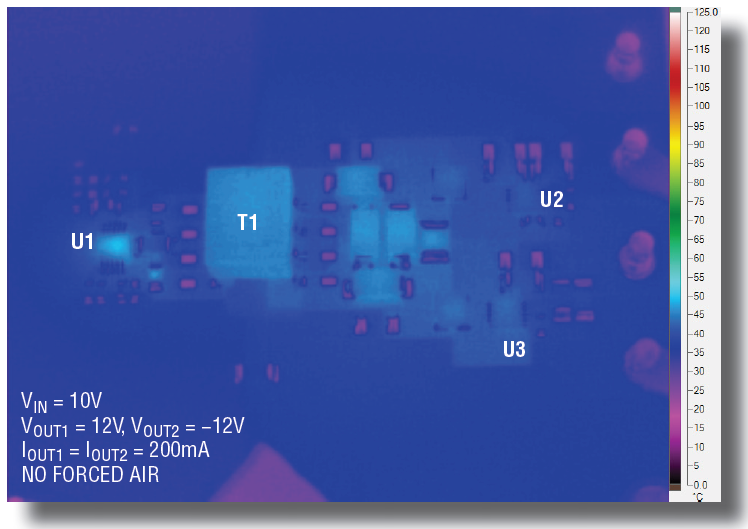

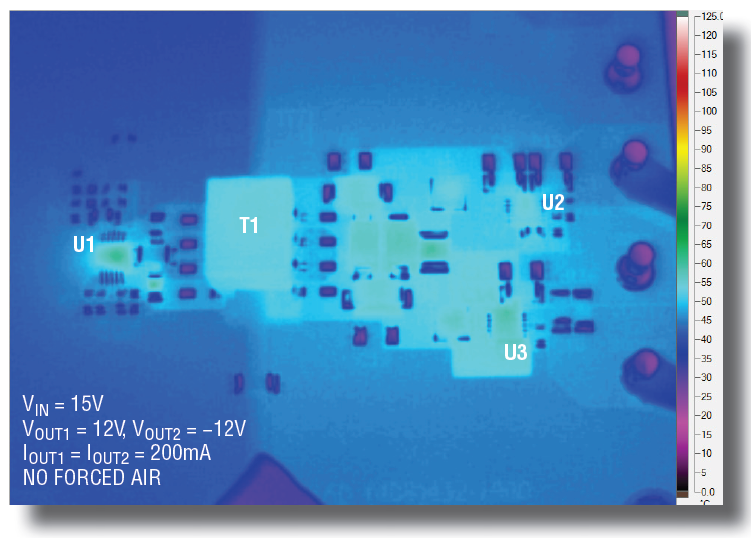

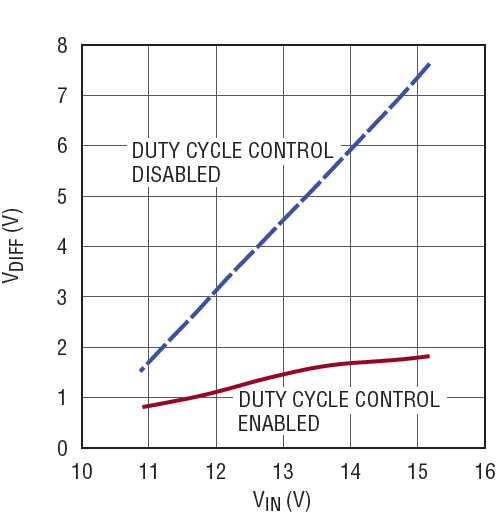

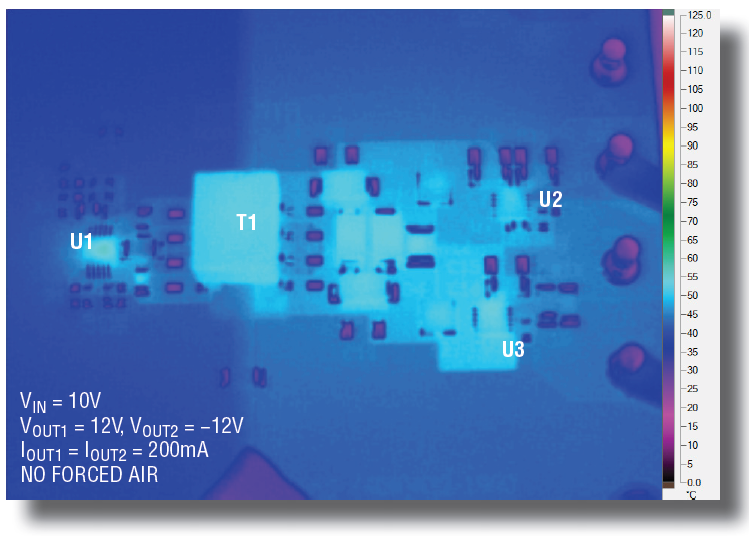

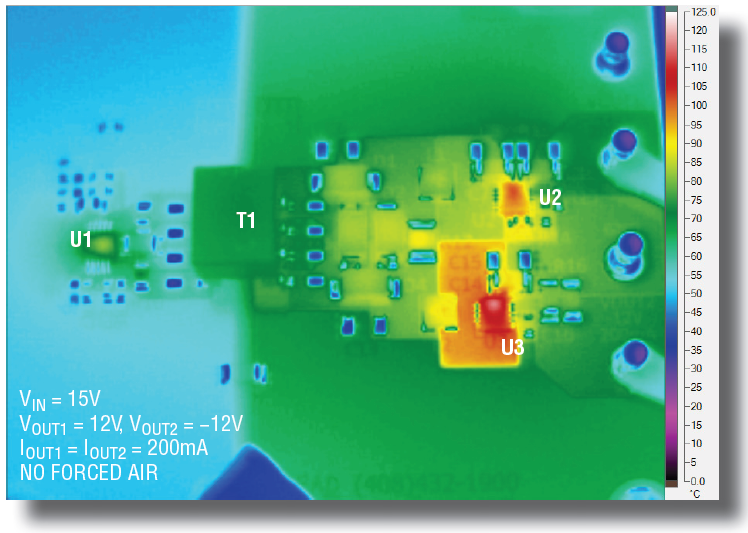

図 3、4、5 の測定結果は、図 1 に示すプッシュプル・コンバータのデューティ・サイクル制御が LDO の入出力電圧差VIN − VOUTを低い値に抑えて、電力損失と温度上昇を最小限に止めていることを示しています。図 3 は、LDO あたりの電流が 200mA の場合、10V~15V の入力電圧範囲全体にわたり、VDIFF が 2.5V 未満であることを示しています。図 4 は、負荷電流範囲では電力損失が低い値に止まることを示しています。熱測定の結果を図 5 と図 6 に示します。

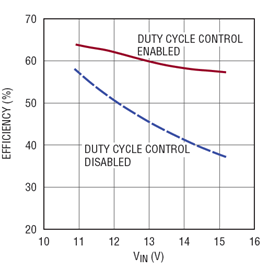

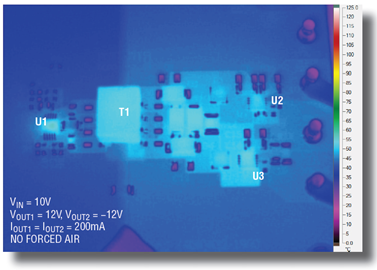

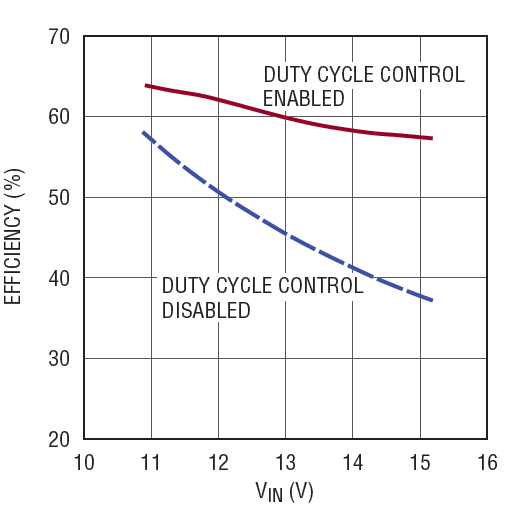

さらに、デューティ・サイクル制御を無効にした場合と有効にした場合で、設計回路の効率を比較した結果を図7に示します。入力電圧が増加すると効率は大幅に低下します。図 8 は、デューティ・サイクル制御を無効にした場合と有効にした場合の、正電圧 LDO の入出力電圧差です。図 9 と 10 は熱測定の結果です。デューティ・サイクル制御によって入出力電圧差が小さくなり、効率と熱性能が改善することがはっきりと分かります。

図 5. 図 1 の回路を動作させた場合の熱画像(VIN = 10V)

図 6. 熱画像(VIN = 15V)

固定入力電圧用のコンパクトなトランス・ドライバ

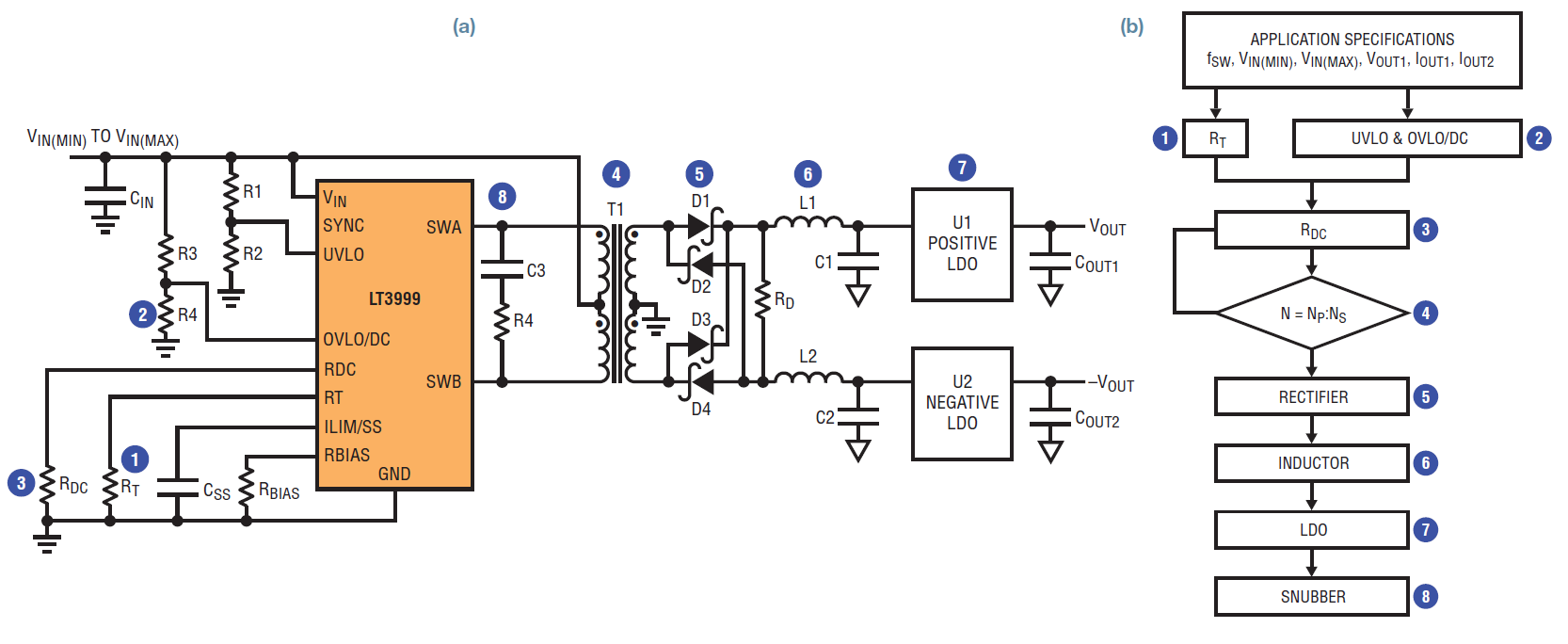

通常、レギュレーションされていない基本的なトランス・ドライブ・コンバータの出力電圧は、負荷電流の変化に応じて大きく変化します。レギュレーションされた電圧を生成するには、出力に LDO を置くことを強く推奨します。LT3999 を使用した、部品数の少ないトランス・ドライバの回路図を図 11a に示します。図11b は設計フローチャートです。

フローチャートに示す4つの簡単なステップを使って、たとえば、1MHz、5V 入力、5V/400mA 出力の、部品数の少ないトランス・ドライバを設計することができます。

ステップ 1:スイッチング周波数(RT)の設定

LT3999 のスイッチング周波数は、LT3999データシートの表に基づいて選択した 1個の RT抵抗によって設定できます(周波数範囲は 50kHz~1MHz)。

この設計例では、fSW = 1MHz の高周波数に対して RT = 12.1k です。

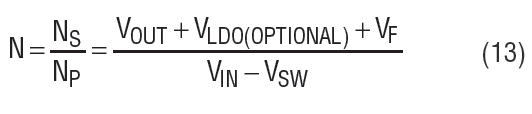

ステップ 2:トランスの選択

トランスの巻数比は、次式で決まります。

ここで、VSWは内部スイッチャのスイッチ飽和電圧、VFは整流ダイオードの順方向電圧です。

図 7. IOUT1 = IOUT2 = 200mA でデューティ・サイクル制御を無効にした場合と、有効にした場合の設計回路の効率の比較

VLDOは、レギュレーションされていないトランス・ドライバ出力からポスト・レギュレーションされた低ノイズ出力への電圧の低下です。VLDO は最大電流時の低下なので、最小限に抑える必要があります。低下が 0.8V であれば、LDO を過熱させることなく十分にドロップアウトを防ぐことができます。およその目安となる値は、VSW = 0.4V、VF = 0.7V、VLDO = 0.8V です。

トランスの電流定格は、ある程度の余裕を持たせるために、出力電流より 20%~50%大きくする必要があります。

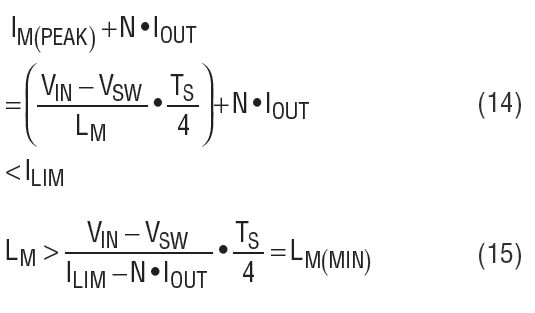

ピーク磁化電流(IM(PEAK))と 1 次側に反映される全負荷電流(N • IOUT)の合計は、内部スイッチャのピーク電流制限値(ILIM)未満とする必要があります。これに基づく最小 LM(LM(MIN))が必要です。

図 8. LDO(U2)の入出力電圧差 VIN − VOUTとVIN の関係(全負荷時にデューティ・サイクル制御を無効にした場合と有効にした場合、IOUT1 = IOUT2 = 200mA)

図 9. 図 1 の設計回路でデューティ・サイクル制御を有効にした場合の熱画像、VIN = 10V

図 10. 図 1 の設計回路でデューティ・サイクル制御を無効にした場合の熱画像、VIN = 15V

VOUT = VIN = 5V の場合は、CoilcraftPA6383-AL(N = 1.5)が好適です。

ステップ 3:整流器(D1、D2)

電圧と電流に基づいて整流ダイオードを選択します。トランスはセンター・タップ構造なので、ダイオードにかかる電圧は 2 次側電圧の 2 倍以上になります。整流器の定格は、2N • VIN = 15V 以上にする必要があります(約 20%大きくする)。

図 11.(a) 部品数の少ない固定入力電圧のトランス・ドライバ (b) トランス・ドライバの設計フローチャート

CMSH1-20M(20V、1A)はこれらの要求を満たします。

ステップ 4:低ドロップアウト・リニア電圧レギュレータ(U2、オプション)

オプションのポスト・レギュレーションLDO の最大入力電圧(VLDO_IN(MAX))は無負荷時に発生し、その値は VIN • N = 7.5Vに等しくなります。LDO の電流定格は負荷電流より大きくする必要があります(この設計例の場合、>400mA)。

5V、400mA の出力に適した LDO は、LT1763です(20V、500mA)。

まとめ

モノリシック DC/DC トランス・ドライバLT3999 は、デューティ・サイクル制御、高周波数、高出力が特長です。このデバイスは広い入力電圧範囲に対応しており、LDO の損失を低く抑えることができるほか、高周波動作なので小型の受動部品を使用することができます。入力電圧は最大 36V、入力電流は最大 1A です。

著者について

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}