要約

民生品製品が小型化、軽量化、および薄型化する傾向に合わせて、より小さなパッケージタイプが開発されています。実際、パッケージは、新しい設計にデバイスを使用するかしないかを決定する主要因になっています。この記事では、まず、「フリップチップ」と「チップスケールパッケージ」という用語を定義し、ウェハレベルパッケージ(WLP)技術の開発について説明します。次に、ウェハレベルパッケージデバイスの実用面について説明します。この説明のトピックとしては、特定デバイスのフリップチップ/UCSP™パッケージの入手性の確認、マークによるフリップチップ/UCSPの識別、ウェハレベルでパッケージ化された製品の信頼性、および信頼性に関する適切な情報の検索があります。このアプリケーションノートの最後には、パッケージ開発の将来の展望、このアプリケーションノートの記述に使用した参考文献、ここで説明しないトピックを扱ったその他の文献へのリンクを記載しています。

はじめに

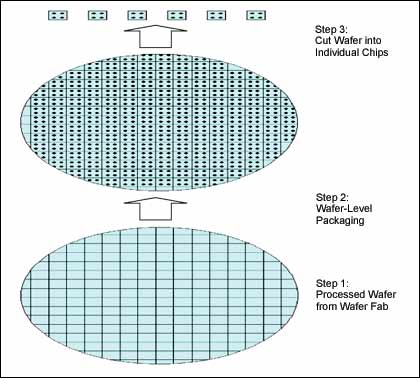

半導体技術の進歩によって、数年前では考えられなかったトランジスタ数と機能を備えたチップが実現しています。現在のポータブル電化製品は、同様に優れたICパッケージの開発がなければ実現しません。民生品製品が小型化、軽量化、および薄型化する傾向に合わせて、より小さなパッケージタイプが開発されています。可能な最小パッケージは常にチップそのもののサイズです。図1は、ウェハから個々のチップまでICを製作する手順を示しています。図2は、実際のチップスケールパッケージ(CSP)です。

チップサイズのパッケージの概念は、1990年代に考案されました。1998年に定義されたCSPカテゴリの中に、ウェハレベルCSPが登場しました。これは、EEPROMのようなピン数の少ないデバイスからASICやマイクロプロセッサに至るまで、幅広いアプリケーションに使用することのできる経済的な選択肢です。CSPデバイスは、ウェハレベルパッケージ(WLP)と呼ばれる工程で製造されます。WLPの主な特長は、パッケージの製造とテストがすべてウェハ上で行なわれることです。ウェハのサイズが大きくなり、チップが小さくなるほど、WLPのコストは下がります。早くからこの技術を採り入れたDallas Semiconductorは、1999年にウェハレベルパッケージの製品の出荷を開始しました。

図1. 処理したウェハを個々のチップに最終的に分割するウェハレベルパッケージ(簡略)。

図2. 12バンプのチップスケールパッケージ。3 × 4バンプで、2バンプは未実装

用語

業界では、WLPの用語がいまだに定まっていません。CSPに対するウェハレベルの手法が独自である理由は、パッケージ内でのボンディング技法が他にないためです。パッケージ化されたチップにも決まった呼び方はありません。よく使用される説明調の名称は、フリップチップ(STMicroelectronicsおよびDallas Semiconductor®)、CSP、チップスケールパッケージ、WLCSP、WL-CSP、MicroSMD (National Semiconductor)、UCSP (Maxim Integrated)、バンプダイ、およびMicroCSP (Analog Devices)です。

Maxim®/Dallas Semiconductorでは、当初、「フリップチップ」および「チップスケールパッケージ」という用語をウェハレベルでパッケージ化されたチップのすべてに対して同意語として使用していました。長年の間に、さらに多くの特性がパッケージ用に開発されました。このアプリケーションノートおよびMaximのすべての資料(当社のウェブサイトを含む)では、「フリップチップ」という用語は、さまざまな位置(端までには隙間がある)に配置可能な任意の形状のバンプを備えた、ウェハレベルでパッケージ化されたチップを表します。「チップスケールパッケージ」という用語は、規定のピッチでグリッドに球状のバンプが配置されているウェハレベルでパッケージ化されたチップを表します。図3は、これらの違いを示しています。すべてのグリッド位置に実装が必要ではないことに注意してください。

図3のフリップチップの寸法は、第1世代のDallas SemiconductorのWLP製品の寸法です。チップスケールパッケージの寸法は、Maximを含むさまざまなベンダの寸法をまとめたものです。現行のMaximおよび新しいDallas Semiconductorのチップスケールパッケージ製品の主な寸法を表1に示します。

図3. チップスケールパッケージとフリップチップパッケージの一般的な寸法および相違点

| Parameter | Designator | Value |

| No. of Bumps | (---) | 4 to 36 |

| Bump Diameter | b | 0.30, 0.35mm |

| Bump Height | A1 | 0.25, 0.3mm |

| Bump Pitch | e | 0.5mm |

| Die Thickness | A2 | 0.33, 0.38mm |

ウェハレベルパッケージ(WLP)技術

WLP製品を提供しているベンダは、自社でWLPファブを所有しているか、パッケージ工程を外部委託しています。したがって、最終製品の信頼性を保証するためにユーザが満たさなければならない要件が変わると、製造工程も変わります。「Wafer-Level Packaging Has Arrived」8、「The Wafer-Level Packaging Evolution」9、および「WLCSP Technology Direction」10の記事には、WLPの過去および未来に関する興味深い概要が記述されています。アリゾナ州フェニックスのFCI、およびノースカロライナ州リサーチトライアングルパークのUnitive®は、UltraCSP (FCI)およびXtreme (Unitive)という製品名の下でWLP技術の標準を作成しました。Unitiveを買収したAmkorは、世界中の半導体業界にWLPのサービスを提供しています。11

回路/ワイヤボードのトレースにチップを接合するバンプは、もともと錫と鉛の共晶*合金(Sn63Pb37)でできていました。電子製品の有害物質を除去する指令(RoHS)によって、半導体業界は、Pbフリーのバンプ(Sn96.5Ag3Cu0.5)や高Pbのバンプ(Pb95Sn5)などを代替品に採用することが必要になりました。合金にはそれぞれの融点があるため、部品実装のリフロー工程では、特定の温度プロファイル(特定温度での期間)が必要です。

集積回路は、必要なすべての電気的機能を実現し、特定のパッケージに適合するように設計されています。チップ上のボンディングパッドは、ワイヤボンディングで従来のパッケージのピンに接合されます。従来のパッケージの設計ルールでは、ボンディングパッドをチップの周囲に配置する必要があります。同一チップに対して2つの設計(従来のパッケージ設計とCSPの設計)を行わないようにするために、通常は、再配線層で、バンプをボンディングパッドに接合する必要があります。

フリップチップ/UCSPの入手性と鉛フリーの準拠性の確認

ごく一部のMaxim/Dallas Semiconductorのデバイスが、フリップチップまたはUCSP製品として提供されています。パッケージの入手性を確認する最も簡単な方法は、Maximのウェブサイトにあるデバイスのクイックビュー機能です。型番検索を行なうと、クイックビューデータシートが表示されます。ここには、デバイスの簡単な説明、主な特長、パッケージのオプション、アプリケーションノートのURL、その他の情報へのリンク(信頼性レポートや評価キットなど)が表示されます。クイックビューの右上で、型番テーブルにアクセスすることができます。データシートに複数の型番がある場合、型番テーブルには、特定の型番を選択することができるドロップダウンボックスが表示されます。[Go]をクリックすると、型番、パッケージ説明、パッケージの図面のURL、温度範囲および鉛フリーパッケージかどうかが表示されたウィンドウが開きます。FCHIPまたはUCSPを検索してください。Dallas Semiconductor製品のフリップチップ/UCSPパッケージ識別子は、「X」です。MaximのUCSPは、一般的に、型番の数字部分に続くサフィックスに「B」が付きます。12型番テーブルからアクセス可能なパッケージの図面には、必ず配置情報が含まれています。UCSPの図面は、一般的に、チップサイズがわずかに異なる複数のデバイスに利用されるため、バンプの電気的な配置は含まれていません。この情報は、デバイスのデータシートから参照することができます。フリップチップの図面は特定のチップにしか利用されないため、通常、電気的な配置が含まれています。

フリップチップ/UCSPのトップマーク(デバイスの識別)

ほとんどのフリップチップおよびUCSPには、プラスチックパッケージでは一般的な従来からのマーキングを行なうスペースがありません。最小のUCSP (4バンプ)には、配置マークと2行にわたる6文字のコードを表記するだけのスペースがあります。配置マークからは、パッケージが「準拠製品」(共晶バンプ)、高Pb (#)、またはPbフリー(+)かどうかもわかります。図4を見てください。

図4. フリップチップおよびUCSPのマーキングテンプレート

UCSPのトップマークコードについては、通常、クイックビューのその他の情報から簡単にアクセスすることができます。データシートに情報が記載されている場合もあります。トップマークからデバイスのパッケージを確認するなど、逆引き検索する場合は、ウェブベースのトップマークコード機能を使用するか、トップマークの全リスト13をダウンロードしてから検索機能を使用して、該当のデバイスを確認してください。トップマークコードは、12バンプまでのUCSPに使用されています。大型のUCSPには、型番のすべてと日付コードとロット情報を刻印するだけのスペースがあります。表2は、Maxim製品に使用される刻印です。

| Maxim Brand | Legend | ||

| 2-lines | mmm nxx |

||

| 3-lines | mmm nxx YWW |

||

| 4-lines | pppp sss nxx YWW |

mmm pppp sss |

Topmark code Part number (numeric portion only) Part number suffix |

| 4-lines, alternate | pppp sss n YWW xxxxx |

n xx YWW If branded, "MAX" is in the same line as the A1 marker. |

Production-related code, letters Date code |

| 5-lines | MAX pppp sss n YWW |

||

Dallas SemiconductorのフリップチップおよびUCSPに使用されている刻印の形式を表3に示します。レーザ刻印は非常に小さいため、読むには拡大鏡が必要です。Dallas Semiconductorのフリップチップでは、最小のデバイスと同じ方法を使用しています。すなわち、2桁のデバイスコード(ファミリコードとも言う)が、ダイの改訂コードの後に刻印されます。この方法では、クロスリファレンスのリストは必要ありません。

| Maxim Brand | Legend | ||

| 1-line | dcrrδ | dc | 2-digit device (family) code |

| 2-lines | DSpppp rrδ#xx |

pppp YYWW |

Part number (numeric portion only) Date code |

| 3-lines | DSppppp yywwrr ###xx |

δ rr ###xx |

Alternate date code Die revision code Production-related code |

ウェハレベルでパッケージ化された製品の信頼性

ウェハレベルパッケージ(フリップチップおよびUCSP)は、独自のパッケージフォームファクタを備えています。このため、従来の機械的な信頼性テストでは、パッケージ製品と同等の性能を発揮しない可能性があります。パッケージの信頼性は、実装方法、回路基板の材料、および使用環境と密接に関係しています。WLP製品の使用を考慮する際は、これらの点を綿密に検討する必要があります。動作寿命テストの性能と耐湿性は、主にウェハの製造工程で決まるため、影響を受けません。

WLPには、機械的な応力性能に対する十分な考慮が必要です。フリップチップとUCSPは、PCBに直接半田付けされるため、パッケージ製品のリードフレームに固有の応力緩和がありません。このため、半田接合部の完全性を考慮する必要があります。基板のレイアウト、実装工程フロー、半田ペーストスクリーン印刷、部品の配置、リフローの温度プロファイル要件、エポキシ封止、および目視検査の受入れ基準については、Dallas Semiconductorのウェハレベルパッケージの実装ガイド14を参照してください。Maximの推奨設計とテストデータの詳細については、アプリケーションノート189115を参照してください。信頼性情報は製品クイックビューの「技術資料」のタブからアクセスできます。フリップチップ、UCSP、またはWLPバージョンの情報が見つからない場合は、 サポートセンター(英語のみの対応)を利用してレポートをご請求ください。

結論

今日のフリップチップおよびCSPは、開発が続く新しい技術です。裏面ラミネートコーティング(BSL)はすでに改良が進んでいます。これによって、チップの動作しない側を光と機械的な衝撃から保護し、明視野でのレーザ刻印の信頼性が向上します。BSLとともに、全体的な実装の高さが変わらないようにするためのダイの薄型化が期待されています。MaximのUCSPの寸法(表1を参照してください)は、2007年2月のパッケージ状態です。業界の全体的な傾向に合わせて、寸法の小型化が進むと思われます。このため、設計者は、各パッケージ図面で実際のパッケージ寸法を確認してから、回路基板のレイアウトを完了させる必要があります。さらに、デバイスがPbフリーと宣伝されておらず、刻印がない場合には特に、バンプダイWLPの合金組成を確認することが重要です。一部の高Pbのバンプ(Pb95Sn5)は、Pbフリー基板の実装リフロー工程でテストされているため、互換性があって信頼性に重大な影響を与えません。16、17共晶のSnPbバンプが使用されているデバイスには、同種の共晶SnPb半田ペーストが必要です。そのため、Pbフリーの実装環境との互換性はありません。

この記事に関して

製品

1-Wireデュアルポートリンク

1-Wire ECDSAセキュア認証用IC

1-WireセキュアSHA-3認証用IC

デュアルNVポテンショメータおよびメモリ

不揮発性トリマポテンショメータ

1-Wire EEPROM

1Kbアドオンリーメモリ

1024ビット、1-Wire EEPROM

シリコンシリアルナンバー

警報付き、高精度Li+ (リチウムイオン)バッテリモニタ

スリープモード付き、シングルチャネル1-Wire®マスター

シングルチャネル1-Wireマスター

DeepCoverセキュア認証用IC、1-Wire SHA-256および512ビットユーザーEEPROM内蔵

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}