全ての重要な仕様でバイポーラ・アンプに挑む高速CMOSオペアンプ

はじめに

LTC6241デュアルCMOSオペアンプおよびLTC6242クアッドCMOSオペアンプは、優れた低入力バイアス電流および低ノイズ電流を維持すると同時に、ノイズ、スピード、オフセット電圧、オフセット・ドリフトにおいてバイポーラ・オペアンプに堂々と匹敵する性能を持っています。こうしたアンプ・パラメータの非常に大きな進展により、これまでのCMOSオペアンプに比べ、システム仕様の厳格化、複雑性の軽減、電源電圧動作範囲の拡張が可能になっています。入力バイアス電流が極めて低いこれらのオペアンプは、精度を要する様々なアプリケーションにも適していますが、フォトダイオードのトランスインピーダンス・アンプ(TIA)などの高インピーダンス変換器アプリケーション向けに最適化されています。

LTC6241およびLTC6242は、オフセット電圧を低減する複雑なポストパッケージ・スキームを使用していませんが、それでも、125µVのオフセット電圧および2.5µV/ºCのオフセット・ドリフトは、手に入るCMOSアンプとしては最高水準にあります。それに加えて、普通のアンプと一線を画しているのは、18MHzのゲイン帯域幅と非常に低いノイズ電流です。3Vと5Vには十分に対応しており、HV版では±5.5Vまでの動作を確保しています。消費電源電流は、最大で2.2mA/アンプです。表1に、これらのオペアンプの控えめに定めた仕様をまとめました。

| パラメータ | 条件 | 最小値 | 代表値 | 最大値 | 単位 | |

| オフセット電圧 | VCM = 0 S8, LTC6241 GN16, LTC6242 DD, DHC, LTC6241/42 |

40 50 100 |

125 150 550 |

µV µV µV |

||

| TC VOS | ● | 0.6 | 2.5 | µV/°C | ||

| 入力バイアス電流 | ● |

1 10 |

75 |

pA pA |

||

| ノイズ電圧 | f = 1kHz f = 0.1Hz to 10Hz |

7 550 |

10 | nV/√Hz nVP–P |

||

| ノイズ電流 | f = 100kHz | 110 | fA/√Hz | |||

| 入力容量 | f = 100kHz CDM CCM |

0.5 3 |

pF pF |

|||

| 大信号ゲイン | RL = 1kΩ to VS/2 | 90 | 215 | V/mV | ||

| CMRR | VCM = –V to +V – 1.5V | ● | 80 | 105 | dB | |

| 動作電源電圧範囲 | LTC6241/42 LTV6241HV/42HV |

● ● |

2.8 2.8 |

6 11 |

V V |

|

| VOUT Low | ISINK = 5mA | ● | 190 | 325 | mV | |

| VOUT High | ISOURCE = 5mA | ● | 4.81 | 4.675 | V | |

| 電源電流 | per amplifier | ● | 1.8 | 2.2 | mA | |

| スルー・レート | AV = –2, RL = 1kΩ, | ● | 5 | 10 | V/µs | |

| ゲイン帯域幅積 | RL = 1kΩ | ● | 13 | 18 |

LTC6241は、SO8パッケージで供給される他、コンパクト設計向けに小型のデュアル・ファイン・ピッチ・リードレス(DFN)パッケージも用意しています。LTC6242は、16ピンSSOPパッケージおよび5mm × 3mmのDFNパッケージで供給されます。

1/fノイズが低いCMOS?ノイズ電流はどうなのか?

CMOSオペアンプにはこれまで、バイポーラ・アンプよりも1/fノイズが非常に高いという欠点がありました。CMOSアンプの1/fコーナーが数キロヘルツを超えることは普通ですが、LTC6241は最高水準のバイポーラ・オペアンプに匹敵するほどで、1/fノイズのコーナーはわずか40Hzです。このノイズは0.1Hz~10Hzの帯域幅でわずか550nVP–Pと非常に低く、これは、オートゼロ方式を使用していないCMOSオペアンプで得られる最も低い1/fノイズとなっています。

フォトダイオード・アンプなどの電流電圧変換アプリケーションでは、アンプが反転動作を行い、ノイズ電流が高周波で支配的になります。CMOSオペアンプのノイズ電流源は2つあります。1つ目は、ゲート・ソース間とゲート・ドレイン間の容量を介して結合する、入力デバイスのチャンネル熱ノイズです。2つ目のノイズ電流は、オペアンプの入力容量と、入力変換器に関連した容量から生じます。この入力換算ノイズ電流(CVノイズ)は、アンプのノイズ電圧VNが全入力容量CTに印加されることで生じ、2πfCTVNの大きさの電流が帰還抵抗を通って流れることになります。

CMOSまたはバイポーラの低ノイズアンプを作るには、大きな入力トランジスタを用いる方法があります。その場合の問題は、大きい入力構造のために、高い入力容量が負担になることです。入力容量が高いと、高周波ノイズ電流が増加すると共に、オペアンプ全体のスピードが低下します。LTC6241の際立った特徴には、わずか0.5pFという低い差動入力容量があり、これが電流電圧変換アンプの設計では大きなメリットになります。この入力容量は、他のCMOSアンプと比べると1/8~1/10という低さです。

シンプルな構造で低ノイズとDC精度を実現

図1はLTC6241の半分を簡略化した回路図で、一対の低ノイズ入力トランジスタ(M1とM2)を備えています。シンプルな折り返しカスコード(Q1、Q2およびR1、R2)により、入力段は、負レールにスイングし、差動ドライブ・ジェネレータにレベル・シフトすることができます。トランジスタM1とM2および電流源I1とI2は、低ノイズ向けに最適化されており、ダイ面積の30%以上を使っています。低オフセットは、レーザ・トリミング抵抗RT1とRT2で実現されています。パッケージ・アセンブリで生じる応力がこのシンプルで安定した構造に及ぼす影響はわずかであるため、オフセット電圧とドリフトを調整する複雑なポストパッケージ・トリム・スキームは不要です。

図1. 簡略化した回路図。

LTC6241およびLTC6242は、ノイズ仕様を損なわないように、意図的にレールtoレール入力段を使わずに設計されました。多くのCMOSレールtoレール入力アンプでは、オフセット・シフトが大きく、この上側の遷移領域でコモン・モード電圧が動作しているときにノイズが高くなり、その有用性が制限されます。

LTC6241およびLTC6242の全ての入出力には、図1に示すように、逆バイアスされたESD保護ダイオードが備わっています。これらのダイオードは、1.7kVまでESD破壊からアンプを保護します。DCベースでは電流がゲートに流れ込むことはありませんが、これらのESD保護ダイオードは、データシートに仕様化されている入力バイアス電流のソースです。これらのダイオードのリーク電流は、およそ7ºCごとに2倍になりますが、入力電流は通常、周辺温度85ºCまで10pA未満にとどまっています。

コンデンサC1は、ユニティ・クロス周波数を下げて、アンプのゲイン帯域幅を悪化させることなく周波数安定性を改善します。コンデンサCMは、アンプ全体のゲイン帯域幅を決めます。差動ドライブ・ジェネレータは、レールtoレールから出力をスイングさせるトランジスタM3とM4に信号を供給します。

図2に、オフセット電圧とオフセット電圧ドリフトの分布を示します。図3に、入力バイアス電流とコモン・モード電圧の関係、ノイズ電圧とノイズ電流の周波数特性を示します。

図2. VOSの分布とVOS温度係数の分布。

図3. 入力バイアス電流とコモン・モード電圧の関係、ノイズ電圧およびノイズ電流と周波数の関係。

アプリケーション

非反転積分器

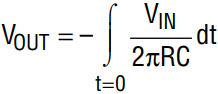

積分器は、帰還制御システムおよびフィルタに広く使われています。LTC6241のようなCMOS入力アンプは、低入力バイアス電流によって、所定の積分時定数に対して大きい値の抵抗と小容量のコンデンサが使用できるため、この機能に適しています。最も一般的な形の積分器は、図4に示す反転型です。これは、以下の伝達関数を持ちます。

図4. 典型的な反転型の積分器。

図4の回路を用いた帰還制御ループで反転が必要ない場合、設計者は別のオペアンプを追加して再度反転させる必要があります。よりシンプルな全体的ソリューションとして、1つのオペアンプを用いるだけで非反転積分器を作ることができます。図5にその回路を示します。

図5. 非反転積分器は非常にシンプルにすることができます。理想的にはR1 • C1 = R2 • C2ですが、ミスマッチは必ず起きます。ミスマッチによる位相上昇を避けるためには、R1 • C1 < R2 • C2となるように、時定数をずらすことが有効です。

低周波数では、R1 • C1は減衰せず、非反転積分機能は、オペアンプのゲインおよびその帰還部の部品C2とR2で提供されます。周波数が高くなると、C2は短絡回路になるので、オペアンプのゲインが1になり、積分機能はR1とC1で提供されます。時定数がマッチングしている場合、積分器の適合性は良好です。しかし、マッチングを取るのは、容易ではありません。ほとんどのループでは、積分器の位相が90度を超えないことを確保するために、R1 • C1 < R2 • C2となるよう、時定数を意図的にずらすことが可能です。非反転積分器の具体的なクローズド・ループの使用例については、LTCデザイン・ノートDN254を参照してください。

圧電型加速度センサー:

反転型と非反転型の比較

図6および図7に、LTC6241を用いて容量性センサーからの信号を増幅する2種類の手法を示します。どちらの場合もセンサーは、770pFの圧電型衝撃センサーを用いた加速度センサーで、物理的な加速を受けると電荷を発生させます。図6に、標準的な「チャージ・アンプ」のアプローチを示します。このオペアンプは反転構成になっているため、センサーは仮想グラウンドを調べます。センサーで生成された電荷は全て、オペアンプの動作によって帰還コンデンサに運ばれます。帰還コンデンサはセンサー容量の1/100と小さいため、出力は、センサーのオープン・サーキット電圧の100倍の電圧に設定されます。したがって、回路のゲインは100です。

図6. 標準的な反転チャージ・アンプ。ケーブル容量(すなわち長さ)の変動は信号ゲインに影響を与えません。加速度センサーがアンプから離れた場所にあって、ケーブル長が分からない場合にこの回路を用います。問題は、小さい値の帰還コンデンサによってゲインが決まり、帰還コンデンサに付加するバイアス抵抗によって低周波性能が決まることです。

この手法の利点は、回路の信号ゲインがセンサーとアンプの間に挿入されるケーブル容量には依存しないため、ケーブル長が異なる可能性のある遠方の加速度センサーに適したソリューションになることです。この回路の難点は、小容量のコンデンサを用いたゲイン設定の不正確さと、小容量の帰還コンデンサに付加するバイアス抵抗による低周波カットオフです。

図7に、非反転アンプの手法を示します。これには多くの利点があります。第1に、ゲインは小容量のコンデンサではなく抵抗で正確に決まります。第2に、低周波カットオフは、小容量の帰還コンデンサではなく、770pFと大容量のセンサーに付加するバイアス抵抗で決まり、より低い周波数応答が得られます。第3に、非反転トポロジは、電圧ノイズをスケーラブルに低減させるために、(図示されているように)並列接続して合算することが可能です。この回路の唯一の欠点は、入力の寄生容量によってゲインがわずかに低下することです。この回路は、パターンやケーブルなどの寄生入力容量が比較的小さくて変化しない場合に有利になります。

図7. 非反転チャージ・アンプにはいくつかの利点があります。各段は、電圧ノイズをより低くするために並列接続が可能です。バイアス抵抗を付加するコンデンサの容量が高いほど、低周波応答が良くなります。

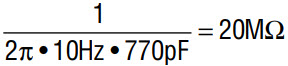

バイアス抵抗を、帯域幅計算から求まる値よりも大きくすることを考えてみます。これにより、低周波でのノイズ・フロアが実際に低下します。例えば、–3dBで10Hzという低い周波数をサポートするには、バイアス抵抗を次のように計算します。

10Hzにおいて、20Mの抵抗であればノイズは580nV/√Hzとなり、信号と同様に3dB低下します。図示されているように抵抗を1GΩにすると、4000nV/√Hzの電圧ノイズが加速度センサーの容量により減衰して実質的に80nV/√Hzまで低下しますが、一方で信号はほとんど減衰しません。これは、S/N比において少なくとも7倍の改善です。

大面積フォトダイオード・アンプ

図8に、トランスインピーダンス・アンプとして大容量大面積フォトダイオードに用いられるLTC6241を示します。この回路はDCでユニティ・ノイズ・ゲインを持つため、分解能は完全にノイズで制限されます。フォトダイオードのインピーダンスは周波数と共に低下し、実効ゲイン(ノイズ・ゲイン)を引き上げるため、帯域幅はロールし、これをオペアンプが調べます。これにより、帯域幅が大幅に制限され、出力ノイズが増加します。この回路の–3dB帯域幅は25kHzと測定され、10kHzでの出力ノイズ密度は1.6µV/√Hzと測定されました。この結果は、多くのアプリケーションにとって十分かと思われます。まだ十分でない場合には、読み進めてください。

図8. 大面積フォトダイオード・アンプでは約25kHzの帯域幅が得られます。DCは良好ですが、出力にはノイズが混ざっています。

先ほどの回路の主な問題は、フォトダイオードの容量が大きいことです。最善の策は、その容量を低ノイズJFETでブートストラップすることです。図9にその回路を示します。低ノイズJFETのソース・フォロワでは、4.99kの抵抗を通って約1mAが流れ、ソースはグラウンドより約0.6V高くなっています。これで、フォトダイオード容量を通って入る実効入力電圧ノイズは、オペアンプの8nV/√Hzではなく、JFETの1nV/√Hzになります。オペアンプは、それ自体が持つ3pFの入力容量、更に2pFのゲート・ドレイン間容量と寄生容量を調べることになります。これは3000pFを調べるよりもはるかに良い状況です!

図9. シンプルなブートストラップ回路によって、DCを良好に保ったまま、ACを大幅に改善します。そのため、出力ノイズは10kHzで221nV/√Hzになり、帯域幅は220kHzです。立上がり時間は、3000pFのフォトダイオードから1MΩのゲインで1.58µsです!

このシンプルな改良の効果は絶大です。補償コンデンサCFの容量を低減でき、帯域幅は220kHz(立上がり時間1.58µs)に改善されます。図10に示すように、10kHzでの出力ノイズ密度は、221nV/√Hzに低下します。DC性能は、JFETが関与しないため良好なままであり、JFETはフォトダイオードにわずかな逆バイスを与えるだけです。

図10. 図9に示すブートストラップ回路の出力ノイズ・スペクトル密度。

まとめ

LTC6241およびLTC6242は、最高のバイポーラ・オペアンプが持つ低ノイズ、低オフセット、低ドリフト性能と、CMOSオペアンプが持つ低入力バイアス電流および低ノイズ電流という特長を兼ね備えています。これらのアンプは、2.7Vから±5.5Vで動作し、高速かつ低ノイズの信号処理向けのオールインワン・ソリューションを提供します。

著者について

この記事に関して

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}