要約

マキシムのシリアライザは、カメラICを接続して制御することができます。このアプリケーションノートでは、カメラのRAW RGBやYUVの出力を標準的なディスプレイでの使用に適したRGBデータに変換する方法を説明します。

はじめに

マキシムのシリアライザは、カメラICを接続して制御することができます。ハーフデュプレックスのUART/I²C制御チャネルを備えたMAX9257や、フルデュプレックスの同時制御チャネルを備えたMAX9259やMAX9263などがそうしたデバイスに相当します。MAX9263は、広帯域幅のデジタルコンテンツ保護(HDCP)にも対応しています。このアプリケーションノートでは、カメラのRAW RGBやYUVの出力を標準的なディスプレイでの使用に適したRGBデータに変換する方法を説明します。

カメラの出力フォーマット

OmniVision® OV10630などのカメラチップは、シリアライザを介して接続することができます。OV10630のインタフェースピンは、ピクセルクロックのPCLK、Line ValidのHREF、フレーム同期のVSYNC、およびパラレルデータビットのD[9:0]です。データビットはクロックの立上りで安定しています。

YUVおよびRAW RGBフォーマットの説明

CMOSカメラセンサーは、数百万個の感光セルで構成されています。各セルはそれ自体であらゆる波長の光に反応します。特定のセンサーを赤、緑、または青の波長の光にのみ反応させるには、光学フィルタのコーティングを利用します。隣り合ったセルは通常ベイヤー配列でカラーコーティングされます。この配列では、緑にコーティングされるセルの数が赤や青の2倍になります。これは人間の眼の生理機能に合わせた結果です。センサーセルの出力を左から右、および上から下に取ると、RAW RGBデータは、図1に示すように、青、緑、...、青、緑(第1ラインの終端)、緑、赤、...、緑、赤(第2ラインの終端)といった形に配列されます。

図1. RAW RGBデータのバイトシーケンス

隣り合ったセルから目的の色を補間することによって、センサーセルと同じ密度を持つRGBデータを生成することができます。あるいは、一定の規則に従い、隣り合ったセルの色を使用してこれを実現することも可能です。ピクセル位置ごとに設定されたRGBを構成するためのそうした規則の1つは、同一ライン上の隣り合ったセルのペアと、緑の隣にある次(または前)のラインのセルを使用することです。補間したRGBデータは、図2に示すように、...、赤(i-1)、緑(i-1)、青(i-1)、赤(i)、緑(i)、青(i)、赤(i+1)、緑(i+1)、青(i+1)、...といった形に配列されます。カメラセンサーの分解能を最大限に維持しつつカラーディスプレイを駆動するには、ピクセルごとにRGBデータのセットが必要です。そのような補間したRGBデータの輝度分解能はセンサーセルの分解能に近くなりますが、クロミナンス分解能では劣ります。人間の眼はピクセルの色成分よりも各ピクセルの強度に敏感であるため、知覚される分解能はセンサーセルの分解能と同程度になると考えられます。

図2. RGBデータのバイトシーケンス

しかし、そのような補間したRGBデータのデータレートは3倍になります。特に伝送用のデータレートを低減するには、(アナログカラーTV信号をアナログ白黒TVの周波数帯域に収める) YUVの色空間を利用することができます。次の式では、輝度がYで表され、青と輝度の間の色差がUであり、赤と輝度の間の色差がVです。

ここで、標準のカラーウェイティング値がWR = 0.299、WB = 0.114、WG = 1 - WR - WB = 0.587で、正規化値がUMAXであり、VMAX = 0.615です。

ベイヤー配列色のフィルタを備えたカメラセンサーでは、ラインインデックスiとピクセルインデックスjに応じて、隣り合ったピクセルのUまたはVのどちらかのデータがほぼ同じになります(隣り合った色を使用する規則を利用している場合)。このガイドラインを使用して、次の式に基づき、YUVデータをRAW RGBデータから直接生成することができます。

ラインインデックスiとピクセルインデックスjが偶数の場合。

ラインインデックスiとピクセルインデックスjが偶数の場合。

ラインインデックスiが偶数でピクセルインデックスjが奇数の場合。

ラインインデックスiが偶数でピクセルインデックスjが奇数の場合。

ラインインデックスiが奇数でピクセルインデックスjが偶数の場合。

ラインインデックスiが奇数でピクセルインデックスjが偶数の場合。

ラインインデックスiとピクセルインデックスjが奇数の場合。

ラインインデックスiとピクセルインデックスjが奇数の場合。

ラインインデックスiとピクセルインデックスjが偶数の場合。

ラインインデックスiとピクセルインデックスjが偶数の場合。

ラインインデックスiが偶数でピクセルインデックスjが奇数の場合。

ラインインデックスiが偶数でピクセルインデックスjが奇数の場合。

ラインインデックスiが奇数でピクセルインデックスjが偶数の場合。j.

ラインインデックスiが奇数でピクセルインデックスjが偶数の場合。j.

ラインインデックスiとピクセルインデックスjが奇数の場合。

ラインインデックスiとピクセルインデックスjが奇数の場合。

ラインインデックスiとピクセルインデックスjが偶数の場合。

ラインインデックスiとピクセルインデックスjが偶数の場合。

ラインインデックスiが偶数でピクセルインデックスjが奇数の場合。

ラインインデックスiが偶数でピクセルインデックスjが奇数の場合。

ラインインデックスiが奇数でピクセルインデックスjが偶数の場合。

ラインインデックスiが奇数でピクセルインデックスjが偶数の場合。

ラインインデックスiとピクセルインデックスjが奇数の場合。

ラインインデックスiとピクセルインデックスjが奇数の場合。

データレートを低減するには、偶数ピクセルインデックスのUデータと奇数ピクセルインデックスのVデータを、偶数と奇数の両方のピクセルインデックスのYデータとともに使用します。そのようなデータレートを低減したYUVデータが、図3に示すように順次伝送されます。つまり、Y1、U0、V1がピクセル1のデータであり、Y2、U2、V1がピクセル2のデータであり、以下同様です。

図3. YUV422データのバイトシーケンス

422は、Y:U:Vのサンプル比を示しています。最初期のカラーNTSC規格では、映像信号の色の分解能が輝度の分解能の4分の1しかない4:1:1のクロマサブサンプリングを使用していたため、4:x:xの規格が採用されました。現在、輝度と色の両方の情報について分解能が同じである4:4:4のクロマサブサンプリングを使用しているのは、圧縮されていない信号を処理するハイエンド機器だけです。

シリアライザの入力フォーマット

マキシムのシリアライザのパラレルインタフェースは、24ビットRGBデータ用に設計されています。とりわけMAX9259は、1つのピクセルクロックビット(PCLK)と29のデータビットを持ち、24ビットのRGBと水平同期、垂直同期、3つの制御ビットに使用可能です。データパラレルインタフェースに加えて、DRSピンとBWSピンを、それぞれデータレートとバス幅の選択のためにハイまたはローに設定する必要があります。

マキシムのシリアライザ/デシリアライザ

MAX9257とMAX9258のシリアライザ/デシリアライザ(サーデス)ペアは、YUVデータの伝送に適した最大18のパラレル入力/出力ビットを備えています。一方、MAX9259/MAX9260チップセットは、RGBデータの伝送に適した28のパラレル入力/出力ビットを備えています。別のサーデスペアであるMAX9263/MAX9264は28ビットを備え、HDCP機能が追加されています。さらに、MAX9265とMAX9268は、パラレル入力/出力インタフェースの代わりにカメラリンクを備えた、28ビットのサーデスペアです。マキシムの28ビットシリアライザとデシリアライザは、いずれもパラレル-シリアルのデータマッピングが同じであり、互いに区別なく使用可能です。たとえば、RGBデータを(FPGAの助けを借りて)送信する場合、MAX9259シリアライザとMAX9268デシリアライザを組み合わせて使用することができます。このデータは、CMOSカメラからシリアルリンクでカメラリンクインタフェース付きのディスプレイデバイスに送信されます。

シリアライザのマッピング

MAX9268デシリアライザのカメラリンク出力インタフェースをマッチさせるには、以下の信号図に基づいてパラレルRGBビットをマッピングする必要があります。図4は、MAX9268の中間パラレルビットとカメラリンク出力とのマッピングを示しています。図5は、カメラリンクのRGBコンテンツのビットマッピングを示しています。表1は、MAX9259シリアライザについて、対応するコンテンツのマッピングを示しています。

図4. MAX9268の内部パラレル-出力マッピング

図5. カメラリンクのコンテンツのマッピング

| DIN0 | DIN1 | DIN2 | DIN3 | DIN4 | DIN5 | DIN6 | DIN7 | DIN8 | DIN9 |

| R0 | R1 | R2 | R3 | R4 | R5 | G0 | G1 | G2 | G3 |

| DIN10 | DIN11 | DIN12 | DIN13 | DIN14 | DIN15 | DIN16 | DIN17 | DIN18 | DIN19 |

| G4 | G5 | B0 | B1 | B2 | B3 | B4 | B5 | HREF | VSYNC |

| DIN20 | DIN21 | DIN22 | DIN23 | DIN24 | DIN25 | DIN26 | DIN27 | DIN28 | |

| R6 | R7 | G6 | G7 | B6 | B7 |

色変換:YUVからRGB

FPGAチップでは、カメラからのデータレートを低減したYUVデータを、MAX9259シリアライザ用のRGBデータに変換可能です。この色空間変換の式は、8ビットの固定小数点演算で実装した場合、下記の計算式で記述することができます。nは、2つめと3つめの式のDnとEnについては偶数です。

Cn = Yn - 16

Dn = Dn + 1 = Un - 128

En = En + 1 = Vn + 1 - 128

Rn = clip((298 × Cn + 409 × En + 128) >> 8)

Gn = clip((298 × Cn - 100 × Dn - 208 × En + 128) >> 8)

Bn = clip((298 × Cn × 516 × Dn + 128) >> 8)

ここで、>> 8は「ビットを右に8回シフトする」という意味であり、clipは「最後の8ビットだけを取る」という意味です。

FPGAソリューション

入力バッファリング

入力バッファリング回路は、1つのカウンタ、3つのレジスタ、ある種の組み合わせロジックで構成され、シングルバイトクロック制御の入力を、入力クロックレートの半分でトリプルバイトクロック制御の出力に変換するために使用されます。組み合わせロジックは、Y、U、Vの各バイトの対応するレジスタをそれぞれイネーブルにするためにのみ使用されます。

図6. 入力バッファリング回路

クロックスイッチ

FPGAの出力ピクセルクロックは、カメラピクセルクロックレートの半分であり、シリアライザのピクセルクロック入力を駆動します。しかし、カメラは初期化が完了するまでピクセルクロックを出力しません。解決策は、2:1のクロックマルチプレクサ(mux)とクロック信号検出回路をFPGA内に実装することです。マルチプレクサは、クロック信号検出回路によって制御されます。マルチプレクサのパワーオンデフォルトクロック入力は、カメラのクロック発振器から取られます。これによってサーデスのチップセットがカメラ初期化用の制御チャネルを提供します。クロック信号検出回路では、垂直同期信号パルスをカウントします。数回の垂直同期パルスの後、マルチプレクサはカメラピクセルクロックのハーフレートに切り替えます。OV10630などの高分解能のカメラセンサーでは、1つの垂直同期パルスの各期間に含まれるピクセルクロックが10万回をはるかに超えます。数回の垂直同期パルスは、カメラの内部フェーズロックループ(PLL)を安定化させるのに十分な時間です。垂直同期のカウントは、ピクセルクロックのカウントよりもはるかに効率的であり、実装に必要なFPGAのロジック要素も節約することができます。

中間バッファリング

変換式では、ハードウェア回路の実装による遅延が記述されていません。RGBデータをYUV入力から生成するには、2~3回の乗算と3~4回の加算が必要です。FPGAのロジック要素(ゲート)では数ナノ秒の遅延しか生じませんが、キャリア、加算器、乗算器のシフト入力の伝播によって大きな遅延と遅延拡散が発生します。この遅延を最小限に抑えるため、各定数乗算器を、定数のうちゼロでない2つの最上位ビット(MSB)を表すシフト入力2つの加算器で近似します。それでも、約100MHzの入力YUVバイトレートでは、遅延拡散が隣り合ったピクセルのタイミング境界を越えることがあるため、映像にノイズが生じる結果になります。遅延拡散を解消するための中間レジスタが、すべての乗算器の後段に配置されます。

前述のYUVからRGBへの色空間変換は、Actel® ProASIC3 A3PN125Z FPGAデバイスに実装されています。図7は、このFPGA実装の回路図を示しています。

|

|

|

図7. FPGAによるYUV-RGB変換の実装

アプリケーション回路

カメラチップは、そのベンダーによってドータPCB上に実装可能です。図8は、カメラドータモジュールのファンクションブロックダイアグラムを示しています。入力は電源のPWRと水晶クロック(XCLK)です。出力信号は、パラレルデータビット(D0..D9)、I²Cバス(SDA、SCL)、ビデオ同期(HREF、VSYNC)、およびピクセルクロック(PCLK)です。

図8. カメラモジュールのファンクションブロックダイアグラム

図9は、FPGAとシリアライザのチップの回路図を示しています。これでアプリケーション回路は完成です。この回路は、2本のツイストペア線で構成されたシリアルケーブルで給電されます。そのうち1本はシリアル信号に使用され、もう1本が電源に使用されます。別のLDO電源ICがシリアライザとFPGAデバイスに使用されます。独自のLDO電源チップを持つカメラモジュールにバイパスコンデンサを使用して、干渉の可能性をさらに低減します。FPGAデバイスとシリアライザデバイス間のデータリンクには、ダンピング抵抗が使用されます。

図9a. アプリケーション回路のFPGA部分

図9b. アプリケーション回路のシリアライザ部分

MAX9259は、さらに小型のカメラヘッドを構成するために、OV10630などのカメラセンサーに直接接続することもできます。色空間変換用のFPGAをデシリアライザの後段に使用可能です。このアプリケーションではMAX9268によって直接駆動可能なカメラリンク出力が必要であるため、色空間変換用のFPGAはカメラセンサーとシリアライザ(MAX9259)の間に配置されます。

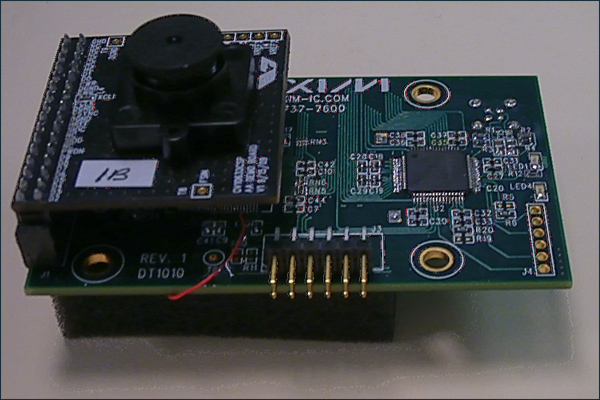

ビデオキャプチャの例

図10は、カメラアプリケーション回路の実装を示しています。これ自体、これらのカメラアプリケーション回路を使用してキャプチャしたものです。

図10. カメラアプリケーション回路の実装

まとめと将来の方向性

このアプリケーションノートでは、マキシムのカメラシリアライザICをFPGAと組み合わせて使用するための標準的な手法を説明しています。アプリケーションの回路図とFPGAコードは、設計リファレンスとしてそのままで利用可能です。このアプリケーションノートの将来の改訂版では、RAW RGBから24ビットRGBへのFPGAコンバータの実装を提供する予定です。

{{modalTitle}}

{{modalDescription}}

{{dropdownTitle}}

- {{defaultSelectedText}} {{#each projectNames}}

- {{name}} {{/each}} {{#if newProjectText}}

-

{{newProjectText}}

{{/if}}

{{newProjectTitle}}

{{projectNameErrorText}}