Overview

設計リソース

説明

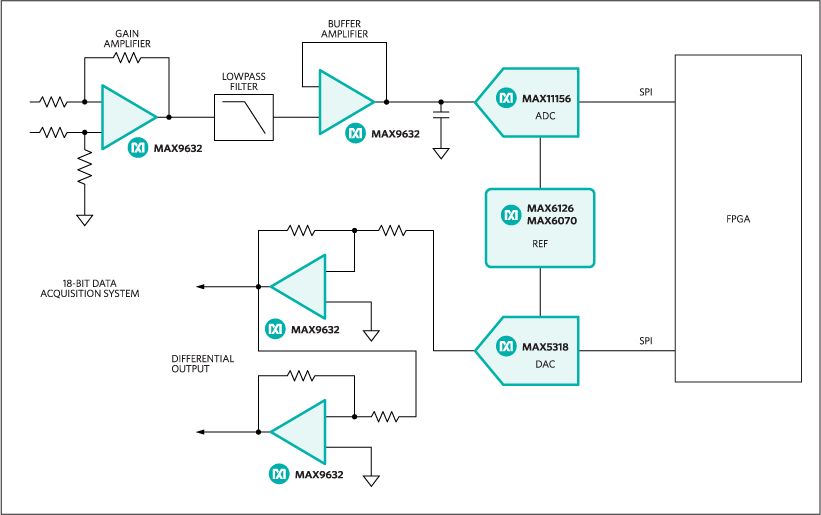

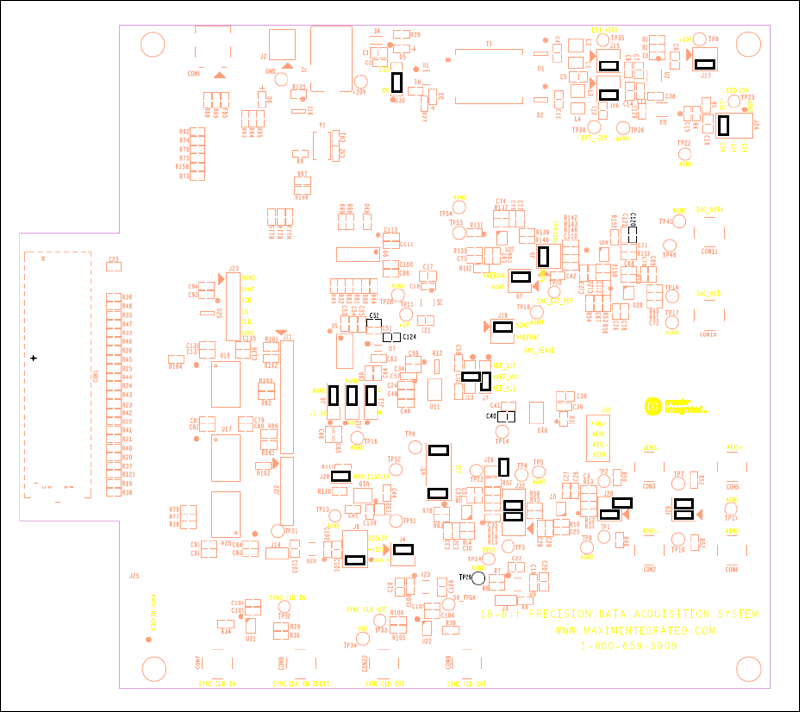

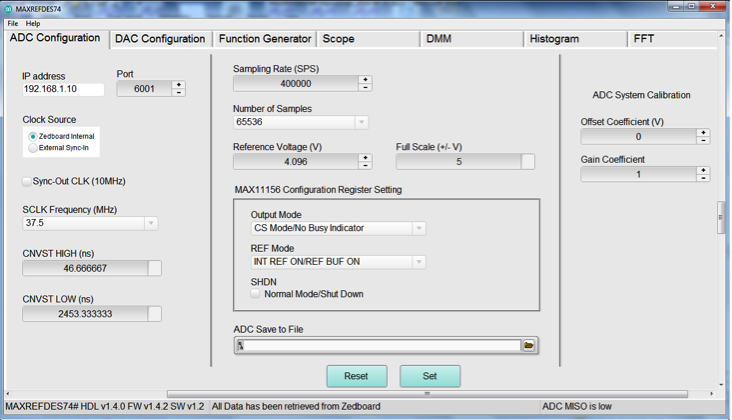

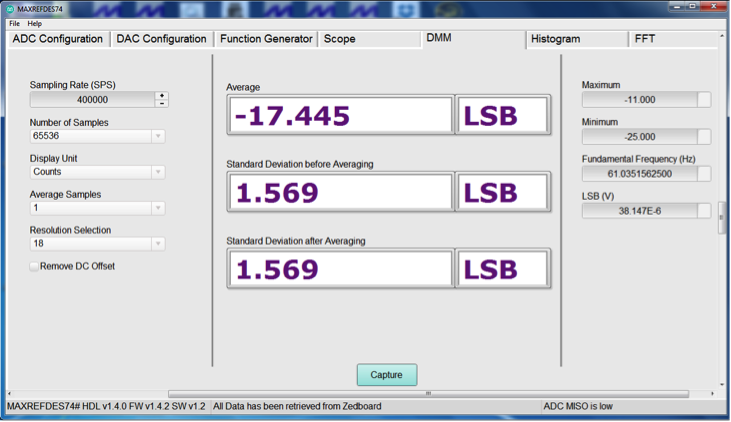

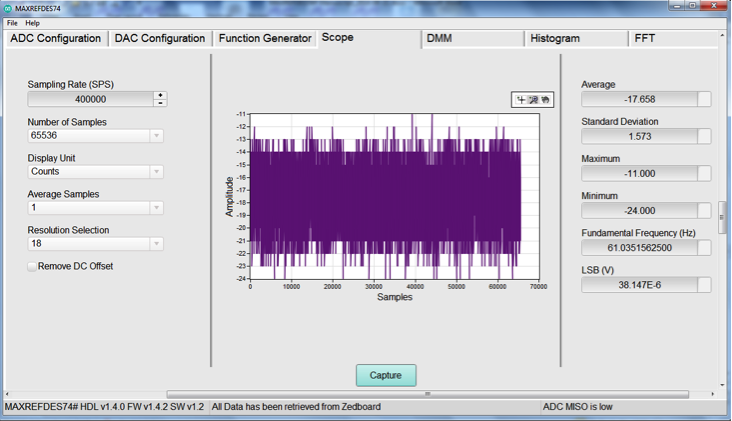

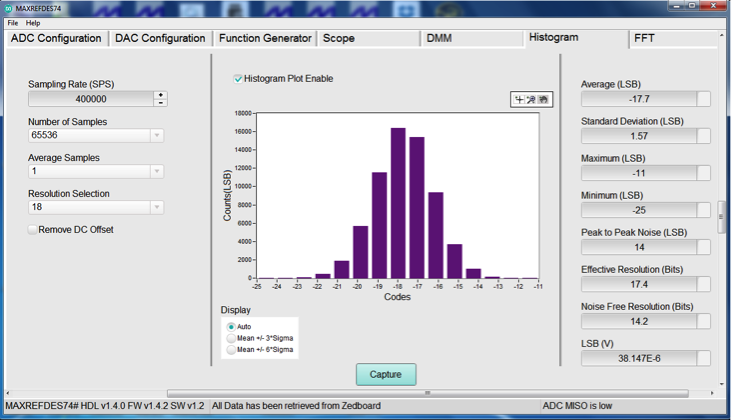

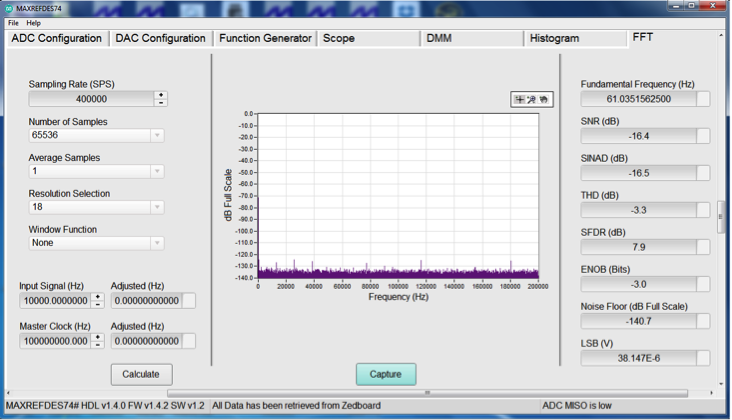

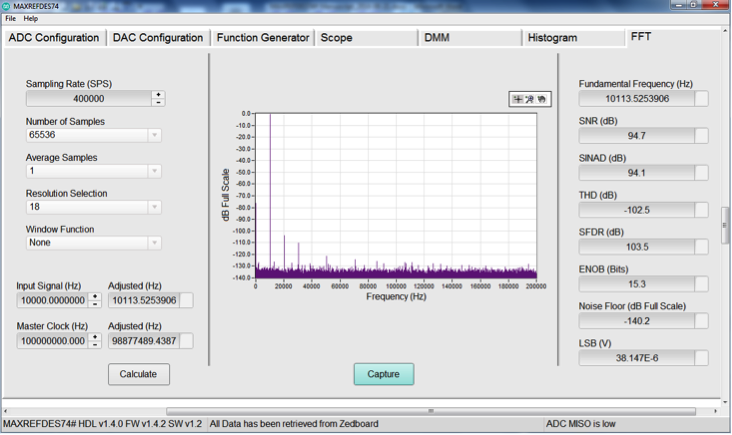

The MAXREFDES74# reference design performs high-speed, 18-bit, precision data acquisition based on Maxim’s leading-edge, high-accuracy, low-power data converters. The MAXREFDES74# design works as a building block for a high-speed, low-power, high-accuracy data acquisition and control system for industrial process control and automation, and high-speed protection systems for power distribution and automation. By changing the ADC and DAC to pin-compatible 16-bit devices such as the MAX11166 and the MAX5316, a 16-bit data acquisition system can also be tested.

機能と利点

The MAXREFDES74# reference design features:

- Power and data isolation

- Flexible, configurable inverting or noninverting input scheme

- Unipolar or bipolar input (ADC) and output (DAC)

MAX11156

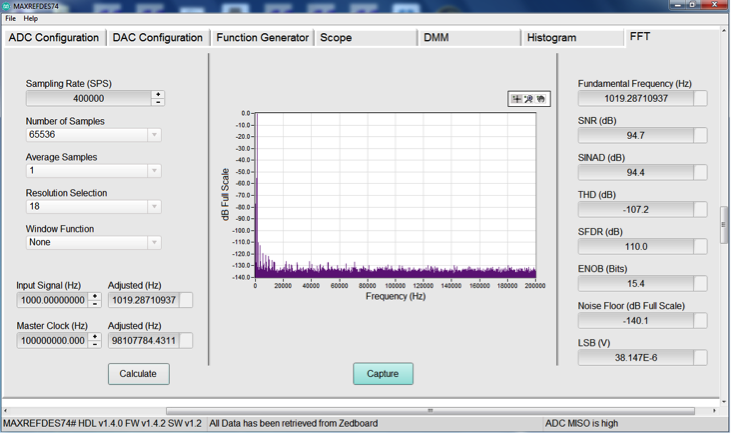

- 18-bit resolution with no missing codes

- SNR: 94.4dB

- THD: -107dB at 1kHz

- Buffered internal or external voltage reference input

- Internal reference with -6ppm/°C (typ) temperature coefficient

- Single 5V supply

- True bipolar ±5V input range

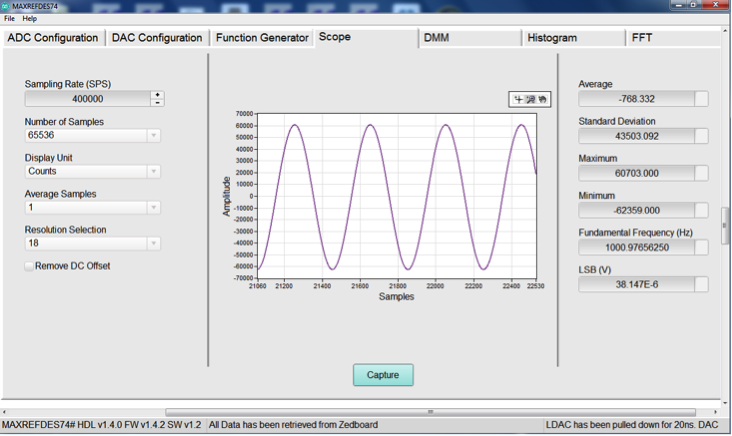

MAX5318

- 18-bit resolution with no missing codes

- High accuracy: ±2 LSB INL (max)

- 3µs settling time

- User-programmable offset and gain calibration

- ±0.5ppm/°C (typ) offset and gain drift over temperature

- Force/sense output

- 50MHz SPI-compatible interface with 1.8V to 5.5V logic

Details Section

ツールおよびシミュレーション

Documentation & Resources

-

MAXREFDES74 Design Files2021/03/03ZIP6 M

-

Bipolar Work Around for the MAXREFDES74#2016/12/19

Support & Training

Search our knowledge base for answers to your technical questions. Our dedicated team of Applications Engineers are also available to answer your technical questions.