Overview

設計リソース

評価用ボード

型番に"Z"が付いているものは、RoHS対応製品です。 本回路の評価には以下の評価用ボードが必要です。

- MAXREFDES44# ($26.20) Secure Authentication Design with 1-Wire ECDSA and Xilinx Zynq SoC

説明

Overview

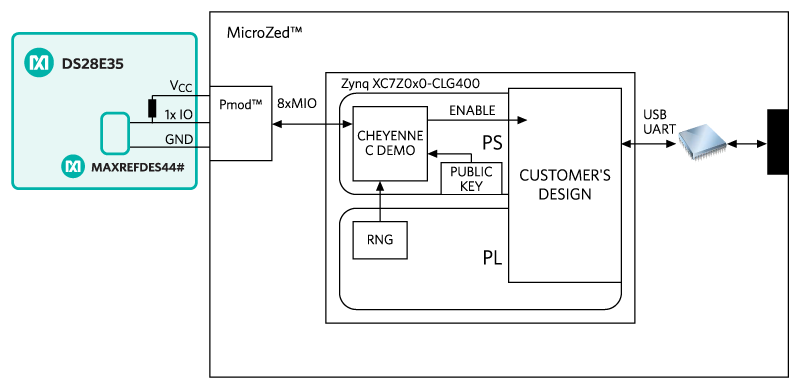

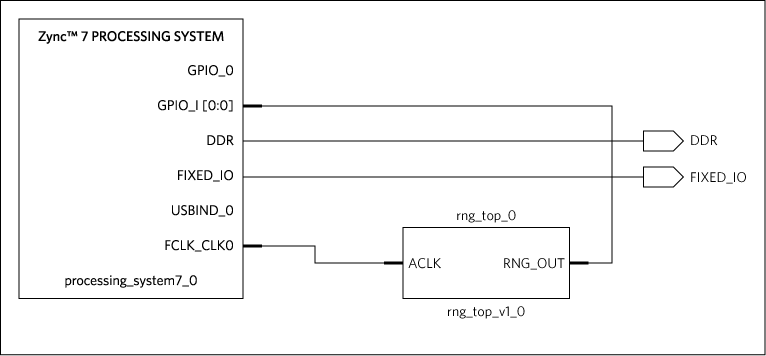

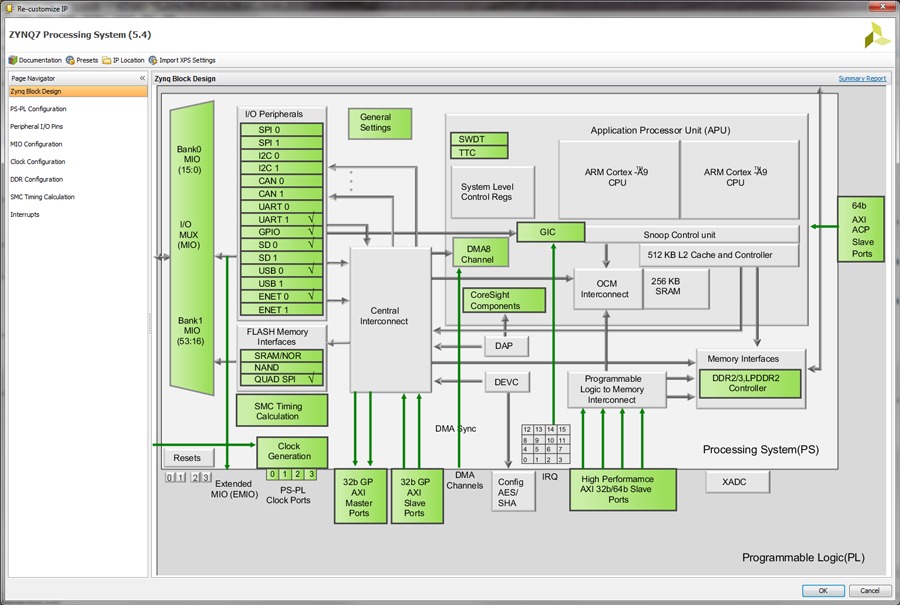

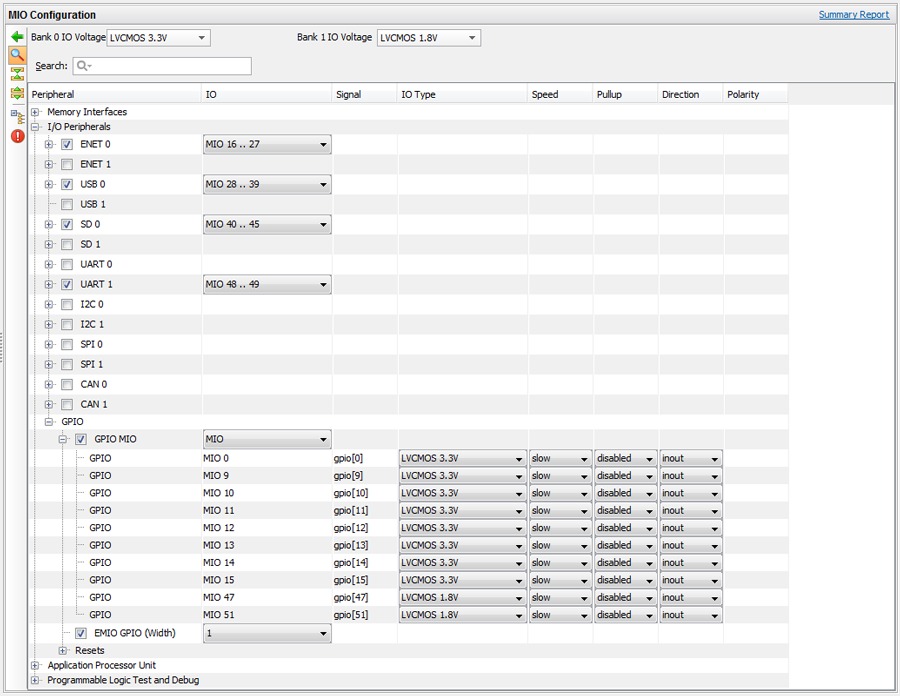

The MAXREFDES44# is a 1-Wire®-based authentication reference design, built to protect IP and authenticate peripherals to Xilinx Zynq™ FPGAs. Using the provided example code, the system executes an asymmetric challenge-response sequence with the DS28E35 to ensure the authenticity of a module, peripheral, or subsystem. The DS28E35 communicates on Maxim Integrated’s 1-Wire bus. The MAXREFDES44# is equipped with a Pmod™ connector for immediate testing using an Avnet MicroZed™ board. The simplicity of this design enables rapid adoption into any peripheral requiring the heightened security provided by the asymmetric ECDSA algorithm.

Refer to the Details tab for more information. Design files including schematic, PCB files, and bill of materials (BOM) can be downloaded from the Design Resources tab. Firmware is available upon request, following the execution of a nondisclosure agreement.

Note: Programming the MAXREFDES44# requires a separate purchase of the DS28E35EVKIT#.

機能と利点

Features

- ECDSA authentication

- 1-Wire interface

- Example source code

- Pmod-compatible form factor

Competitive Advantages

- Crypto-strong authentication

- Fast performance with hardware acceleration

- No VCC pin required for peripheral authentication

使用されている製品

Details Section

Documentation & Resources

-

MAXREFDES44 Design Files2021/02/17ZIP594K

Support & Training

Search our knowledge base for answers to your technical questions. Our dedicated team of Applications Engineers are also available to answer your technical questions.