T1/E1/J1トランシーバDS26518の送信パルス制御

要約

システムにネットワーク保護部品を追加する、および/または、コネクタを通して信号を送信する必要がある、相手側のPCボードの要件が存在する場合、時として送信波形に手を加えることが必要となります。このアプリケーションノートは、T1/E1/J1トランシーバのDS26518が、出力パルスの小さな、または大きな成形を行うための精密な方法をどのように内蔵しているのかについて解説します。また、このアプリケーションノートは、多様なアプリケーションの要件を満たすために設計者が送信波形を成形することを可能にする、出荷テストレジスタのアクセス方法についても説明しています。

T1およびE1の送信波形:設定可能部分

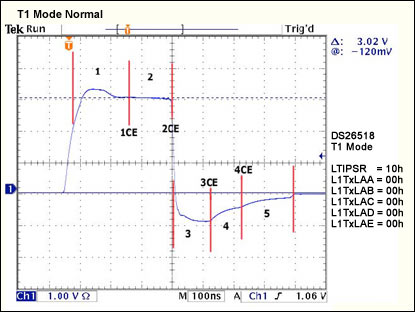

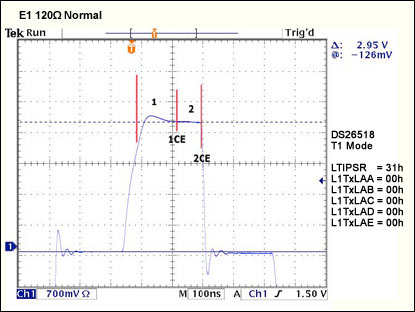

DS26518のレジスタは、振幅とタイミングの送信パルスの2つの主要部分の制御を提供します。T1およびE1の送信パルスは複数の部分に分割され、要求される波形を提供するために個々を処理することができます。図1は、どのようにT1パルスが分割されるのか、および各部分を制御するためのレジスタを示しています。図2は、E1パルスについて同様の情報を提供しています。

T1およびE1の送信波形:振幅制御

DS26518の送信パルスの振幅は、2つの方法で制御することができます。

- DACのゲインを調整

L1TXLAEレジスタのビットDAC[3:0]は、同時にT1またはE1の全レベルの正および負の調整を提供します。 - 部分的な波形レベルを調整

レベル調整レジスタのWLA[3:0]ビットは、波形の特定部分の微調整を提供します。電圧レベルのステップサイズは、設定されたDACのゲインに比例して変化します。DACのゲインを10%増加させた場合、ステップサイズもまた10%増加します。

T1およびE1の送信波形:タイミング制御

DS26518の送信パルスレベルのタイミングは、レベル調整レジスタのCEA[2:0]ビットによって制御されます。各エッジはTCLKの1/32の増減量で、正または負の両方向に移動させることができます。

全般的な推奨事項

DACゲインの修正は、1つのレジスタを変更するだけで、DACゲインが全体の波形を制御するため、送信パルスの振幅を最も制御しやすい方法です。最初にDACゲインを使用することで、必要に応じて、個々のレベル調整レジスタの部分修正を最小にすることが可能となります。DACの最大出力は、VDDによって影響されます。VDDの最小値において、最大のDACゲイン設定が達成不可能となる場合があります。また。VDDの変動は、ラインドライバの出力段による到達可能な最大電圧に影響する可能性があります。

負の値は、符号付き整数表現を使用しません。MSBは符号ビットであり、LSB部は、符号とは無関係に大きさを表しています。例えば、WLA[3:0]レジスタの-3は、1101b (4ビットの符号付き整数表現)ではなく1011b (ビット3を負を意味する1に設定し、次の3ビットの011は、大きさの3)になります。

図1. T1パルス制御部分

T1 パルス制御部分

| オーバシュート(1) | レジスタL1TXLAA WLA[4:0] |

| クロックエッジ(1CE) | レジスタL1TXLAA CEA[2:0] |

| (1CE) = オーバシュートから平坦域までのクロックエッジ遷移 | |

| 平坦域(2) | レジスタL1TXLAB WLA[4:0] |

| クロックエッジ(2CE) | レジスタL1TXLAB CEA[2:0] |

| (2CE) = 平坦域から立下りエッジまでのクロックエッジ遷移 | |

| アンダシュート(3) | レジスタL1TXLAC WLA[4:0] |

| クロックエッジ(3CE) | レジスタL1TXLAC CEA[2:0] |

| (3CE) = 立下りエッジからアンダシュートの終点までのクロックエッジ遷移(3) | |

| アンダシュート(4) | レジスタL1TXLAD WLA[4:0] |

| クロックエッジ(4CE) | レジスタL1TXLAD CEA[2:0] |

| (4CE) = アンダシュートの終点(3)からアンダシュートの終点(4)までのクロックエッジ遷移 | |

| アンダシュート(5) | レジスタL1TXLAC WLA[4:0] |

図2. E1パルス制御部分

E1パルス制御部分

| オーバシュート(1) | レジスタL1TXLAA WLA[4:0] |

| クロックエッジ(1CE) | レジスタL1TXLAA CEA[2:0] |

| (1CE) = オーバシュートから平坦域までのクロックエッジ遷移 | |

| 平坦域(2) | レジスタL1TXLAB WLA[4:0] |

| クロックエッジ(2CE) | レジスタL1TXLAB CEA[2:0] |

| (2CE) = 平坦域から立下がりエッジまでのクロックエッジ遷移 | |

注:レジスタL1TXAC、L1TXAD、およびL1TXAEは、E1モードでは未使用。

LIUテストレジスタの説明

表1に、LIU 1のレジスタアドレスと説明を示します。これらのレジスタが、LIU 2から8についても繰り返されます。

表2に、すべてのLIUテストレジスタのアドレスを示します。

表1. LIU 1テストレジスタ

| アドレス | 省略形 | 説明 |

| 1011h | L1TXLAA | LIU 1 Tx レベル調整A (テストレジスタ) |

| 1012h | L1TXLAB | LIU 1 Tx レベル調整B (テストレジスタ) |

| 1013h | L1TXLAC | LIU 1 Tx レベル調整C (テストレジスタ) |

| 1014h | L1TXLAD | LIU 1 Tx レベル調整D (テストレジスタ) |

| 1015h | L1TXLAE | LIU 1 Tx レベル調整E (テストレジスタ) |

表2. LIU 1テストレジスタのアドレス範囲

| LIU | アドレス範囲 |

| 1 | 1011–1015h |

| 2 | 1031–1035h |

| 3 | 1051–1055h |

| 4 | 1071–1075h |

| 5 | 1091–1095h |

| 6 | 10B1–10B5h |

| 7 | 10D1–10D5h |

| 8 | 10F1–10F5h |

LIUテストレジスタの詳細

LIU 1についてレジスタアドレスと説明を以下に示します。これらのレジスタが、LIU 2から8についても繰り返されます。

| レジスタ名 | L1TXLAA |

| レジスタの説明 | LIU Tx レベル調整A (オーバシュート電圧) |

| レジスタアドレス | 1011H |

| 読み/書き機能 | R/W |

| ビット# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名称 | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| デフォルト | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ビット7~3:出力レベル1の送信波形レベル調整(WLA[4:0])

振幅をデフォルトから±360mV移動します。

ビット7 = 符号ビット(「1」は負を意味)

ビット6~3 = 振幅の大きさ(符号なし)、LSBステップサイズは20mV

ビット2~0:クロックエッジ調整(CEA[2:0])

クロックエッジをデフォルトから±3 32x-clks移動します。

<2> = 符号ビット(「1」は負を意味)

<1:0> = 32x-clks単位の移動値(符号なし)

| レジスタ名 | L1TXLAB |

| レジスタの説明 | LIU Tx レベル調整B (平坦域電圧) |

| レジスタアドレス | 1012H |

| 読み/書き機能 | R/W |

| ビット# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名称 | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| デフォルト | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ビット7~3:出力レベル2の送信出力レベル調整(WLA[4:0])

振幅をデフォルトから±360mV移動します。

ビット7 = 符号ビット(「1」は負を意味)

ビット6~3 = 振幅の大きさ(符号なし)、LSBステップサイズは20mV

ビット2~0:クロックエッジ調整(CEA[2:0])

クロックエッジをデフォルトから±3 32x-clks移動します。

<2> = 符号ビット(「1」は負を意味)

<1:0> = 32x-clks単位の移動値(符号なし)

| レジスタ名 | L1TXLAC |

| レジスタの説明 | LIU Tx レベル調整C (アンダシュート電圧) |

| レジスタアドレス | 1013H |

| 読み/書き機能 | R/W |

| ビット# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名称 | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| デフォルト | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ビット7~3:出力レベル3の送信出力レベル調整(WLA[4:0])

振幅をデフォルトから±360mV移動します。

ビット7 = 符号ビット(「1」は負を意味)

ビット 6~3 = 振幅の大きさ(符号なし)、LSBステップサイズは20mV

ビット2~0:クロックエッジ調整(CEA[2:0])

クロックエッジをデフォルト値から±3 32x-clks移動します。

<2> = 符号ビット(「1」は負を意味)

<1:0> = 32x-clks単位の移動値(符号なし)

| レジスタ名 | L1TXLAD |

| レジスタの説明 | LIU Tx レベル調整D (アンダシュート電圧#2) |

| レジスタアドレス | 1014H |

| 読み/書き機能 | R/W |

| ビット# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名称 | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| デフォルト | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ビット7~3:出力レベル4の送信出力レベル調整(WLA[4:0])

振幅をデフォルトから±360mV移動します。

ビット7 = 符号ビット(「1」は負を意味)

ビット6~3 = 振幅の大きさ(符号なし)、LSBステップサイズは20mV

ビット2~0:クロックエッジ調整(CEA[2:0])

クロックエッジをデフォルト値から±3 32x-clks移動します。

<2> = 符号ビット(「1」は負を意味)

<1:0> = 32x-clks単位の移動値(符号なし)

| レジスタ名 | L1TXLAE |

| レジスタの説明 | LIU Tx レベル調整E (アンダシュート電圧#3) |

| レジスタアドレス | 1015H |

| 読み/書き機能 | R/W |

| ビット# | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 名称 | WLA4 | WLA3 | WLA2 | WLA1 | WLA0 | CEA2 | CEA1 | CEA0 |

| デフォルト | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ビット7~4:出力レベル5の送信出力レベル調整(WLA[3:0])

振幅をデフォルトから±180mV移動します。

ビット7 = 符号ビット(「1」は負を意味)

ビット6~4 = 振幅の大きさ(符号なし)、LSBステップサイズは20mV

ビット3~0:DACゲイン調整(DAC[3:0])

以下の設定によってDACのゲインを変更します。

| DAC[3:0] | DACゲイン値 |

| 0000 | 公称(デフォルト) |

| 0001 | +2.67% |

| 0010 | +5.34% |

| 0011 | +8.67% |

| 0100 | +11.34% |

| 0101 | +14.0% |

| 0110 | +17.34% |

| 0111 | +20.97% |

| 1000 | -2.1% |

| 1001 | -4.0% |

| 1010 | -6.0% |

| 1011 | -8.0% |

| 1100 | -10.0% |

| 1101 | -12.0% |

| 1110 | -14.0% |

| 1111 | -15.34% |

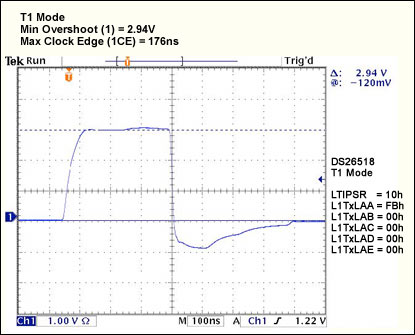

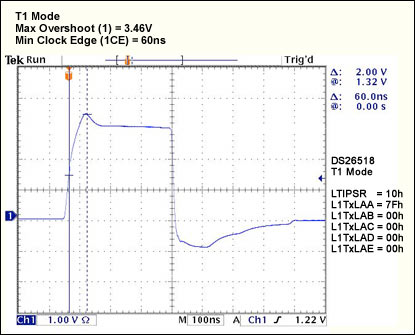

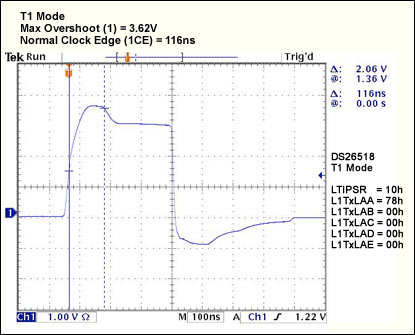

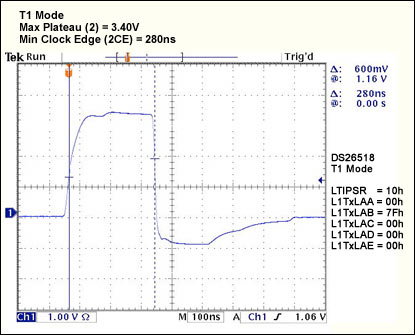

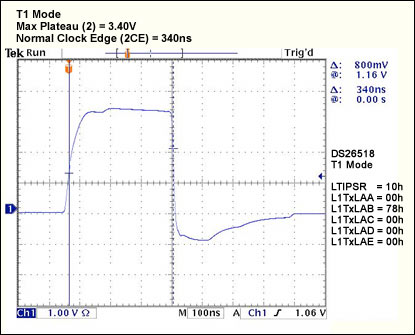

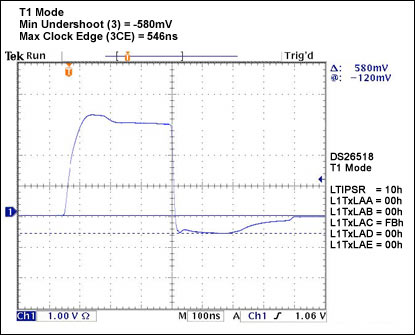

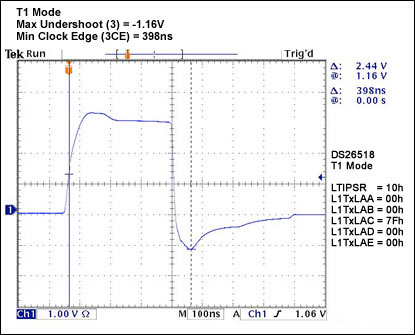

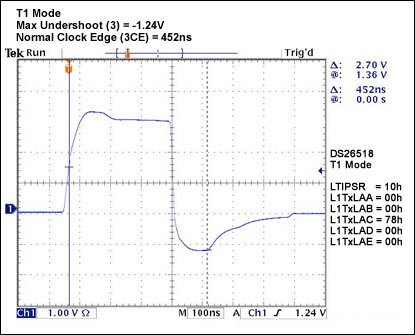

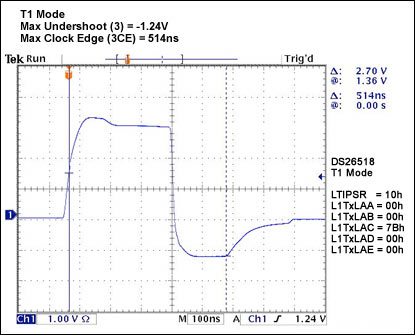

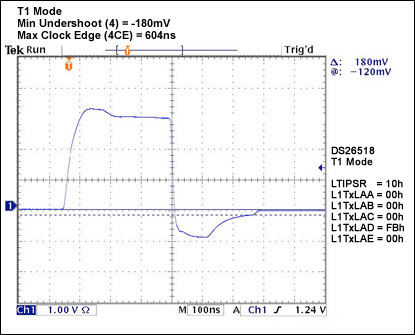

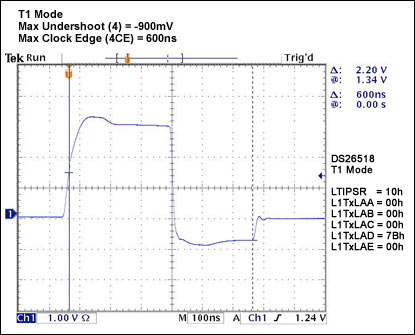

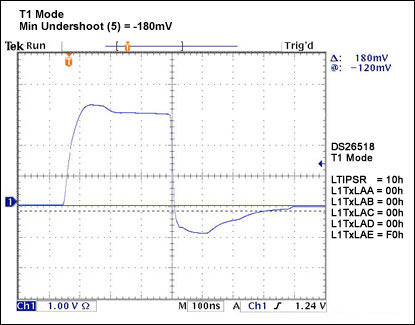

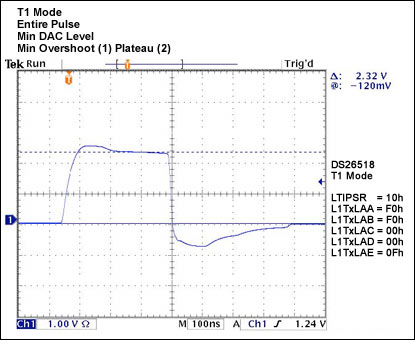

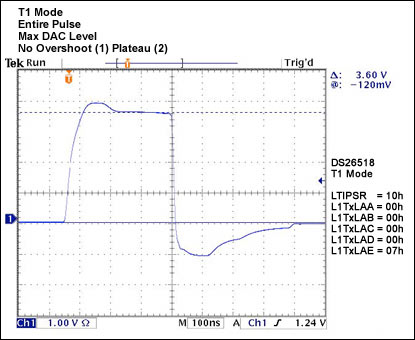

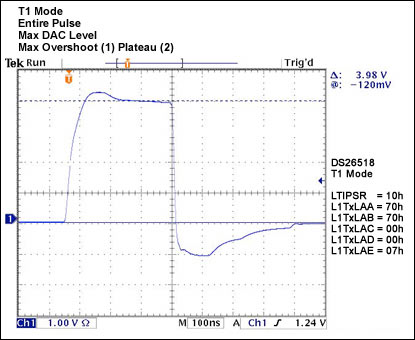

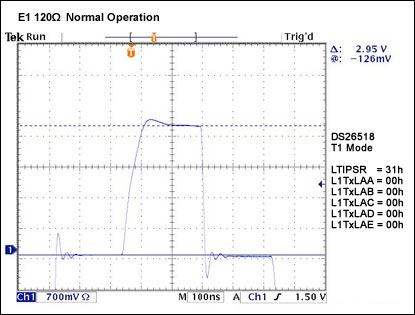

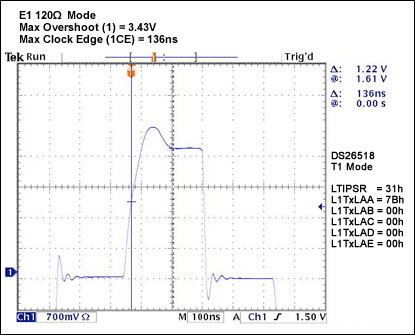

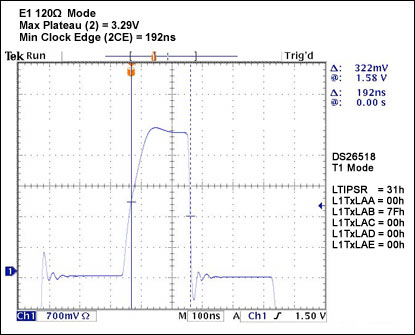

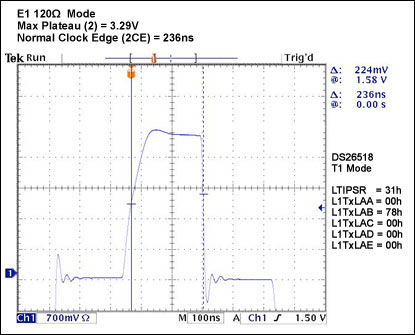

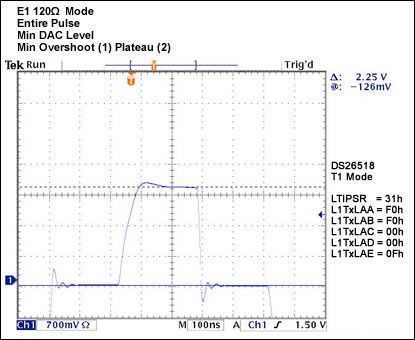

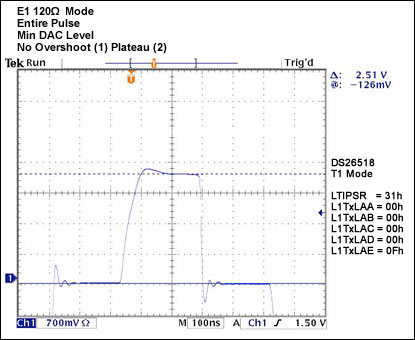

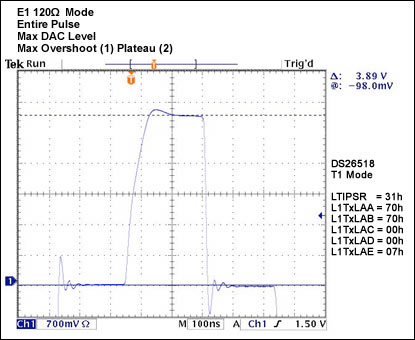

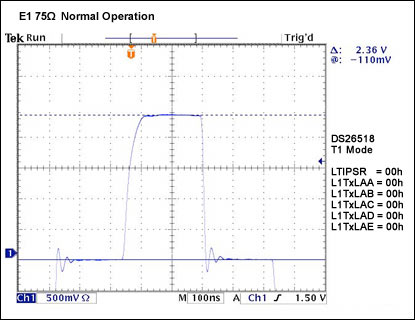

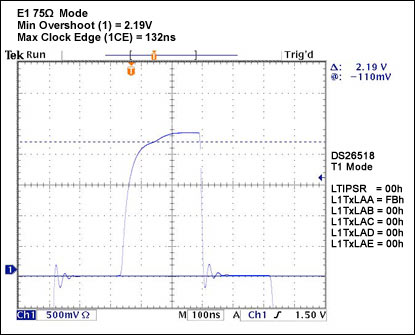

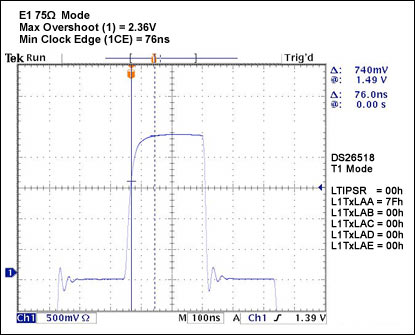

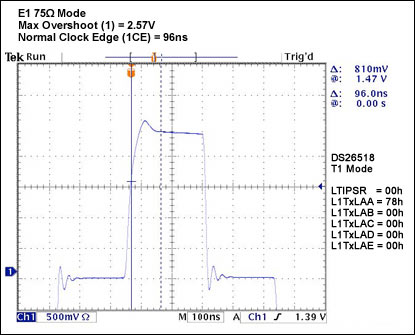

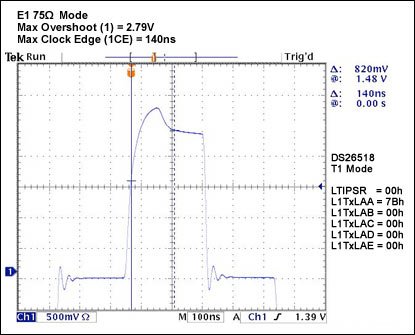

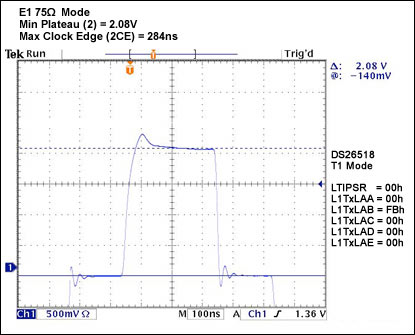

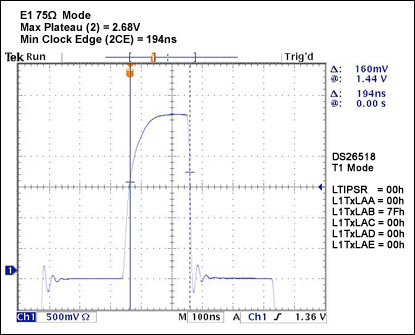

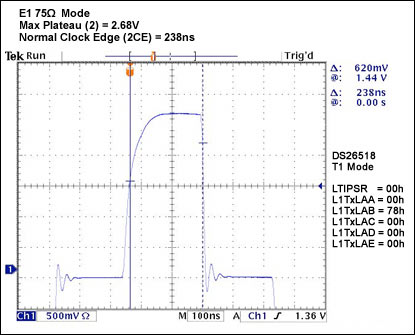

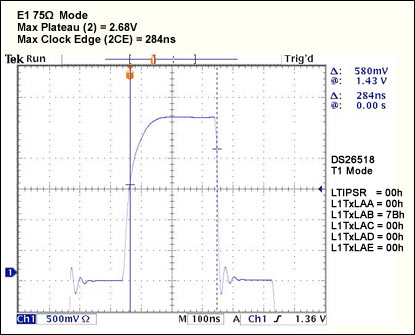

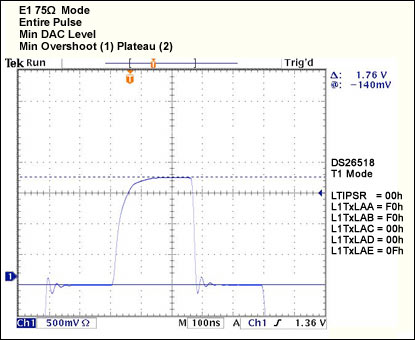

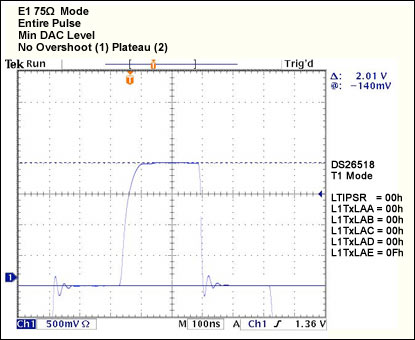

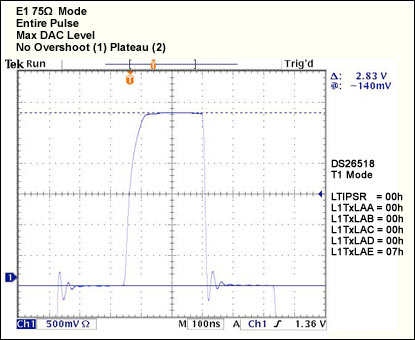

T1およびE1送信波形データ

以下のデータは、DS26518についての予測される結果についての典型例です。このデータは、T1およびE1送信パルスの振幅とタイミングを制御するためのレベル調整レジスタの使用範囲および使用方法を決定するガイドラインとなります。このデータは、3.3VのVDDで室温において収集されたものです。

図3.

図4.

図5.

図6.

図7.

図8.

図9.

図10.

図11.

図12.

図13.

図14.

図15.

図16.

図17.

図18.

図19.

図20.

図21.

図22.

図23.

図24.

図25.

図26.

図27.

図28.

図29.

図30.

図31.

図32.

図33.

図34.

図35.

図36.

図37.

図38.

図39.

図40.

図41.

図42.

図43.

図44.

図45.

図46.

図47.

図48.

図49.

図50.

図51.