資料ライブラリ

アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-737: ADIsimADC によるADC モデリングの方法

コンバータのモデリング

コンバータのモデリングは、見落とされるか、省略されてきました。あるいは理想データ・コンバータ・モデルを使って実行されてきました。ミックスド・シグナル技術を採用するシステムが増えるにつれて、システム・モデリングはますます重要になっています。デザイン・サイクルの短縮とファースト・パスでの成功を求める圧力により、完全なシステム・モデリングの重要性が増しています。ADIsimADC™は、この増え続けるニーズに対する答えとして開発されました。

理想コンバータ・モデルはよくファンクショナル・モデリングとして使われますが、特定のデバイスがシステムの目標を満たすか否かを判断するために必要な詳しい性能を提供してくれません。これが、ADIsimADC が開発された理由です。まず、ADIsimADC は選択したデバイスの適用性を判断する条件を使って、システム内の特定のコンバータの性能を確認する手段を提供します。ADIsimADC はADC のすべての特性をエミュレートしませんが、システム・シミュレーション内で実際のコンバータをユーザがモデル化できるようにする目標を実現するため努力を続けています。

ビット・イグザクト対ビヘイビア

ビット・イグザクト・モデルは、既知のテスト信号を入力した場合に既知で予測可能な出力が得られるモデルです。ADIsimADC はビット・イグザクト・モデルではありません。これらのタイプのモデルはよくデジタル・システムで使用されています。アナログ機能を扱う場合、ノイズ、歪み、その他の非直線性があるため、与えられた入力に対して既知の応答が得られることはありません。応答の一部を予測できる場合がありますが、その他の多くの部分は、歪み、ノイズ、さらにはデバイス間のバラツキの影響を受けます。さらに、ビット・イグザクト・モデルを用意するためには、過渡応答を処理するSPICE モデルのような回路シミュレーション・ファイルを用意する必要がありますが、これらのモデルは大規模、複雑、非常に低速であるため、最終的な精度が制約されてしまいます。縮小した、または等価なSPICE モデルを使うと複雑さは軽減されますが、スタティック性能とダイナミック性能の詳細なモデリングができません。

ビヘイビア・モデルでは複雑さが解消されると同時に、回路ファイルでは実現できない詳細性能のモデリングが可能になります。ADIsimADCとVisualAnalog™の組み合わせは、スタンドアロンのコンバータ評価ツールとして機能します。

ADIsimADC™は、Agilent Technologies社のADS、Applied Wave Research社のVSS、National Instrument社のツール、MATLAB®、C++などの他の多くのサード・パーティのシミュレーション・ツールと組み合わせて使うこともできます。これらのツールと組み合わせて使う情報は、www.analog.com/ADIsimADCから提供しています。

モデル対ハードウェア

システムまたはADC のモデリングは、実システムの構築やキャラクタライゼーションの代わりになるものではありません。回路をモデル化することは1 つの問題ですが、実際にモデルを構築してテストすることは別の問題です。

シミュレーションで得られた性能を実現するためには、アナログまたはミックスド・シグナルのデバイスの場合と同様に、適切なレイアウトと構成が必要です。このため、製品データ・シートに記載するすべてのレイアウト・ルールとガイドラインに従うことが重要になります(図4 参照)。十分な電源バイパス・コンデンサを使用する重要性は1 つの例です。ミックスド・シグナル・デバイスには幾分かのデジタル回路が含まれているため、デジタル・スイッチング・ノイズが問題になり、適度なコンデンサを使用しないと、これらのスイッチング電流により最適なデバイスであっても性能が大幅に損なわれてしまいます。コンバータの周囲には、追加コンデンサ、インダクタ、抵抗などのその他のサポート・デバイスが必要になります。必要なものを知る最善の方法は、製品データ・シートと評価ボード回路図を調べることです。

Notes:- R2 is installed for input matching on the primary of T3. R15 is not installed.

R15 is installed for input matching on the secondary of T3, R2 is not installed. - AC-COUPLED AIN is standard, R3, R4, R5, R8 and U3 are not installed.

If DC-COUPLED AIN is required, C30, R15 and T3 are not installed. - AC-COUPLED ENCODE is standard. C5, C6, C33, C34, R1, R11-R14 and U8 are not installed.

If PECL ENCODE is required, CR1 and T2 are not installed.

モデル化に重要な仕様は?

ADIsimADC は、実デバイスの実際の性能を提供することを目標としています。モデル化に重要な仕様は、実行しようとしている解析の種類に依存します。たとえば、制御ループでは正確な伝達関数と遅延情報が必要となり、無線システムではノイズと歪みの正確な表現が必要になります。ADIsimADC は、オフセット、ゲイン、サンプル・レート、帯域幅、ジッタ、レイテンシ、AC 直線性、DC 直線性などの、データ・コンバータの重要な多くの仕様をモデル化します(AC 直線性の詳細については、AN-835 アプリケーション・ノート「Understanding High Speed ADC Testing and Evaluation」を参照してください)。

このアプリケーション・ノートでは、これらの仕様の詳細とこれらのADIsimADC での扱い方について説明します。

ゲイン、オフセット、DC 直線性

コンバータのフルスケール・レンジは、コンバータのデザインによって決められます。固定、選択可能、または可変です。コンバータのゲイン誤差は公称値からの偏差で、入力スパンと呼ばれることもあります。ADC は電圧入力デバイスであるため、フルスケール・レンジはDCまたは低周波での電圧として規定されます。

オフセットは、コンバータのフルスケール・レンジの1/2からの実際の電荷(多数)キャリア変移によるずれ量として定義されます。これは、入力をフルスケールの1/2に接続することにより測定することができます。多くのデバイスには、入力同相モード電圧を設定するために入力ピンにバイアスを与える内部接続があります(図1 参照)。

このようなデバイスでは、この接続を外部で行う必要はありません。シングルエンド入力の場合は入力をフローティングにしておくか、あるいは差動入力の場合には互いに短絡することができます。内部に同相モード電圧への接続がないデバイスでは、外部で接続する必要があります(図2 参照)。入力スパンの場合と同様に、同相モード電圧は固定または調整可能にすることができます。設定方法については、デバイスのデータ・シートをご覧ください。

ADIsimADC では、入力スパンまたは同相モードの変更を許していません。複数の入力スパンを持つデバイスには、別々のコンバータ・モデルを提供します。同相モードは、すべてのデバイスに対して固定で、変更することはできません。異なる同相モード・レンジを使うシステムのモデル化が必要な場合は、外部オフセットを使って差を減算することができます。

ADC のDC 直線性(図3 参照)は、コンバータの量子化法とスタティック伝達関数によって決定されます。コンバータには多くのタイプがあり、各々は独自の伝達関数を持ち、DC と高周波で異なる結果を発生します。異なるタイプのコンバータと伝達関数のコンバータ性能への影響の詳細については、参考文献のセクションのBrannon(2001)とKester (2004)の参考文献をご覧ください。

サンプル・レート

サンプル・レートの変化とアナログ入力周波数の変化として、コンバータの性能が変化します。サンプル・レートの点では、大部分の優れたコンバータは最小規定サンプル・レートから最大規定サンプル・レートまで一貫した性能を提供します(図5 参照)。最小より下のサンプル・レートでは、正常に動作しないコンバータもあります。これは、内蔵コンデンサに蓄積された電荷に起因して発生するもので、この電荷の放電すなわち電圧低下により正しくないデータ変換が生じます。したがって、コンバータのデータ・シートで最小有効サンプル・レートを確認しておく必要があります。最大サンプル・レートより上では、2 つの問題が発生する可能性があります。デバイス内部で、デジタル信号を1 つのステージから次のステージへ渡せないことがあります。これは、チップ上でセットアップ・タイムまたはホールド・タイムが不足するために発生します。もう1 つの問題は、クリティカルなアナログ信号が割り当てられた処理時間内に安定しないことです。これの1 つの例としては、ホールド・コンデンサのアクイジション・タイムがあります。前と同様に、コンバータのデータ・シートで最大サンプル・レートを確認しておく必要があります。ADIsimADC では、規定のサンプル・レートを使ってコンバータ動作を求めますが、デバイスの規定範囲外に対しては、このモデルはすべてゼロの結果を出力します。

帯域幅

アナログ入力周波数が高くなると、振幅応答の減衰により、コンバータの見掛け上のフルスケール・レンジが実効的に大きくなるため、コンバータ応答でのロールオフが必要になります。応答が3 dB 減少する周波数は、コンバータの3 dB 帯域幅と呼ばれます。

コンバータの性能は、アナログ入力周波数が高くなるにつれて、コンバータの周波数応答に従ってロールオフします(図6 参照)。これは、ADIsimADC 内でモデル化されているため、モデル内で応答が減衰させられています。この減衰を考慮するため、モデルのデフォルトとして指定された振幅を超えて入力信号振幅を大きくする必要があり、このため入力はコンバータのフルスケール・レンジより大きく見えます。実際には、この信号はパッケージ、デバイスの寄生、さらにサンプル・アンド・ホールド・アンプ(SHA)のホールド・コンデンサにより形成されるフィルタにより減衰させられます。このため、この信号は実際には規定スパン内に収まります。

ダイナミック歪みとスタティック歪み

ADC の帯域幅は有限であるため、原理的なスルーレート制限、すなわちダイナミック制限があります。このスルーレート制限が、ADC 内の歪み原因の1 つになっています。データ・コンバータの入力周波数をDC から高い周波数まで変化させると、コンバータのSFDR 性能と高調波性能が低下します(図7 参照)。

歪み制限は少なくとも部分的にはスルーレートの問題から発生するため、アナログ周波数を一定に維持したまま信号入力の振幅を小さくすると、スルーレートが小さくなるため、コンバータのフルスケールに対して高調波性能と歪み性能を改善することができます。これらのスプリアスは必ずしも古典的なn 次積の傾向に従いませんが、この傾向は弱いながらもよく観測されます。信号レベルが小さくなると、ダイナミックな影響はなくなりますが、スタティックな影響が歪みの支配的な因子として急速に置き換わります。スタティックな歪みは、コンバータの伝達関数に起因する歪みです(図8 参照)。この歪みはまったく予測できない結果を発生させることがよくあります。これには、入力レベルの関数として急激に変化するスプリアスが含まれるため、正と負のスロープ特性を示すことがあります。これらのスプリアスは、主にコンバータのアーキテクチャ特性に起因します。異なるコンバータは異なるスタティック伝達関数を持つため、歪み応答は大きく異なります。さらに、これらはアナログ部品であるため、同じデザイン内の各部品は入力信号に対して異なる応答を示します。このため、部品間でバラツキがあります。

ADIsimADC は、データ・コンバータの公称性能をモデル化しようとします。ADIsimADC は優れた仕事をしますが、部品間のバラツキは常に発生します。予測される性能バラツキを求めるときは、コンバータのデータ・シートを調べてください。

ジッタ

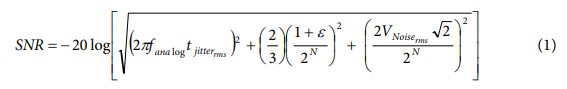

コンバータ・アナログ入力のスルーレート制限の他に、高周波アナログ信号のサンプリングで最も困難な点の1つはジッタです。ジッタは、すべてのデータ・コンバータ・フロント・エンドでのサンプリング・プロセスで発生するサンプル間隔のバラツキです。低周波のアナログ入力では、ジッタを無視することができますが、高周波のアナログ入力では、ジッタのためにアナログ・サンプリング・プロセスで発生する誤差は大きな性能低下を発生させます(図9 参照)。サンプリング・タイム誤差はフェムト秒のオーダーですが、SNRで発生する制約は大きくなります(www.analog.comに掲載するAN-501 アプリケーション・ノート、「Aperture Uncertainty and ADC System Performance」を参照してください)。高周波での全体ノイズには複数の要因がありますが、ジッタは明らかに支配的な要因です。式1 に示すように、特に高分解能コンバータでは支配的です。

ジッタには2 つの原因があります。1 つ目は、デバイスに内在する内部ジッタです。最新のコンバータ・デザインでは、種々の技術を採用して内部ジッタを小さくする努力をしているため、内部ジッタは2 つの原因の内で小さい方になっています(無視はできません)。2 つ目として、ジッタの主要原因になっているのは、外部クロック・ジッタです。モデルがジッタから生ずるノイズを計算する際、これらの2 つのジッタ原因はノイズを計算する前に統合されます。

ADIsimADC は入力信号の瞬時スルーレートを計算し、この値にガウス・モデルによるジッタ・ノイズ原因(シグマ= 内部ジッタと外部ジッタを統合したrms 値)を乗算します。この結果としてノイズのジッタ成分が得られます。この値は、アナログ入力の周波数と振幅レベルの関数としてジッタの影響を正確にモデル化しています。外部ジッタのデフォルトは、デバイスのキャラクタライゼーション時に使用されたセットアップでの外部ジッタですが、この値は任意の値に変更することができます。

レイテンシ

多くのタイプのコンバータには、サンプルのタイミングから有効なデータがデジタル出力に出力されるまでの間の遅延があります。SAR コンバータとフラッシュ・コンバータは一般に、サンプル周期後直ちにデータを出力します。パイプライン化コンバータやΣ-Δ コンバータのようなマルチステージ・コンバータは、多くのクロック・サイクルが経過するまでデータを出力しません。これは、制御システムやレイテンシが重要となるその他のシステムでは問題となります。ADIsimADC では、レイテンシをクロック周期の整数値でモデル化します。このため、パイプラインへのデータ書き込み中に変換周期の始めで無効なデータが発生し、パイプラインのフラッシュ中に変換周期の終わりで有効なデータが発生するということが起こります。このモデルを使用するときは、バッファのフラッシュまたはその他の方法により、パイプライン遅延を適切に考慮するための注意が必要です。

結論

ADIsimADC は、特定の動作条件下でADC 性能をシミュレーションする有効なツールです。ソフトウェアが実世界の状態をエミュレートするため、システム・モデリングをより完全なものにすることができます。ハードウェアを置き換えるものではありませんが、システム・デザイン内でのADC 動作を理解する最初のステップになります。

参考文献

Brannon, Brad.2006. AN-501 Application Note Aperture Uncertainty and ADC System Performance.Analog Devices,Inc. (March).

Brannon, Brad.2001. “DNL and Some of Its Effects on Converter Performance.”Wireless Design and Development(June).

Brannon, Brad and Rob Reeder.2006. AN-835 Application Note Understanding High Speed ADC Testing and Evaluation.Analog Devices, Inc. (April).

Kester, Walt, ed. 2004. Analog-to-Digital Conversion.Analog Devices, Inc. ISBN 0-916550-27-3.

Looney, Mark.Analog-to-Digital Converter (ADC) Signal-to-Noise Ratio (SNR) Analysis.Unpublished paper.