アプリケーション・ノート使用上の注意

本アプリケーションノートの英語以外の言語への翻訳はユーザの便宜のために提供されるものであり、リビジョンが古い場合があります。最新の内容については、必ず最新の英語版をご参照ください。

なお、日本語版のアプリケーションノートは基本的に「Rev.0」(リビジョン0)で作成されています。

AN-352: 高速コンパレータを適正に使用することによって得られる多くの有用な回路機能

質問:高ゲインあるいはオープン・ループ構成の標準オペアンプは、電圧コンパレータとして転用できないものなのでしょうか?

数十マイクロ秒の応答時間で十分ということであれば、使用はできます。しかも、低バイアス電流、高精度、低オフセット電圧が必要であれば、大部分の標準電圧コンパレータよりオペアンプのほうがよいでしょう。しかし、ほとんどのオペアンプは帰還の安定性を確保するために位相/周波数補償回路を内蔵しているので、ナノ秒単位の応答を実現するのはそう簡単ではありません。これに対し、低価格の汎用コンパレータLM311の応答時間は200ns です。

また、オペアンプの出力は標準ロジック・レベルと簡単にはマッチングしません。外部クランプやレベル・シフト回路がないと、コンパレータとして動作するオペアンプは正電源と負電源の数ボルトの範囲内でスイングします。これは、標準TTL/CMOS ロジック・レベルに適合しません。

コンパレータの発振が制御不能になります。どうしてこうなるのでしょうか?

電源のバイパスを調べてみてください。場合によっては、電源ライン上の数インチのPCパターンによって許容値を超えたDC抵抗やインダクタンスが発生します。その結果、出力スイッチング中に過渡電流が流れて電源電圧が変動し、それがグラウンドと電源ラインを経由して入力に逆戻りすることになります。これに対処するために、低損失のコンデンサ(0.1μFセラミック・コンデンサ)をできる限りコンパレータの電源ピンの近くに接続して、それが高速スイッチング中に低インピーダンスのエネルギー蓄積器として機能するようにします1。

バイパス・コンデンサを設置しましたが、高速コンパレータの発振を防ぐことができません。何が問題でしょうか?

コンパレータのグラウンド接続に問題があるかもしれません。グラウンド・リードはできる限り短くし、低インピーダンスのグラウンド・ポイントに接続してリード・インダクタンスによるカップリングを最小限に抑える必要があります。できればグラウンド・プレーンを使用し、ソケットは避けてください。

発振の原因としてもう一つ考えられるのは、入力に対する高ソース・インピーダンスと浮遊容量です。数キロオームのソース・インピーダンスや数ピコファラッドの浮遊容量でも、手に負えないような発振の原因になり得ます。スコープ・プローブのグラウンド・クリップを含め、リードは短くしてください。最良の測定結果を得るために、できる限り短いグラウンド・リードを使用してそのインダクタンスを最小限に抑える必要があります(1 インチ未満)。

入力信号が低速で移動し、それが遷移電圧を通過するときにコンパレータに「チャッタ」が生じているようにみえます。どうしてデバイスから単一のクリーンな遷移が得られないのでしょうか?

一般に、この問題の原因となるのはコンパレータの高いゲインと広い帯域幅です。これにより、あらゆるノイズが増幅されることとなり、信号が遷移領域を通過すると、ノイズが原因となって、高速に応答するアンプの出力が前後にはね返りを生む可能性があります。また、デバイスの感度(すなわち、ゲイン)は遷移中に高くなるので、帰還による発振は増大傾向を示します。可能であれば、信号をフィルタ処理してそのノイズを最小限に抑えてください。

次に、歯車機構のバックラッシュのように反転が起きる前に特定量の入力の変化が必要となるヒステリシスを利用してみてください。たとえば、AD790 ではハイレベルからローレベルへの遷移が起きた後、ローレベルからハイレベルへの遷移が起きるためには、内部ヒステリシスがあるため、入力電圧(正の入力)が500μV 増大しなければなりません。

コンパレータに内蔵のヒステリシスがない場合は、それを外部から追加できるでしょうか?

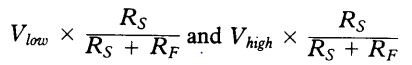

はい、外部に正帰還を加えることでヒステリシスを生成できます。これを行うには、コンパレータ出力のごく一部を正の入力に帰還させる必要があります。図1 にこの単純な技法を示します。下側遷移点から上側遷移点までのヒステリシス電圧は、帰還抵抗RF、ソース抵抗RS、低出力レベルVlow、および高出力レベルVhighに依存します。低遷移点と高遷移点は次式に基づいて設定されます。

図1. コンパレータに外部ヒステリシスを適用

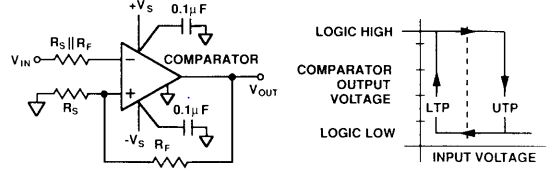

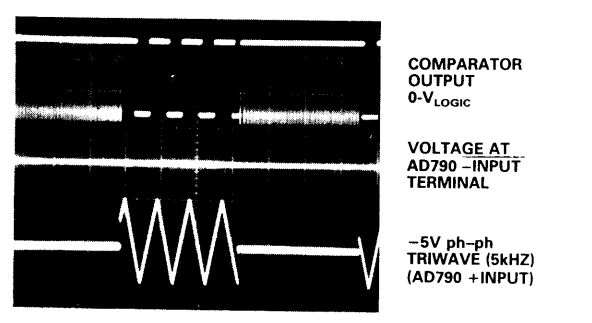

図2 は、外部ヒステリシスの追加によってどのようにコンパレータの応答を「クリーンアップ」できるかを示しています。図2aには、ヒステリシスを追加しない場合のコンパレータの応答(バイポーラ出力振幅)を示しています。三角波入力(パターンA)が遷移点(グラウンド)を通過すると、デバイスは強く発振し、発振信号の一部をグラウンドと信号源にカップリングします。図2bに、5mVの外部ヒステリシスを加えたコンパレータの応答を示します。この場合は、かなりクリーンな遷移となっています。

図 2. ヒステリシスでクリーンアップされたコンパレータの応答

外部ヒステリシスを用いて問題となるのは、出力電圧が電源電圧と負荷に依存するという点です。つまり、ヒステリシス電圧はアプリケーションごとに異なる可能性があります。これは分解能に影響を及ぼしますが、それほど大きな問題ではありません。ヒステリシスは一般に当該レンジのごく一部であり、計算値の2 倍または3 倍(あるいはそれ以上)のマージンを見ておけば誤差範囲内に収まります。数個のコンパレータを交換してみれば、マージンの信頼性を増すことができます。帰還用に巻線抵抗を使用するのは避けてください。インダクタンスによって、状況がさらに悪化する恐れがあります。

伝播遅延と伝播遅延分散の違いは何でしょうか? この2 つのうち重要な仕様はどちらでしょうか?

伝播遅延は、入力信号が遷移点に到達してからコンパレータ出力が実際にスイッチングされるまでの時間を指しています。伝播遅延分散は、オーバードライブ・レベルに応じた伝播遅延の変動を意味します。自動試験システムでピン駆動の電子機器にコンパレータを使用すると、伝播遅延分散によって最大エッジ分解能が決まります。これとは対照的に、伝播遅延は固定時間オフセットとみなすことができるので、他の技術によって補償することができます。

現在、+5V のシステムを使用していますが、このシステムに補助電源電圧を追加したくはありません。単電源でコンパレータを使用できるでしょうか?

はい、使用できます。ただし、スレッショールドを設けるために、適正にバイパスされた高安定のリファレンス・ソースをデバイスの同相電圧範囲内で使用してください。信号レベルもこのソースを基準とします。

コンパレータが予想外の動作をすることがあります。この問題の原因は何でしょうか?

入力信号の同相電圧範囲を調べてください。オペアンプは通常同じレベルの入力電圧で動作しますが、コンパレータはこれとは違って一般に大きな差動電圧振幅が入力に現れます。入力がデバイスで規定された同相電圧範囲を越えると(規定の信号範囲内であっても)、コンパレータが間違って応答することがあります。適正な動作を確保するには、両方の入力信号がコンパレータの同相電圧範囲を越えないようにする必要があります。たとえば、AD790 の差動入力範囲は±Vs ですが、その同相電圧範囲は-Vs から+Vsより2V 低い電圧までとなります。

コンパレータのオフライン時にドリフトを最小限に抑える自動ゼロ調整回路として推奨できるものがありますか?

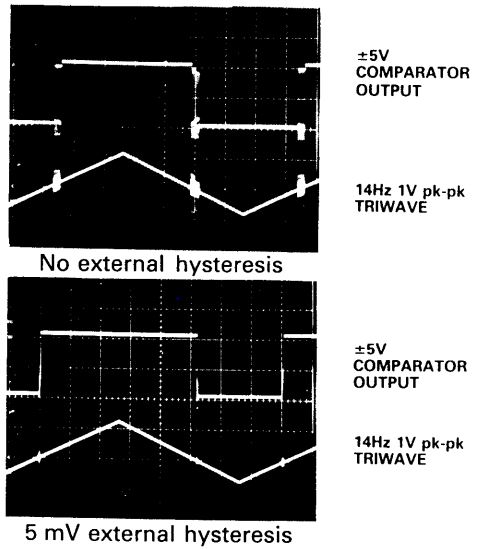

図3 と図4 に示す回路を試してみてください。キャリブレート・モード時に、入力は切断され、コンパレータの正入力がグラウンドに切り替えられます。コンパレータはループ内で逆極性の1 対の低電圧源に接続され、バッファ付きコンデンサはコンパレータの出力状態に応じて充電されます。

図3. キャリブレーション・サイクル中にオフセットを積分出力する自動ゼロ調整コンパレータ

図4. コンパレータ出力、バッファ出力、およびコンパレータ入力

コンパレータのマイナス入力端子がグラウンド電位より高くなると、コンパレータの出力はローレベルになり、1μF コンデンサは負電圧(-365mV)に接続され、バッファ・アンプの電圧は、グラウンド電位のプラス入力点(+ヒステリシスとオフセット)より低くなるまで降下し、コンパレータが切り替わります。グラウンドより低くなると、コンパレータの出力はハイレベルになり、コンデンサは正電圧(+365mV)に接続され、バッファ・アンプの出力は上昇します。最終段階では、コンパレータが切り替わるたびに(上昇変化がヒステリシス電圧を上回ったとき)電流の極性が反転し、コンデンサの電圧でバッファとコンパレータのオフセットが平準化されます。

キャリブレート・サイクルの終わりに、JFET スイッチがオープンになり、コンデンサはコンパレータおよびバッファのオフセット±ヒステリシス電圧に等しい値になるまで充電されます。また、キャリブレート信号はローレベルになり、極性スイッチへの帰還がディスエーブルとなって、入力信号がコンパレータに接続されます。

注

1 コンパレータの欠点に関する有用な情報が『Troubleshooting Techniques Quash Spurious Oscillations(Bob Pease 著、EDN、1989 年9 月14 日、pp.152-6)』に記載されています。