AN-139: 電源レイアウトとEMI

はじめに

PC基板のレイアウトによって、あらゆる電源設計の良し悪し が決まります。レイアウトにより、機能、電磁干渉(EMI)、温度 特性が決まります。スイッチング電源のレイアウトは黒魔術で はありませんが、設計プロセスで見落とされて、手遅れになっ てしまうことが多々あります。これには幸い対処法があります。 機能要件とEMI要件を満たすことが必要で、電源ユニットの レイアウトのトレードオフにおいて、機能の安定性に優れてい るものはEMIに対しても優れています。最初の試作から適正 なレイアウトを行うことは、コストを抑えるだけでなく、実際に EMIフィルタ、シールド機構、EMIテスト時間、PC基板の配線 などのリソースを大幅に削減します。このアプリケーションノー トでは非絶縁トポロジーを中心に説明しますが、いくつかの 絶縁トポロジーについても検討します。安定した電源を設計す るためのPC基板のレイアウトに関して、最適なテクノロジを選 択することができるでしょう。

私が約10年前に顧客として自動車用無線に初めてスイッチ・ モード電源を使用していたところ、多くの同僚から不可能と言 われたことを覚えています。しかしながら、レイアウトと入力フィ ルタリングでいくつかの問題を解決すると、すべてが正常に動 作しました。その後、顧客は自動車用無線レシーバのAM帯 域中で動作するLT®1940 1MHzデュアル降圧スイッチング・レ ギュレータを首尾よく採用することができました。電源ユニット (PSU)に金属シールドを追加する必要はありませんでした。 唯一の問題は、配置とレイアウトでした。目的を達成するため には、いくつかの手法を検討する必要があります。

非絶縁トポロジーの最も基本的なトポロジーの1つは降圧レ ギュレータです。EMIは高di/dtループから生じます。電源のワ イヤをはじめ、負荷のワイヤには大きなAC電流成分があって はなりません。したがって、関連するすべてのAC電流の源と なる入力コンデンサCINから、AC電流が終端する出力コンデ ンサCOUTに絞って解析することができます。

S1がクローズでS2がオープンのときのオンサイクルの間、AC 電流は赤のループを流れます(図1)。S1がオープンでS2がク ローズのときのオフサイクルの間、AC電流は青のループを流 れます。どちらの電流も台形波です。多くの場合、最も大きな EMIを生じるのが赤のループか青のループかを判断すること は困難です。ゼロからIPEAKに切り替わってゼロに戻る完全ス イッチングAC電流は緑のループにのみ流れます。緑のループ のACエネルギーとEMIエネルギーが最も大きいので、この ループをホット・ループと呼びます。

EMIを低減して機能を改善するためには、できるだけ緑の ループの放射影響を低減する必要があります。緑のループの PC基板面積をゼロまで低減でき、インピーダンスがゼロの理 想的な入力コンデンサを購入できれば、問題は解決できるで しょう。しかし、実際には限界があります。設計作業は最適な 妥協点を見つけることです。

LT8611降圧コンバータ(図3)のレイアウトを調べてみましょ う。LT8611は両方のスイッチを内蔵しているので、注意する 必要があるのは入力コンデンサの接続だけです。

図2の回路図から分かるように、レイアウトのためのホット・ ループを見つけるのは容易ではありません。

緑の線はトップ層のホット・ループです。入力コンデンサとデバ イスのスイッチをAC電流が流れます。LT8611のデモボード DC1750Aを図3に示します。ホット・ループの断面の電流密 度は図4のようになります。

ホット・ループの下側の銅箔の短絡ループやプレーンにより、 回路の機能とEMI特性がどの程度改善するでしょうか?

10cm×10cmの直角ループを27MHzで試験した結果を表1に 示します。この表は、上面のトレースの下側の切れ目のない銅 箔プレーンによってどの程度改善されるかを示しています。最 初の行はプレーンのない1層です。

プレーンとループ・トレースの間の絶縁がわずか0.12mmしか ない場合、187nHの1層ループのインダクタンスが13nHに減 少します。

| d (mm) |

f (MHz) |

C (pF) | L (nH) |

0.12mmのとき の倍数 |

|

| 18.4 | 400 | 187 | 1層の開ループ | 14.4 | |

| 21.2 | 400 | 141 | 内部銅箔の短絡ループ | 10.85 | |

| 1.5 | 38.9 | 400 | 42 | 切れ目のないプレート | 3.23 |

| 1.5 | 34.7 | 400 | 53 | 重なり合わない長方形 ループ |

4.08 |

| 0.5 | 52.1 | 400 | 23 | 細い長方形 | 1.77 |

| 0.27 | 55 | 400 | 21 | 1.61 | |

| 0.12 | 69 | 400 | 13 | 紙 |

多層基板(4層以上)の隣の層の切れ目のないプレーンのイン ダクタンスは、切れ目のないボトム・プレーンを備えた通常の 1.5mm 2層基板の1/3以下で、1層基板の1/14以下です。ホッ ト・ループに最小距離で切れ目のないプレーンを備えること がEMIを低減する最も効果的な方法の1つです。

プレーンに電流が流れる場所

緑のトップ層のホット・ループのAC磁界によってプレーンに 渦電流が生じます(図5)。これらの渦電流は、ホット・ループ の磁界とは逆のミラーAC磁界(赤線)を発生します。両方の 磁界は相殺されます。これはミラー電流がホット・ループに近 いほど有効です。電流はトップ層を往復します。シールド内の 最も起こり得る電流経路はトップ層の真下の電流の往復で す。両方の電流はほとんど同じです。プレーン電流はトップ・ト レース電流と同じ大きさが必要なので、プレーン両端に電流 を維持するのに必要な電圧を発生します。シールドの外側へ GNDバウンスとして現れます。

EMIの観点からは小さなホット・ループが最良です。同期ス イッチを内蔵し、ピン配置が最適化され、注意深い内部スイッ チ制御が行われる電源ICは、ショットキー・ダイオードを外付 けした非同期電源ICよりもEMI性能が優れています。また、 どちらも外付けMOSFETを備えたコントローラのソリューショ ンよりも性能が優れています。

昇圧回路は、連続モードで逆方向に動作する降圧回路と見 なすことができます。

ホット・ループは、S1がクローズのときの青のループと、図6に 示すS1オープン、S2クローズのときの赤のループの間の差と 定義できます。

LT3956 LEDドライバ昇圧コントローラのホット・ループを図7 の緑で示します。第2層は切れ目のないGNDプレーンです。 EMIを主に放射するのはホット・ループが構成する磁気アン テナです。ホット・ループの面積とそのインダクタンスには密接 な関係があります。インダクタンスを十分に配慮できれば、な るべく小さくします。アンテナの設計に余裕があれば、磁気ア ンテナの実効面積を低減します。近磁界を得るための、インダ クタンスの効果と磁気アンテナの効果は基本的に同じです。 詳細な背景説明については「付録A」と「付録B」を参照してく ださい。

シングル・インダクタの4スイッチ昇降圧回路(図8)は、降圧回 路に昇圧回路が続いた構成です。レイアウトは多くの場合、両 方のホット・ループに共通するGND電流シャントによって複 雑になります。LTC®/sup>3780のデモボードDC1046A(図9)は2つ の並列ループの検出抵抗を分離する的確なソリューションを 示しています。

多少異なるSEPIC回路の図(図10)はそのホット・ループ を示しています。多くの場合、トップ・スイッチにアクティブ MOSFETの代わりにダイオードを使用します。LT3757の DC1341A(図11)は優れたSEPICのレイアウトです。緑のホッ ト・ループの面積は最小限に抑えられ、隣の層に切れ目のな いGNDプレーンを備えています。

反転トポロジー(図12)はSEPICに非常に似ており、負荷がトッ プ・スイッチとトップ・インダクタを経由しているだけです。レイ アウトは非常に簡単で、ICがLT3581、LT3757などの負帰還 電圧も制御できれば、デモボードは一般にSEPICから反転ト ポロジに変更可能です。

フライバック(図13)はトランスに個別の巻線を使用し、1次巻 線と2次巻線の間に磁気結合のみが存在します。相対的に高 いdi/dtで1次巻線の電流がゼロになり、巻線間の漏れインダ クタンスと漏れ容量内およびスイッチ・ノードに蓄積されたエネルギーのみが電流を低減します。トランスの1次巻線とその 他の巻線の電流は完全なスイッチング電流と見なすことがで きます。図8の昇降圧のケースには2つのメイン・ホット・ルー プがあります。EMIを低減するため、このトポロジーでは差動 モードEMI用のVIN近くのデカップリングに加えて、起こり得 る主な同相EMI用の同相チョークが使用されます。

その他のACループ

主にスイッチング・エネルギーを有するホット・ループは大きな RFエネルギー源になります。しかし、ICと回路を動作させるに はその他のAC伝搬ループが必要です。すべての回路はメイ ン・スイッチ・ドライバ用の電源を必要とします。降圧では多く の場合、ホット・ループと同じVINコンデンサでデカップリング します。駆動回路に個別の電圧を使用するその他のICでは多 くの場合、INTVCCコンデンサのことを指します(図14)。

INTVCCコンデンサのPGNDとGNDのループはできるだけ 小さくし、隣の層の切れ目のないプレーンでシールドします。 EMIエネルギーはメイン・ホット・ループより20dB程度小さく なります。INTVCCループに過度のインダクタンスがあると、 ICの性能が低下します。INTVCCコンデンサは、多くの場合 INTVCCからも内部給電される電流検出コンパレータ、リファ レンス、エラーアンプなどのスイッチ駆動の内部の敏感な広帯 域回路もデカップリングします。

図15は、INTVCCデカップリング・コンデンサ(図17のC2)の 電流のFFTです。

図16は、入力コンデンサ(図17のC6)の電流のFFTです。RF エネルギーはINTVCCループよりも20dB以上大きくなります。

LT8610のLTspice®回路( 図17)では、RPAR = 1Ωの高 損 失 のL2を使用し、入力コンデンサC6によってゼロ・インピーダ ンスのLTspice電圧源V1をデカップリングしています。注意: LTspiceスイッチ・モード・レギュレータ・モデルはICの機能をシ ミュレートするために開発されたものです。このモデルは内部や 外部のすべての部品や基板レイアウトを考慮していないので、 RF特性の推定には十分注意してください。しかしながら、効果 の測定が非常に困難な推定を行う優れたツールです。

外部スイッチの駆動信号

メイン・ホット・ループとINTVCCデカップリング・ループの次 の問題の要因は多くの場合、外部スイッチの駆動信号です。 最新のMOSFETでも数nF~数十nFの実効入力容量があり ます。これらのドライバの駆動電流は大抵シングル・アンプの 範囲で、立ち上がり時間と立ち下がり時間は数ナノ秒に達し ます。

図18は、図19のQ2に流れ込むゲート電流のFFTです。

緑のループ(図19)はボトム・ゲート電流の電流経路を示して います。この電流はC1から供給されます。ループは確実に小 さくなるようにします。Q2のソースのGNDからC1のGNDへ の接続は、部品層の真下の切れ目のないGND領域を使用す ることにより、最も容易に行えます。

図20の赤のループと緑のループはトップ・ゲート駆動電流の ループを示しています。これらの電流は昇圧コンデンサC2か ら供給され、コントローラICへのSW接続に戻されます。赤の ループを小さく保ち、トレースをほんのわずかなギャップで並 列に設置します。C2をコントローラICの近くに配置すると、緑 のループも小さくなります。

図21の緑のループは昇圧コンデンサの再充電を示していま す。上記のループを既に小さくしていて、D1を比較的近くに設 置していると、このループも小さくなります。

磁気アンテナやループを含むパッシブ・アンテナは交互に動 作するので、これらの送信特性と受信特性は同じです。図22 の検出アンプは、トップ・スイッチのオン・サイクルを決定する R1のシャント電圧が小さいとき、SENSE+ とSENSE–が広帯 域幅であると見なされます。

1mV以下のノイズでもデューティ・サイクルにジッタを生じま す。前記のすべての送信ループへの結合は最小限に抑える必 要があります。まず、このループで囲まれた面積も小さくする 必要があるので、SENSE+ ラインとSENSE– ラインの間のギャップを最小にします。次いで、前記の大電流ループからシール ド・プレーンの反対側のループ・トレースを設置します。十分 な数の層が利用可能な場合、PC基板層に並列なAC磁界が あまり大きくなければ、SENSE+ ラインとSENSE– ラインを重ね 合うことができます。SENSE+ とSENSE– のフィルタリングを使 用する場合、R1が常に低インピーダンスで検出入力が高イン ピーダンスなので、フィルタをコントローラICの近くに設置し ます。

図23のメイン・ホット・ループは、外付けMOSFET Q1および Q2と最も近い低インピーダンス・デカップリング・コンデンサ C7で構成されています。これはコントローラ・ソリューションで 最大のRFエネルギーを有するループです。コントローラのレ イアウトの詳細については、リニアテクノロジーの「アプリケー ションノート136」 [8] を参照してください。

シールドの機能

DC磁界は、空気、FR4エポキシ誘電体および銅箔をほとんど 遮られずに通り抜けます。

AC磁界は、導電体(一般に銅や錫など)の誘導電流によって のみ影響されます。したがって、強磁性材料を除き、電流を標 準的なPC基板環境のAC磁界の変化や減衰の唯一の要因 として位置付けることができます。

実験から、導電性の筐体がAM帯域を上回る非常に広い周 波数範囲で磁界を非常に大きく減衰する(100dBを容易に上 回る)ことが分かっています。クッキーの箱は、研究開発分野 で高周波数(HF)測定を可能にするため、敏感な回路をシー ルドするのに広く使用されている一般的な例です。高周波回 路用に、PC基板やBNC、N、SMAなどの高周波コネクタに容 易に適合する四角い形状の筐体を購入可能です。実際には、 高周波磁界は壁が表皮厚さより厚い限り、密閉された導電性 の筐体から漏れることはありません(「付録C」を参照)。

導電性の筐体をAC電流との間が平坦な壁になるほど風船の ように大きく膨らませた場合、シールド素材の渦電流は壁の 背面のオリジナルのAC電流と反対方向のAC磁界を生成す る必要があります(図24)。シールドの渦電流は筐体の外側 へのAC磁界をキャンセルするだけで十分です。つまり、この 例では図25の下側の部分に示される方向です。

シールドの効果

基板の銅箔プレーンが非導電性だとしたら、紙のようにすべ ての磁界を透過します。銅箔の電流は磁界に作用する唯一の 要因です。渦電流に利用可能なエネルギーはシールド内で誘 導されます。この電流は、表皮効果と近接効果の限界の範囲 内で、銅箔シールドの内側と誘導電流から離れる方向の外側 のすべての磁界をキャンセルします(図26)。

キャンセル層は、ホット・ループなどからの誘導電流とシール ド内で誘導される電流による磁界をキャンセルする層です。し たがって、反対方向のAC電流間の中間の層のようなもので す。キャンセル層の位置は経験則によって推定可能で、残り のAC磁界がどうなっているかを可視化できます。

キャンセル層が誘導電流層に近いほど、キャンセルが良好に なります。磁界を積分したものがインダクタンスで、この同じ磁 界が近磁界RFアンテナを形成します。これらの効果はすべて、 キャンセル層が誘導電流ループの近くに配置されるほど低減 されます。

効果の改善方法

電流がプレーンを通して戻ると、状況はいくらか異なります (図27)。この場合、プレーン内の電流は受動的に誘導され るだけでなく、能動的なリターン電流にもなります。

これはトップ・トレースの電流と同じ値になってしまいます。こ の利点は、キャンセル層が誘導トレースに近くなり、この場合、 トップ層の電流とプレーン内のリターン電流の間の中間に なることです。キャンセル層が誘導電流までの距離の半分に なったので、磁界が受動的なシールドのみの前記の状況に比 べて少なくとも1/2になったと言っても間違いありません。

可能であれば、リターン電流を最も近い層に流します。誘電体 (絶縁体)をできるだけ薄くします。リターン電流を誘導電流 に最も近いトレースに流し、誘電体距離を最小にすることが 得策です。そのために、最初から切れ目のないGNDプレーン があります。

多層基板には多くの場合、EMIを低減するための非常に薄い 外部層の誘電体があります。

ラインに誘導されるEMIの測定

図28は、フェライト・ビーズと4.7µFのセラミック・コンデンサ の入力フィルタリングを備えたLT8611のラインに誘導される 30MHz~400MHzのEMIです。–67dBmの表示線は40dBµV に相当します。

図29は、13V入力、5V/1A出力のLT8610電源のラインに 誘導される900MHzまでのEMIを示しています。図29では、 高周波シグナルチェーン内に利得が35dBの広帯域アンプ (LNA)が追加されています。したがって、スペクトラム・アナ ライザの–100dBmの表示線は–135dBmに相当し、室温で 10kHzの帯域幅を持つ50Ωシステムの熱ノイズ・フロアの値で す。LT8610/LT8611から除去する必要がある主な高周波エネ ルギーは400MHz未満です。+10dBµVは3.16µVRMSに相当 します。

EMIの最適化

まず層数をチェックします。可能であれば、4層以上のPC基 板を使用します。上面から2番目の層は一般に約200µmの距 離しかないので、シールドにより、ホット・ループが2層基板の 1mm以上離れたどのシールドよりもはるかに良くキャンセルさ れます。

ホット・ループのシールドでは、トップ・トレースのホット・ルー プと同じ電流が渦電流として流れます。第2層のシールドを切 れ目のない状態にしておきます。ノイズを少なくしておきたい場 合には、GNDプレーンに接続するためのビアをホット・ループ から離して設置します。ホット・ループのシールドをキャンセル する電流によってループと交差し高周波電圧が生成されるの で、ノイズを少なくする為、その領域にビアで結合すべきでは ありません。この電流は距離が離れるほど減衰しますが、多く の場合、問題として残ります。

(必要がある場合に)入力と出力をフィルタリングするための 課題は、主に十分にノイズの少ない領域を見つけることです。 有効な方法は、ビアで接続された電源ユニット(PSU)周囲に GNDリングを完備することです。

フィルタ・コンデンサのGNDリターンは、VIN電流がリングを 交差する位置にします。ホット・ループの方向にフィルタリン グ・インダクタンスを維持する必要があります。これにはフェラ イト・ビーズやインダクタを使用できます。

フィルタ・インダクタとメイン・インダクタの間の磁気結合に注 意してください。トランスの動作によって減衰が損なわれる可 能性があります。フィルタ・インダクタをメイン・インダクタから 離して設置します。

ブロック・コンデンサは主にインピーダンスを決定する等価直 列インダクタンス(ESL)が小さくなければならないので、0402などの短いセラミック・コンデンサやリバース・ジオメトリー・コ ンデンサを使用します。短くて厚いコンデンサほどESLが小さ くなります。説明については「付録C」を参照してください。

VINトレースとして形成するストリップラインの特性インピー ダンスは数Ωの範囲です。ブロック・コンデンサのESLはで きるだけ小さくします。リバース・ジオメトリー・コンデンサや 0402のスタックをフィルタ・ポイントの最も近くに設置し、大き なケースを近くに配置します。小さなブロック・コンデンサのト レース長は数百pHの大幅なインダクタンスの増加を生じま す。VINとリターン・トレースの配線経路はフィルタ・コンデンサ のパッドを経由するようにします。これによってトレース・インダ クタンスの増加が避けられます。

付録A

電磁界インピーダンス

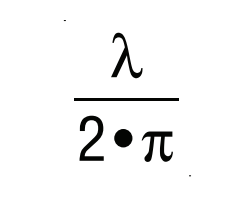

真空での光速の遠電磁場インピーダンスは約377Ω = 120π、 つまり29,9792458 • 4 • πΩです。発生源から十分に遠い電 磁波(経験値 >波長/2 • π)は磁界と電界の間に377Ωの相 関関係があります。発生源に近づくほど理想的に整合したア ンテナになる可能性があり、入力電源を正確に377Ωの電磁 界に変換します。そうでないと、大きな不整合が生じ、アンテ ナは主に磁界源または電界源として作動します。

磁界源には377Ωより小さいインピーダンスがあります。電界 源には377Ωより大きいインピーダンスがあります。図30のグ ラフは、アンテナが電界源として作動するか磁界源として作動 するかに関係なく、電磁界が次の距離で遠電磁場インピーダ ンスに安定することを示しています。

電流が非常に小さい高電圧電源でない限り、高di/dtのEMI 関連のループのインピーダンスは377Ωよりはるかに小さいの で、非絶縁型スイッチ・モード電源ユニットは主に磁界源にな ります。したがって、どの非絶縁型電源ユニットも、AC磁界を 最小限に抑えることが成功への鍵になります。

絶縁型電源には377Ωより小さいACループがあり、非絶縁 型PSU同様に磁界を最小限に抑える必要があります。ただし、 絶縁の特性により、絶縁バリアの間のインピーダンスを大きく する必要があります。大部分をトランスで実現する絶縁バリア はMΩの絶縁になるようにします。絶縁バリアにおいては、AC 電界が支配的なので異なる方策が必要です。そこで、容量性 電界結合をできるだけ小さくします。したがって、できるだけ距 離を大きくし、銅箔などのすべての導電素材の寸法を最小限 に抑えます。

付録B

ホット・ループのダイポール・アンテナ効果

ホット・ループの作用を分析する際には、磁気ダイポール・アン テナがよい手がかりになります。

ある領域の周りをAC電流が流れると一般的なダイポール・ア ンテナの磁界要素が形成されます(図31)。

ループの直径がλを大幅に下回る磁気アンテナは非常に小さ い放射抵抗を持ちます。この値はµΩ~mΩの範囲です。

PC基板の電源ユニットの標準寸法に対する放射抵抗は小さ い値(mΩ)です。放射抵抗を大きくすると、整合が改善され、 放射抵抗に比例して放出される放射線が増加します。レイア ウトに最も影響を与える可能性があるパラメータは磁気ルー プの面積です。

放出される放射線はこの面積の2乗に比例します。

付録C

表皮効果

シールドの効果を理解するためには、使用される素材の電磁 特性を少し調べる必要があります。電流は、導体を流れる流 れないにかかわらず、常に最小インピーダンスの経路を流れ ます。高い周波数では、これが最小インピーダンスの経路に なります。これは電流が損失の最も小さい経路も流れることを 意味します。導電素材は、導電素材の内部AC磁界に反発す る渦電流を生成することによってすべての内部AC磁界を最 小限に抑えます。電流密度が導体の外側方向に限られるの で、これは外部からは表皮効果のように見えます。

最初のモデルの例では、電流(I)が円柱を均一に流れると仮 定します。これはDC電流の典型例です。

電流がDCの場合、図32のようになります。Iは定数なので、こ れによるHは一定でIWはゼロです。IにAC成分がある(di/dt が存在することを意味する)場合、これによる磁界Hは変化し ます。変化する磁界Hによって誘導電圧が生成され、導体内 部では誘導電圧によって誘導電流IW(多くの場合、渦電流と 呼ばれる)が生成されます。渦電流は損失を生じます。これら の損失を最小限に抑える特性を想定する場合、これを最小 限に抑える唯一の方法は、元の均一な電流分布を変えて、す べての電流を円柱の表面だけに流すことです。

この場合、磁 界Hは円柱の表面だけに存在します。この方法では、渦電流IWが外側に移動してリターン・パスが遮断されるので、渦電 流とそれによる損失のほとんどが除去されます。

電流密度を導体の外側に移動させる力(図33)を想定できま す。

これは表皮効果と呼ばれています。ACでの無垢の円柱状の ワイヤと同じDCでの抵抗を与えるパイプの壁の厚さは、表皮 厚さと呼ばれています(図34)。電流密度を外側へ移動する力 は電磁誘導の法則から生じるものなので、周波数が増加する に従って表皮厚さは減少します。表皮厚さは、導電性が増す に従って減少し、透磁率が増すに従って減少します。

別の例を使用することができます。

図35に示すような、すべての電流が壁の表面に流れる直径 が大きなパイプの壁を想定します。このワイヤの所定の長さ(1 メータや1フィートなどの最適な値)の合計インダクタンスは、 無限大(つまり宇宙規模で想定する物理的サイズ)までの磁 界をすべて積分した値です。

ここで、パイプの直径を図35の内側の小さい方にします。磁 界は無限大までの大きい方のパイプと同じままです。ただし、 新しい小さいパイプと大きいパイプの直径の間に追加の磁界 が得られます。したがって、磁界の積分値の合計が大きくなります。このことは、所定の長さの導体のインダクタンスは導体 が薄いほど大きくなることを示しています。つまり、多くの電流 が外側の壁からワイヤの中心に移動するほどインダクタンス が増加すると想定することができます。ワイヤの両端に電圧を 印加すると、これによる電流分布はインピーダンスによって決 まります。中心のインダクタンスが大きいので、ほとんどの電流 密度は表面に移動します。抵抗がゼロの導体での表皮効果 の最も極端な例は、超電導体に見られます。超電導体の量子 効果により、すべての電流が厚さがゼロの外部層に向かうの が阻止されます。超電導体でほとんどの電流が集中する部分 の厚さはロンドン深度と呼ばれています。

いくつかの素材の周波数に対する表皮厚さのグラフを図36に 示します。

標準的なPC基板素材である銅は、5MHz~50MHzの範囲 の表皮効果の影響を受けることが分かります。また、一般的 にICで使用される厚さの高濃度にドープしたシリコンでも、 テラヘルツの領域になれば影響を受けることが分かります。銅 (Cu)と金(Au)は近接しています。高透磁率の素材(Fe-Ni) の表皮厚さは可聴周波数でも低い値です。このため、オーディ オ・トランスのシールドに使用されます

良質な導体を流れるAC電流は電流密度を外側へ強制しま す。この電流は、(インダクタンスが主な成分の)インピーダンス が最も小さいところを流れます。レイアウトと部品への表皮効 果の影響に関して、シンプルなガイドラインが得られます。短く 厚くまたは幅を広くすることが推奨されます。リバース・ジオメト リー・コンデンサは短くて厚いので、ESLは小さい値です。

付録D

近接効果

逆方向の電流が流れる場合、同じ力が電流を互いに引き付 け合います(図37)。これは近接効果と呼ばれています。

1層のPC基板のトレースの場合、高周波数の電流密度は図 38のようになります。

第2層に切れ目のないプレーンを追加すると、図39に示すよ うに、プレーンに渦電流が生じ、トップ・トレースの電流のすべ ての鏡像が生成されます。

多層基板では、プレーンがAC電流をシールドします(図40)。

付録E

EMI測定

ほとんどの電源は、発生し測定するEMI周波数の波長に比べ て比較的小さい形状です。電流電源技術を使って慎重に設 計すると、ほとんどのエネルギーが500MHz未満であることが 分かります。EMI規格は一般的でなければならず、様々なサイ ズの機器に適用する必要があります。これらは対象となる波 長の順にすることが可能です。そこで、30MHzまでのラインに 誘導されるEMIの測定値と30MHzを上回る放射EMIの測 定値が求められます。ただし、信頼できる放射測定を行うに は、大きな無響室が必要です。これらの使用料は高くて十分 に利用できません。無料の空き地はノイズが多すぎるので、大 規模で困難な設定を必要とし、天候に左右されます。

電源を最適化するための適切な方法は、放射測定に必要な スペクトラムの末端まで、ラインに誘導されるノイズの適合前 測定を行うことです。電源の寸法は対象となる波長に対して 小さいので、ほとんどのエネルギーがVINとVOUTのワイヤを 通ると想定することが可能です。そこで、これらはラインに伝導 するものとして測定できます。

設定は非常にシンプルです。LISN(ライン・インピーダンス・ス タビライザ・ネットワーク)またはAN(擬似ネットワーク)、入力 電源、負荷および測定レシーバを必要とします。

LISN(AN)は、電圧源V1を電源(またはDUT(デバイス・アン ダー・テスト))のVIN(VDUT+ 、VDUT)を絶縁するために使用さ れます。

これは自動車でよく使われる非対称LISNの例です(図41)。 このようなにシンプルな回路は、L1を空芯コイルとして構成す るか、損失のあるインダクタを使用できます。規格によっては、 様々なコアのタイプのシリーズおよび特有の巻線手法を規定 するものもあります。ただし、主目的はL1の50Ωに対する広帯 域高インピーダンスを生成することです。

C1、R1の内部配線長、VOUT_HF、およびL1のインピーダンス 以外は、使用可能な上限周波数範囲の制限となりません。し たがって、独自のものを購入するか作成してください。L1の共 振は、L1巻線の部品の両端に抵抗を終端することによって減 衰させることができます。

専用のEMIレシーバを使用することができますが、通常、スペ クトラム・アナライザで適合前測定を行います。AC結合入力 はアナライザ内部の高価なミキサを破壊させないための2次 バリアとなるので、必ずAC結合入力を使用してください。

EMI研究の専門家から、使用したEMI規格(ピーク、擬似ピー ク、必要とした比較的高精度な時定数での平均)により、必要 な検出手法について詳細な説明が得られます。電源が対象と なる負荷領域で固定周波数の動作をする場合には、この説 明を割愛することができます。固定周波数では、スイッチング 周波数の間隔の高調波(周波数コム)のみが生成されます。ス イッチング周波数が必要な分解能の帯域幅(大部分は9kHz から30MHzまでと30MHzの120kHz上まで)を上回ると、ピー ク、擬似ピーク、平均の各手法は同じ結果を示すので、使用す るレシーバの値を使用できます。規格によっては、9kHzに対 して10kHzの帯域幅を、120kHzに対して100kHzの帯域幅を 使用できます。100kHzをはるかに上回る周波数で動作する固 定周波数のスイッチングPSUの誤差は、適合前測定との相関 がありません。

システムにプロセッサが含まれている場合、上記の分解能の 帯域幅内に十分に入る周波数成分で大きく変動する電流が 生じる可能性があります。

この場合、規格が要求するフィルタ手法に戻す必要があります。

スイッチング周波数の一部か、またはスイッチング周波数に相 当する整数で割り切れない成分が観測される場合、オシロス コープでスイッチ・ノードをチェックしてください。時間領域で は、パルス・スキップまたは低調波発振が観測される可能性 があります。作業を進める前にこの挙動の要因をチェックして ください。プローブを付けてEMI測定を行うと、プローブ・ア ンテナへの追加誘導によって間違った結果を得るので、オシ ロスコープのプローブを外すことを忘れないでください。

参照

[1] http://www.conformity.com/past/0102reflections.html

[2] http://www.ece.msstate.edu/~donohoe/ece4990notes5.pdf

[3] http://de.wikipedia.org/wiki/Skin-Effekt 1.3.2011

[4] Rudnev, Dr. Valery I.; Heat Treating Progress; Oct. 2008

[5] Archambeault,Bruce R.; PCB Design for Real-World EMI Control; 2002

[6] Williams, Tim; EMC For Product Designers; Second Edition; 1996

[7] Johnson Howard, Graham, Martin; High Speed Digital Design A Handbook Of Black Magic; 1993

[8] Zhang, Henry J.; PCB Layout Considerations For NonIsolated Switching Power Supplies; AN136; www.linear.com

[9] Ott, Henry W.; Electromagnetic Compatibility Engineering; Wiley; 2009