Overview

説明

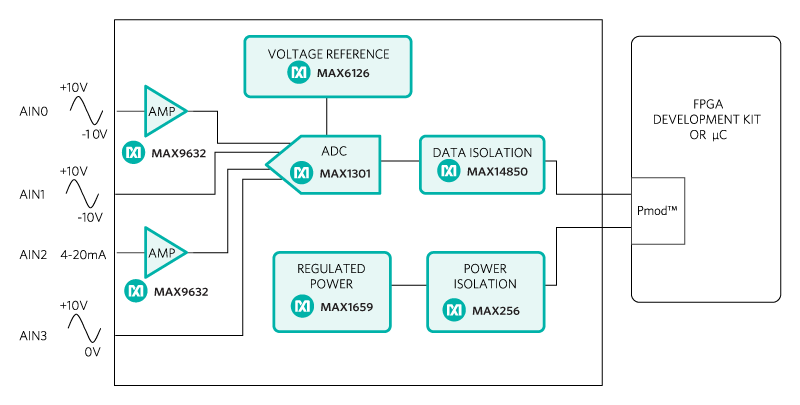

アナログ-デジタルコンバータ(ADC)を内蔵した最近のFPGA (field programmable gate array)およびマイクロコントローラは、低分解能で低電圧のアナログ入力に対応します。しかし、産業用制御および産業用オートメーションアプリケーションの必要を満たすには不十分であり、多くの場合、絶縁型の、より高分解能で、より高電圧のシステムソリューションが必要になります。Santa Fe (MAXREFDES5)サブシステムリファレンスデザインは、-10V~+10V、0~10V、および4~20mAの電流ループ信号を許容する16ビット高精度産業用アナログフロントエンド(AFE)で、絶縁された電源とデータを小型基板に集約しています。Santa Feデザインは、ローノイズハイインピーダンスアナログバッファ(MAX9632)、革新的なアッテネータを内蔵した高精度ADC (MAX1301)、超高精度4.096V電圧リファレンス(MAX6126)、600VRMSデータアイソレーション(MAX14850)、および絶縁型/安定化+12V、-12V、および5V電源レール(MAX256/MAX1659)を統合しています。このAFEソリューションは、高精度アナログ-デジタル変換を必要とするあらゆるアプリケーションで使用することができますが、主として産業用センサー、産業用オートメーション、プロセス制御、プログラマブルロジックコントローラ(PLC)、および医療アプリケーションを対象としています。

機能と利点

アプリケーション

- 高精度

- ±10V、0~10V、および4~20mA入力

- 絶縁された電源とデータ

- 小型のプリント基板(PCB)

- デバイスドライバ

- Cのソースコード例

- Pmod™対応形状

- 産業用センサー

- プロセス制御

- 産業用オートメーション

- PLC

- 医療

Details Section

Documentation & Resources

-

UG-5886: Santa Fe (MAXREFDES5#) MicroZed Quick Start Guide2015/04/06PDF1M

-

UG-5639: Santa Fe (MAXREFDES5#) ZedBoard Quick Start Guide2013/04/22PDF857K

-

UG-5578: Santa Fe (MAXREFDES5#) Nexys 3 Quick Start Guide2013/02/04PDF861K

-

ラピッド・プロトタイピングを実現するためのソリューション2024/04/15PDF4 M

Support & Training

Search our knowledge base for answers to your technical questions. Our dedicated team of Applications Engineers are also available to answer your technical questions.