The Fundamentals of LDO

The Fundamentals of LDO Design and Applications

- ADIsimPower Design Tool (Web)

- ADI Linear Regulator Design Tool and Parametric Search (Download)

- The Fundamentals of LDO Design and Application (pdf)

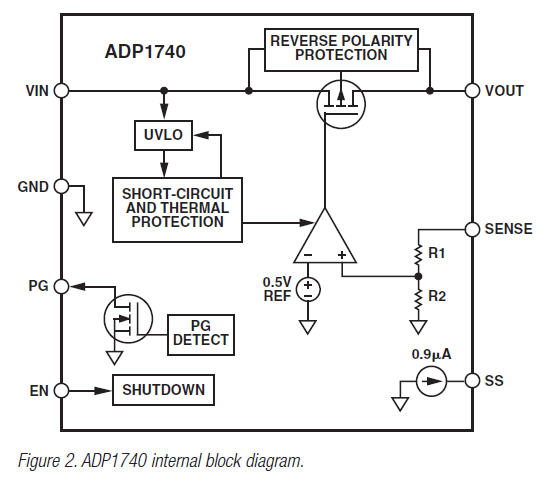

A low dropout regulator (LDO) consists of a voltage reference, an error amplifier, a feedback voltage divider, and a series pass element, usually a bipolar or CMOS transistor (see Figure 1). Output current is controlled by the PMOS transistor, which in turn is controlled by the error amplifier. This amplifier compares the reference voltage with the feedback voltage from the output and amplifies the difference. If the feedback voltage is lower than the reference voltage, the gate of the PMOS device is pulled lower, allowing more current to pass and increasing the output voltage. If the feedback voltage is higher than the reference voltage, the gate of the PMOS device is pulled higher, allowing less current to pass and decreasing the output voltage. This is a closed-loop system based around two main poles, the internal pole of the error amplifier/pass transistor and the external pole of the output capacitor’s equivalent series resistance (ESR).

Analog Devices LDOs are designed to be stable over the specified operating temperature and voltage ranges when the recommended capacitors are used. The ESR of the output capacitor affects the stability of the LDO control loop. A minimum ESR of 1 Ω or less is recommended to ensure stability. The LDOs response to rapid changes in load current, i.e. the transient response, is also affected by output capacitance. Using a larger value of output capacitor improves the transient response of the LDO; however, it can increase the start-up time.

LDO regulators are used to derive lower output voltages from a main supply or battery. The output voltage is ideally stable with line and load variations, immune to changes in ambient temperature, and stable over time. LDOs should have as low a difference between the input and output voltage as possible, called the dropout voltage. For example, in a battery-powered design using a lithium-ion cell connected to a 2.8 V LDO, the battery voltage can drop from 4.2 V (fully charged) to 3.0 V (battery empty) and provide a constant 2.8 V output provided the LDO’s dropout voltage is below 200 mV. In some systems LDOs are used for postregulation. The LDO connects to the output of a high-efficiency switching regulator and provides noise filtering, as well as a constant and stable output voltage.