概览

设计资源

评估硬件

产品型号带"Z"表示符合RoHS标准。评估此电路需要下列选中的电路板

- MAXREFDES44# ($26.20) Secure Authentication Design with 1-Wire ECDSA and Xilinx Zynq SoC

描述

概述

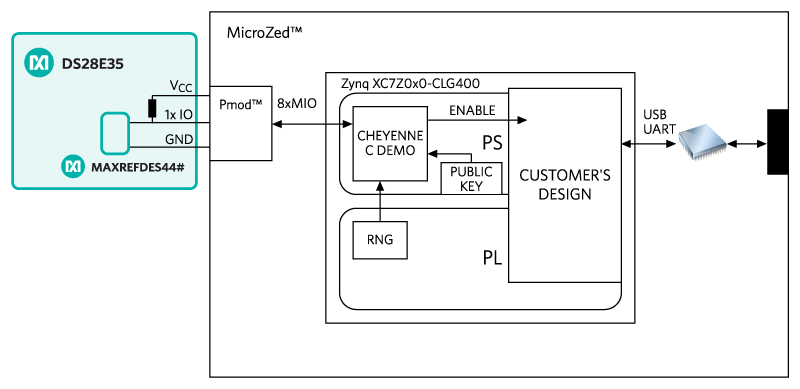

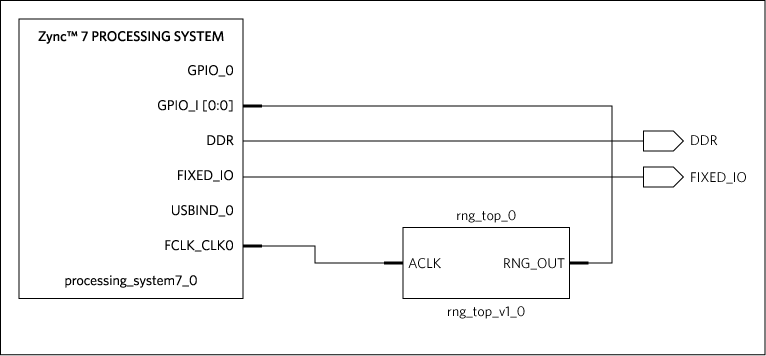

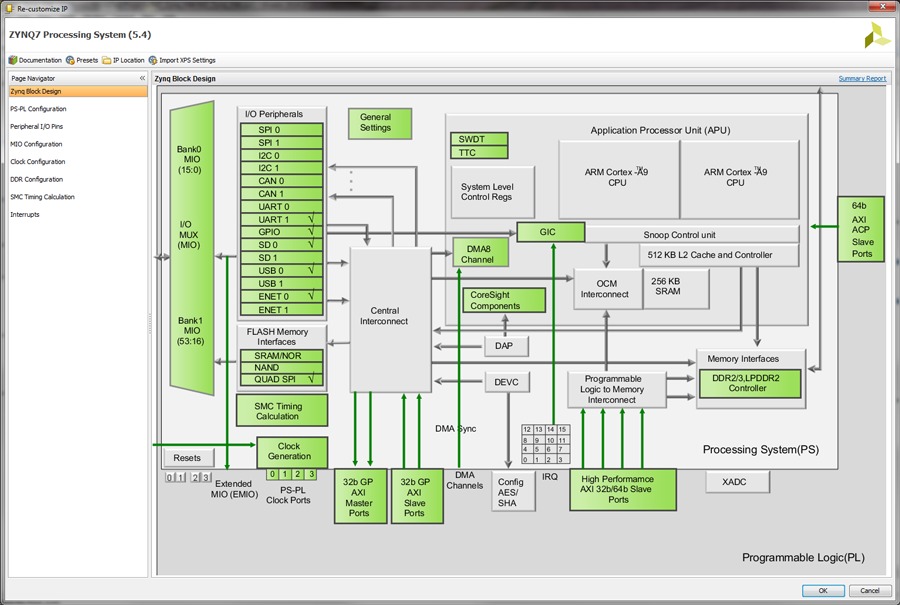

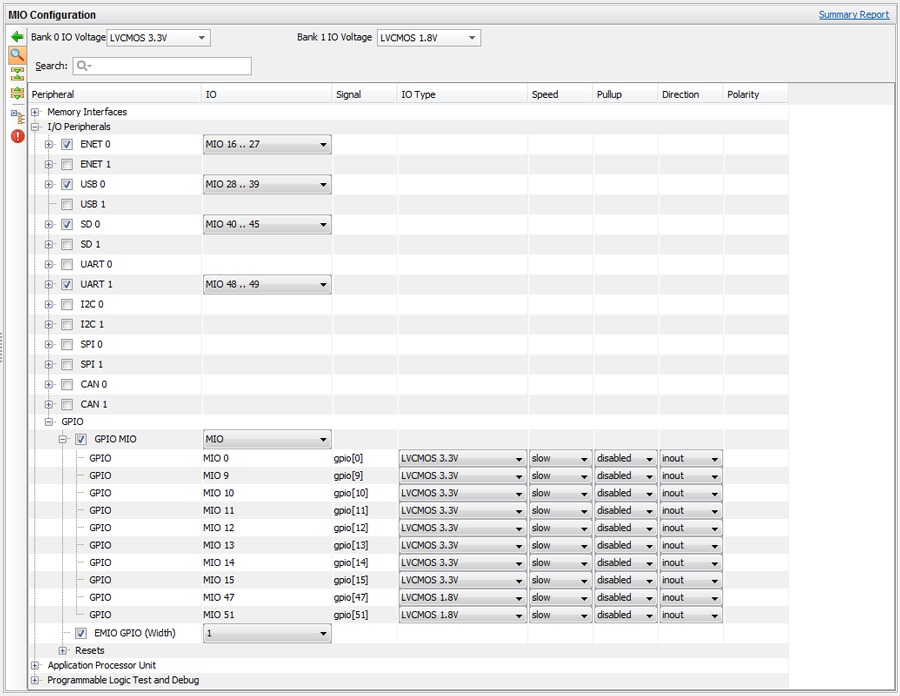

MAXREFDES44#是一款基于1-Wire®的身份验证参考设计,旨在保护IP并对Xilinx Zyn™ FPGA的外设进行身份验证。使用提供的示例代码,系统借助DS28E35执行不对称质询-响应序列,以确保模块、外设或子系统的真实性。DS28E35通过Maxim Integrated的1-Wire总线进行通信。MAXREFDES44#配备了Pmod™连接器,可使用Avnet MicroZed™板进行即时测试。这种简单设计便于快速集成到任何需要通过非对称ECDSA算法进一步提高安全性的外设中。

更多信息,请参阅“详情”标签页。可从“设计资源”标签页下载设计文件,包括原理图、PCB文件和物料清单(BOM)。在签署保密协议后,可根据要求提供固件。

注:对MAXREFDES44#进行编程需要单独购买DS28E35EVKIT#。

优势和特点

特征

- ECDSA安全认证

- 1-Wire接口

- 源代码示例

- Pmod兼容规格

竞争优势

- 强加密安全认证

- 带硬件加速,实现快速性能

- 外设安全认证不要求VCC引脚

重要通知及免责声明

请阅读关于ADI设计信息和资源的参考设计免责声明。

所用产品

详情

文件和资源

-

MAXREFDES44 设计文件2021/2/17ZIP594K

支持与培训

搜索我们的知识库,获取技术问题答案。我们专门的应用工程师团队也会随时为您解答技术问题。