配合DS34S132使用的DDR3存储器模块

Abstract

本应用笔记介绍了如何连接DS34S132 (32端口TDM-over-packet IC)与DDR3存储器芯片。DS34S132采用外部双数据速率(DDR)同步DRAM (或DDR1)存储器缓存数据。内存空间需提供足够的缓存区域,以支持256条伪线(PW)/绑订中每一伪线的256ms数据包延迟变化(PDV),确保接收数据包的重新排序。

引言

DS34S132 32端口TDM-over-packet IC采用外部双数据速率(DDR)同步DRAM (也称为“DDR1”)存储器缓存数据。内存空间需提供足够的缓存区域,以支持256条伪线(PW)/绑订中每一伪线的256ms数据包延迟变化(PDV)。如果数据包交换网络(PSN)没按正确的先后次序排列数据,存储器需确保对接收数据包的重新排序。由于目前DDR3已成为主流存储器件,为了使DS34S132更方便地采用DDR3,本应用笔记介绍了如何实现DS34S132与DDR3存储器的对接。

图1所示为利用FPGA和DDR3取代DDR1的推荐电路框图。

图1. 用DDR3和FPGA取代DDR1

借助DDR SDRAM数据信号与时钟信号的混合时序控制,DDR SDRAM接口能够支持速率高于典型SDRAM数据传输。例如,一个125MHz时钟频率的DDR SDRAM,可以实现同等频率SDRAM几乎两倍的带宽(BW)。因此,Maxim开始在其方案中用DDR1取代SDRAM,SDRAM用于Maxim的上一代TDM over Packet (TDMoP)器件。

DDR3 SDRAM采用的是DRAM接口规范。实际的DRAM存储数据阵列的存储架构与早期类型相似,具有相似的性能指标。DDR3 SDRAM的数据传输速率是DDR1的4倍,具有更宽频带。

目前,DDR1存储器模块的使用不如DDR2或DDR3广泛。但DDR2和DDR3向下、向上都不兼容DDR1。因此,DDR2或DDR3存储器模块不能工作在早期采用DDR的主板设计中,反之亦然。

DS34S132的DDR接口配置

针对DS34S132 TDMoP器件内部配置:

- DDR1接口必须设置成3类列地址选通(CAS)。

- 必须计算“刷新频率”,针对DDR3存储模块配置足够快的时间间隔。

- DDR时钟频率为125MHz。

值得注意的是,DDR3有8个扇区,DS34S132只有2个扇区选择位。因此,其中一半的DDR3存储器模块(上区)没有使用。

DDR3配置

DDR3应该运行在500MHz时钟速度,该频率是DDR1 125MHz时钟频率的四倍。

我们采用8位数据进行Verilog® RTL仿真,BW为:500MHz × 2 × 8位。该BW是125MHz × 2 × 16位DDR的两倍,额外的BW用作从DDR3流水线回传数据给DS34S132,不需占用FPGA的FIFO存储器。对于DDR3,我们使用以下配置:

- CAS延迟:8

- CAS写延迟:6

- DLL复位,然后再使能。

我们用Micron DDR3 MT41J128M8 (16M × 8 × 8扇区)进行仿真。当CL = 8 (DDR3 - 1066) - 187时,DDR3的周期是1.87ns。如需支持其它DDR3配置/速度,可能还需提升资源配置。我们使用的DDR3仿真具有以下规格:

'elsif sg187 // sg187 is equivalent to the JEDEC DDR3-1066G (8-8-8) speed bin eter TCK_MIN 1875; // tCK ps Minimum Clock Cycle Time eter TJIT_PER 90; // tJIT(per) ps Period JItter eter TJIT_CC 180; // tJIT(cc) ps Cycle to Cycle jitter eter TERR_2PER 132; // tERR(2per) ps Accumulated Error (2-cycle) eter TERR_3PER 157; // tERR(3per) ps Accumulated Error (3-cycle) eter TERR_4PER 175; // tERR(4per) ps Accumulated Error (4-cycle) eter TERR_5PER 188; // tERR(5per) ps Accumulated Error (5-cycle) eter TERR_6PER 200; // tERR(6per) ps Accumulated Error (6-cycle) eter TERR_7PER 209; // tERR(7per) ps Accumulated Error (7-cycle) eter TERR_8PER 217; // tERR(8per) ps Accumulated Error (8-cycle) eter TERR_9PER 224; // tERR(9per) ps Accumulated Error (9-cycle) eter TERR_10PER 231; // tERR(10per)ps Accumulated Error (10-cycle) eter TERR_11PER 237; // tERR(11per)ps Accumulated Error (11-cycle) eter TERR_12PER 242; // tERR(12per)ps Accumulated Error (12-cycle) eter TDS 75; // tDS ps DQ and DM input setup time relative to DQS eter TDH 100; // tDH ps DQ and DM input hold time relative to DQS eter TDQSQ 150; // tDQSQ ps DQS-DQ skew, DQS to last DQ valid, per group, per access eter TDQSS 0.25; // tDQSS tCK Rising clock edge to DQS/DQS# latching transition eter TDSS 0.20; // tDSS tCK DQS falling edge to CLK rising (setup time) eter TDSH 0.20; // tDSH tCK DQS falling edge from CLK rising (hold time) eter TDQSCK 300; // tDQSCK ps DQS output access time from CK/CK# eter TQSH 0.38; // tQSH tCK DQS Output High Pulse Width eter TQSL 0.38; // tQSL tCK DQS Output Low Pulse Width eter TDIPW 490; // tDIPW ps DQ and DM input Pulse Width eter TIPW 780; // tIPW ps Control and Address input Pulse Width eter TIS 275; // tIS ps Input Setup Time eter TIH 200; // tIH ps Input Hold Time eter TRAS_MIN 37500; // tRAS ps Minimum Active to Precharge command time eter TRC 52500; // tRC ps Active to Active/Auto Refresh command time eter TRCD 15000; // tRCD ps Active to Read/Write command time eter TRP 15000; // tRP ps Precharge command period eter TXP 7500; // tXP ps Exit power down to a valid command eter TCKE 5625; // tCKE ps CKE minimum high or low pulse width eter TAON 300; // tAON ps RTT turn-on from ODTLon reference eter TWLS 245; // tWLS ps Setup time for tDQS flop eter TWLH 245; // tWLH ps Hold time of tDQS flop eter TWLO 9000; // tWLO ps Write levelization output delay eter TAA_MIN 15000; // TAA ps Internal READ command to first data eter CL_TIME 15000; // CL ps Minimum CAS Latency

FPGA配置

FPGA的关键性能:

- 在上电时,初始化DDR3存储器芯片。

- 初始化完成后,把从DS34S132发出DDR1命令转换成DDR3命令/数据。

- i. 读

- ii. 写

- iii. 预充电

- iv. 使用数字时钟模块(DCM)对DS34S132的DDR1时钟(125MHz)进行4倍频,生成DDR3时钟(500MHz)。

- v. 使用第二个DCM产生四个不同的相位DDR3时钟,提供DDR3沿触发时序。此外,利用一路反馈时钟(从一个IO端输出并返回)调整这些时钟相对于DDR1时钟沿的相位关系,有助于DS34S132及时读取数据。

据此,FPGA与DDR3存储器相结合,构成类似于DS34S132的DDR1功能。FPGA代码包括DCM和早期的DDR IO。可从这里下载程序和详细说明。

FPGA采用Spartan,Verilog RTL仿真速度等级为-4,能够达到500MHz。FPGA选用接近300的触发器,不带FPGA RAM。我们还使用了两个DCM转换时钟频率。为了验证DDR1 - DDR3转换设计方案,在Verilog RTL仿真器进行以下测试:

- DDR1模式测试并记录结果。

- 通过FPGA测试DDR3模式,并记录结果。

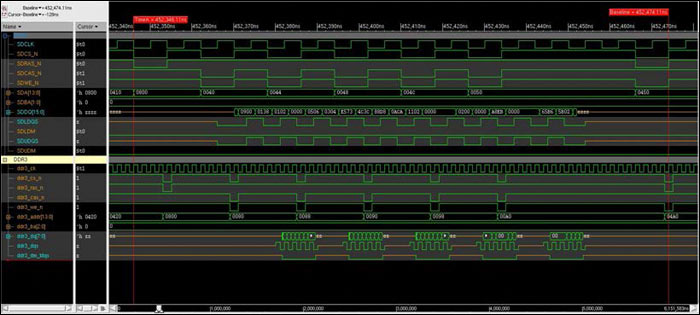

- 监测DDR3独立的读、写操作,并与DDR1读、写操作进行对比。图2和图3显示了DDR1和DDR3的读、写仿真结果。

在Verilog RTL仿真中,可以成功地通过FPGA从DDR3向器件发送有效信号。同样也可成功地读取器件信号并发送到DDR3。仿真结果证明,从DDR1到DDR3转换方案可以正确工作。

图2. DDR1 (上图)和DDR3 (下图)的写操作仿真结果

图3. DDR1 (上图)和DDR3 (下图)的读操作仿真结果

结论

本文利用Micron DDR3 MT41J128M8参数模型进行FPGA的Verilog RTL仿真,确保器件能够配合DDR3和Spartan FPGA工作。但该方案并不适用于所有DDR3器件,设计人员需要首先了解利用哪些DDR3进行设计。没有提供FPGA映射和位文件。

有关TDMoP器件或其它Maxim电信产品技术支持,请联络:术支持团队。