AN-737: 如何用ADIsimADC完成ADC建模

转换器建模

转换器建模经常被忽视、忽略或者采用理想的数据转换器模型来完成。随着越来越多的系统使用混合信号技术,系统建模的重要性不断提高。日益缩短的设计周期和“一次成功”的压力,进一步凸显了完整系统建模的重要性。ADIsimADC™正是为回应这一不断增长的需求而开发。

理想转换器模型常常用于功能建模,但它们无法提供所需的详细性能信息,从而无法确定特定器件是否符合系统目标。解决这一问题是ADIsimADC开发的初衷。ADIsimADC使用户第一次拥有了在系统中验证特定转换器的性能,从而利用其条件确定所选器件是否适用的手段。虽然ADIsimADC并不模拟ADC的每一个特性,但它对于实现让用户能够在其系统仿真中模拟真实转换器这一目标意义深远。

位精确模型与行为模型

位精确模型是这样一种模型,如果提供已知的激励,它将产生已知的、可预测的输出。ADIsimADC不是位精确模型。此类模型常见于数字系统。处理模拟功能时,对于给定的输入,由于噪声、失真和其它非线性因素的影响,从来不存在一个已知的响应。虽然响应的一部分可能是可以预测的,但大部分要受到失真、噪声甚至器件间差异的影响。此外,位精确模型要求提供用来处理瞬态响应的电路仿真文件,如SPICE模型等。然而,这些模型庞大而复杂,处理速度非常慢,最终只能提供有限的精度。缩小或等效的SPICE模型可降低复杂性,但无法充分模拟静态和动态性能的精致细节。

行为模型不仅消除了复杂性问题,而且能够模拟电路文件所无法获得的精致性能细节。ADIsimADC与VisualAnalog™一起构成独立的转换器仿真工具。ADIsimADC™也可以配合许多其它第三方仿真工具使用,包括Agilent Technolo-gies的ADS、Applied Wave Research, Inc.的VSS、National Instrument的工具以及MATLAB®和C++。有关这些工具的使用信息,请访问: www.analog.com/ADIsimADC。

模型与硬件

系统或ADC的建模绝不应代替真实系统的构建和表征。电路建模是一码事,实际构建并测试电路则是另一码事。

与任何模拟或混合信号器件一样,要实现仿真所显示的性能,必须采用正确的布局布线和配置。因此,必须遵循产品数据手册所述的所有布局布线规则和指导原则(见图4)。举例来说,为电源提供充足的旁路电容就很重要。混合信号器件包括一定量的数字电路,因此数字切换噪声常常是一个问题,如果不提供电容来控制这些开关电流,则即使最佳器件的性能也会大大降低。转换器周围经常需要其它支持器件,包括附加电容、电感和电阻。要知道需要哪些器件,最好的办法是查阅产品数据手册和评估板原理图。

哪些特性需要建模?

ADIsimADC旨在提供真实器件的实际性能。哪些特性需要建模取决于用户打算执行何种分析。例如,控制环路需要精确的传递函数和延迟信息,而无线电系统则可能需要噪声和失真的精确表示。ADIsimADC能够模拟数据转换器的许多关键特性,包括失调、增益、采样速率、带宽、抖动、延迟、交流和直流线性度等。(欲了解有关交流线性度的更多信息,请参阅应用笔记AN-835:“了解高速ADC测试和评估”。)

本应用笔记将详细说明这些特性以及ADIsimADC如何对待它们。

增益、失调和直流线性度

转换器的满量程范围由设计决定,它可以是固定的、可选的或可变的。转换器的增益误差是与标称值(常常称为输入范围)的偏差。ADC是电压输入器件,因此满量程范围用直流或低频下的输入电压范围(伏特)表示。

失调是指实际主载波转换与转换器满量程范围一半的偏差,可以通过将输入短路至满量程的一半进行测量。许多器件都有内部连接来偏置输入引脚,以便设置输入共模电压(见图1)。对于此类器件,不需要在外部形成此连接。单端输入时,输入端可以悬空;差分输入时,输入端可以短路连在一起。内部未连接到共模电压的器件必须采用外部连接(见图2)。与输入范围一样,共模电压可以是固定的或者可调的。在确定其配置时,请查阅器件数据手册。

ADIsimADC不允许改变输入范围或共模范围。针对具有多个输入范围的器件,它可提供不同的转换器模型。共模范围对于所有器件都是固定的,无法更改。如果希望使用不同的共模范围进行系统建模,可以用一个外部偏置减去差值。

ADC的直流线性度(见图3)由量化方法和转换器的静态传递函数确定。转换器有许多类型,每种类型都有其独特的传递函数,在直流和高频时会产生不同的结果。有关不同类型转换器以及传递函数如何影响转换器性能的更多信息,请查看参考文献部分中的Brannon(2001)和Kester(2004)文献。

采样速率

转换器性能随着采样速率和模拟输入频率的改变而变化。就采样速率而言,从最小到最大额定采样速率,大多数优良的转换器都能提供一致的性能(见图5)。当采样速率低于最小值时,一些转换器无法正常工作。这可能是由于片内电容所储存的电荷放电或减少,导致数据转换出错。因此,应查询转换器数据手册以确定最小可用采样速率。在最大采样速率以上,可能会出现以下两个问题中的一个。其一是器件可能无法将片内数字信号从一级传递到下一级,原因是片内建立或保持时间不够用。其二是关键模拟信号无法在所分配的时间内稳定下来,保持电容的采集时间便是一例。同样,应查询转换器数据手册以确定最大采样速率。ADIsimADC利用额定采样速率确定转换器的性能。在器件的额定范围之外,模型产生全0结果。

带宽

随着模拟输入频率的提高,幅度响应的衰减会实际上增大了转换器的视在满量程范围,导致转换器的响应滚降。响应降低3 dB时的频率称为转换器的3 dB带宽。

随着模拟输入频率的提高,转换器性能根据其频率响应而滚降(见图6)。ADIsimADC对此进行了模拟,模型中的响应相应地降低。为抵消此损耗,输入信号幅度必须提高到模型的默认范围以上,导致输入似乎高于转换器的满量程范围。实际上,此信号会被封装和器件的寄生效应以及采样保持放大器(SHA)的保持电容形成的滤波器所衰减,因而仍然在规定的范围以内。

失真:动态和静态

ADC的带宽是有限的,因此也存在固有压摆率限制,或者称动态限制。此压摆率限制是ADC内部的失真来源之一。当数据转换器的输入频率从DC扫描到某一较高频率时,转换器的SFDR和谐波性能会下降(见图7)。

由于失真限制至少部分归因于压摆率问题,因此可以在保持模拟频率恒定的同时降低输入信号的幅度,导致相对于转换器的满量程而言,压摆率得以降低,谐波和失真性能得以改善。虽然这些杂散并不总是遵循n阶产物的典型趋势,但是经常可以微弱地观察到这一趋势。随着信号电平降低,动态效应减小,但静态效应会迅速取代动态效应而成为失真的主要因素。静态失真是由转换器的传递函数所引起的失真(见图8)。这种失真常常产生一些不可预测的结果,包括杂散随着输入电平而迅速变化,而且还可能同时表现出正负斜率特性。大部分杂散要归因于转换器的架构特征。不同的 转换器具有不同的静态传递函数,导致非常不同的失真响应。此外,由于是模拟器件,采用同一设计的每个器件对输入信号都会表现出不同的响应。因此,不同器件之间会有一些差异。

ADIsimADC致力于模拟数据转换器的标称性能。虽然它能出色地完成工作,但器件间的一些差异在所难免。欲确定可能会有何种性能差异,请参阅转换器数据手册。

抖动

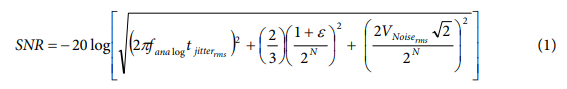

除了转换器的模拟输入压摆率限制之外,对高频模拟信号进行采样最棘手的问题之一是抖动。抖动指在每个数据转换器的前端的采样过程中样本与样本之间的差异。模拟输入频率较低时,抖动可以忽略不计。然而,当模拟输入频率较高时,抖动引起的模拟采样过程误差会导致转换器性能显著降低(见图9)。虽然采样时间误差可能只有几飞秒,但由此产生的对信噪比的性能限制可能很大(参见ADI公司网站www.analog.com上的应用笔记AN-501:“孔径不确定度与ADC系统性能”)。虽然影响整体噪声的因素有多个,但在高频时,抖动显然是主要因素,特别是对于高分 辨率转换器,如方程式1所示。

抖动有两个来源。一是器件本有的或内部抖动。多数现代转换器设计人员都会想方设法降低内部抖动,因此内部抖动在两种抖动中通常较小(但不是可以忽略不计)。第二个同时也是主要的抖动来源是外部时钟抖动。当模型计算抖动引起的噪声时,这两个抖动源会先行合并。

ADIsimADC估计输入信号的瞬时压摆率,然后将其乘以高斯模型抖动噪声源,西格玛(Σ)等于内部和外部抖动的合并均方根值。结果就是抖动的噪声贡献,它精确模拟了抖动作为模拟输入频率和幅度水平的函数的影响。外部抖动的默认值是器件表征期间所用设置的默认值。不过,用户可以将它设为任意值。

延迟

许多类型转换器的采样时间与有效数据出现在数字输出上的时间之间存在一定的延迟。SAR和Flash转换器一般在采样周期结束后立即提供输出数据。多级转换器,如流水线和Σ-Δ型转换器等,经过许多时钟周期才提供一个输出。对于延迟是重要考虑的控制系统和其它系统,这是一个问题。ADIsimADC根据时钟周期的整体值来模拟延迟,这会导致在转换周期开始时(同时填充流水线)产生无效数据,并且在转换周期结束后(同时刷新流水线)产生有效数据。使用模型时,必须通过刷新缓冲器或者其它方式来正确处理流水线延迟。

结论

ADIsimADC是用于模拟特定工作条件下的ADC性能的有用工具。这款软件能够模拟现实条件,支持更完整的系统建模。虽然它不能取代硬件,但却可以作为一个很好的起点,帮助用户了解ADC在系统设计中如何工作。

参考文献

Brannon, Brad. 2006. AN-501 Application Note Aperture Uncertainty and ADC System Performance. Analog Devices, Inc. (March).

Brannon, Brad. 2001. “DNL and Some of Its Effects on Converter Performance.” Wireless Design and Development (June).

Brannon, Brad and Rob Reeder. 2006. AN-835 Application Note Understanding High Speed ADC Testing and Evaluation. Analog Devices, Inc. (April).

Kester, Walt, ed. 2004. Analog-to-Digital Conversion. Analog Devices, Inc. ISBN 0-916550-27-3.

Looney, Mark. Analog-to-Digital Converter (ADC) Signal-to-Noise Ratio (SNR) Analysis. Unpublished paper.