资源库

AN-1393: 将系统级保护和测量要求转换成ADC规格

简介

本应用笔记提供指南,概述如何将输配电应用的系统级要求转换成ADI数据手册中提供的模数转换器(ADC)规格。这些指南描述了测量和保护设备对系统级性能的影响。本应用笔记使用 AD7779作为参考。但是,本应用笔记介绍的一般原则适用于ADI的所有ADC。

系统级要求

尽管系统级规格因应用而异,但是一些关键要求可运用至大部分应用,包括最大和最小标称工作电流 (INOM) 和精度规格。精度通常取决于测量或保护标准,规定了电流、电压或电能测量值的特定百分比误差。

主要规格

ADC或数据采集系统(DAQ)的交流或动态性能表示为给定输入频率和采样速率 (fS) 或输出数据速率(ODR)下的SNR、SINAD和THD。这些主要规格和描述如下所示:

- 信噪比(SNR)指实际输入信号的均方根值与奈奎斯特频率以下除谐波和直流以外所有其它频谱成分的均方根和之比。SNR用dB表示。

- 动态范围(DR)指DAQ/ADC产生的最大输入信号与最小输入信号之比。DR用dB表示。

- 信纳比(SINAD)指实际输入信号的均方根值与奈奎斯特频率以下包括谐波但排除直流的所有其它频谱成分的均方根和之比。SINAD一般用于衡量ADC或DAQ信号链的测量分辨率。SINAD用dB表示。

- 总谐波失真(THD)指前五个谐波成分的均方根和与满量程输入信号的均方根值之比。THD用dB表示。

有关主要规格的详情,请参见 MT-003:解SINAD、ENOB、SNR、THD、THD + N和SFDR,不在噪底中迷失。

下述两种情形可能需要高DR:

- 需要将输入范围中的信号解析成高精度。

- 需要以适当的精度测量变化范围大的信号。

通过不同的信号链设计实现DR,信号链设计将在“信号链实现”部分进行进一步讨论。

转换各种规格

要确定DAQ或ADC需要什么样的性能水平,可分析以下要求:

- DAQ/ADC的工作输入范围。

- 输入范围内的精度要求。

“输入范围”部分将说明如何计算这两个要素的影响。

输入范围

计算测量输入范围所需的DR的方式是使用ADC必须测量

的最大和最小电流(或电压)之比。输入范围的DR(DR 输入范围) 通过下式计算:

| DR输入范围 | = | 最大电流 (A) |

|

|

||

| 最小电流 (A) |

为了允许不确定性,此输入范围的上限通常需要留出设计裕量。

使用相同的步骤,通过最大和最小电压输入计算电压通道 的DR。下式用于将输入范围的DR转换成用dB表示的值 (DRInput Range (dB))。

| DRInput Range (dB) | = | 20 × log10 (DR) |

请注意,以上公式假定最大电流可直接用最大ADC输入电压衡量。

如果并非如此,则需要在DR上留出额外的裕量,以对未使用ADC的满量程输入范围进行补偿。

精度

系统精度指测量值的允许误差。通常,系统精度用相对于测得信号的百分比误差表示,例如:整个工作范围内误差为0.5%。

或者,也可以将精度表示为相对于标称信号或的百分比误差或绝对值。要将此要求转换成DR值,使用的最小输入处的百分比误差如下式所示:

| DRAccuracy (dB) | = 20 × log10 | ( | 1 | ) |

|

|

||||

| 百分比误差 |

其中,DRAccuracy (dB) 指达到指定精度所需的DR。

必须注意,理想精度必须在指定测量时间内实现,在DAQ/ADC的每个输出样本中并非必要。例如,在保护应用中,算法可能使用所有从AD7779收集到的样本,并将样本在半个电力线路周期上进行平均,以得到最终结果。在计量应用中,测量周期可能大幅延长。例如,rms读数可能在10个电力线路周期过后更新。在这种情况下,作为ADC的AD7779会在整个周期内产生多个样本,这些样本可以取平均值。平均或过采样过程的结果会降低本底噪声。本底噪声降低的数值取决于整个测量周期内可用的ADC样本数量,如下式所示:

| DRAveraging (dB) | = | 20 × log10 √No_Samples |

其中:

DRAveraging (dB) 指通过在 No_Samples(dB)范围内取平均值实现的DR降低量(dB)。

No_Samples 指在测量时间内产生的ADC输出样本的数量。

要计算样本数(No_Samples),需要用到AD7779 ODR。AD7779可实现的输出数据速率最高为16 kSPS。参见下式:

| No_Samples | = | ODR (SPS) × 测量时间 (sec) |

通过取平均值得到的正DR净值可得出 DRAccuracy (dB) )规格的降低量,因此该值必须通过对DR取平均值重新计算。

| DRAccuracy (dB) | = | DRAccuracy (dB) – DRAveraging (dB) |

得到的DAQ/ADC性能要求

最终的DAQ/ADC DR规格通过将输入范围的DR贡献添加至精度DR进行确定。

| DRFinal | = | DRInput Range (dB) + DRAccuracy (dB) |

总谐波失真(THD)的影响

求平均值计算假定AD7779的噪声随机且在频谱中均匀分布。但是,系统中实际上还会存在一定程度的谐波噪声。因为每个ADC输出样本中相同频率处都存在谐波成分,简单的求平均值不会降低此噪声。求平均值可使系统受益的程度受THD限制。因此,在选择ADC时必须注意THD参数。THD用于衡量谐波成分,指前五个谐波成分的均方根和与满量程输入信号的均方根值之比。ADC的THD参数必须低于SNR/DRFinal 值才能满足系统要求。如果THD较高,系统性能会受THD的值限制。对于AD7779,−0.5 dB信号的THD为−108 dB。ADC输入信号的幅度减小时THD会增大,保护和测量应用中通常都会出现这种情况。

保护和测量

大部分输配电应用都需要保护和测量这两种功能。这两种功能在精度和有效额定范围方面可能有不同的要求。确定合适的DAQ/ADC以满足这些要求时,应单独评估各种要求。请按照“空气断路器示例”部分所述,使用最高规格选择合适的ADC。

空气断路器示例

下例演示了将空气断路器(ACB)的系统级性能转换成ADC要求的过程。在这个特殊例子中,ACB中包含一个计量单元;因此,存在一系列独立的计量和保护规格。

系统级规格示例

表1显示了计量和保护规格的示例。

| 参数 | 计量 | 保护 |

| 精度 | 0.5% | 2% |

| 最小电流 | 5 A | 40 A |

| 最大电流 | 6300 A | 150 kA |

| 测量时间 | 200 ms | 0.1 ms |

ADC要求的计算示例

动态范围(DR)

最大输入信号必须调整至与最大ADC输入范围相匹配;因此,使用最大电流的最大值计算DR。本例中,用于保护时需要的数值为150 kA。最小信号由5 A驱动,5 A为用于测量时需要的数值。

| 输入范围 | = | 150,000 | = 30,000 |

|

|

|||

| 5 |

| DR 输入范围 | = | 20 × log10(30,000) = 89.5 dB |

精度

本例中有两种精度要求:

- 测量:在5 A和200 ms的条件下为0.5%。

- 保护:在40 A和0.1 ms的条件下为2%。

单独评估这些要求并使用最高的要求来选择合适的ADC。

测量要求

最小输入为5 A时需要0.5%的测量精度,因此额外的SNR/DR可通过以下公式计算:

| DRAccuracy | = 20 × log10 | ( | 1 | ) | = 46 db |

|

|

|||||

| 0.005 |

| No_Samples | = | 8 kSPS × 0.2 sec = 1600 个样本 |

| DRAveraging | = | 20 × log10 √1600 | = 32 dB |

| DR测量精度 | = | 46 dB – 32 dB = 14 dB |

其中,DRMeasurement Accuracy指与测量相关的精度DR。

保护要求

保护要求表明,40 A时允许的最大误差为2%。要确定此要求对整个DR的影响,应先计算最小电流为5 A时的精度,之后才能直接比较保护和测量要求:

| 5 A时的误差 | = | 40 A | × 2% = 16% |

|

|

|||

| 5 A |

SNR/DR贡献按如下方式计算:

| DRAccuracy | = 20 × log10 | ( | 1 | ) | = 15.9 db |

|

|

|||||

| 0.16 |

| No_Samples | = | 8 kSPS × 0.001 sec = 8 个样本 |

| DRAveraging | = | 20 × log10 √8 | = 9 dB |

| DRProtection Accuracy | = | 15.9 dB − 8 dB = 6.9 dB |

其中, DRProtection Accuracy 指与保护相关的精度DR。

评估完保护和测量要求后,可以明确看出,测量要求会产生更高的SNR精度规格(14 dB)。因此,可根据下式选择ADC:

| DRFinal | = | 89.5 dB + 14 dB = 103.5 dB |

信号链实现

如前文所述,DR可通过结合不同的模拟信号链设计和信号处理方式来实现。

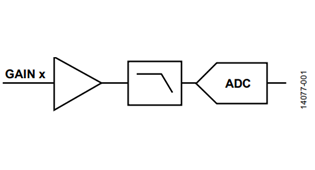

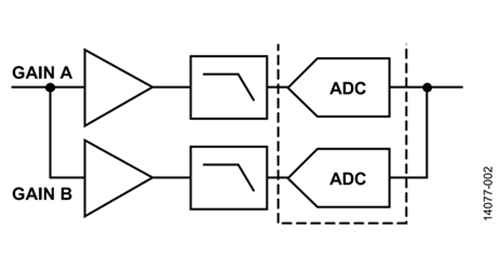

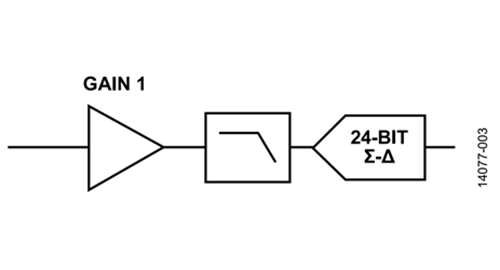

图1至图3显示了如何实现系统DR的顶层框图。

根据ADC采样速率和目标测量带宽之间的比,可在ADC样本上执行额外的数字滤波,以进一步增大信号链的DR。

AD7779是一个8通道、24位、Σ-Δ型ADC。AD7779可实现的输出采样速率/输出数据速率最高为16 kSPS。AD7779的 THD为−108 dB,最高输入频率为1 kHz。

SINAD指满量程均方根输入信号的比率与奈奎斯特频率以下包括谐波的所有其它频谱成分的比率之比。SINAD往往决定了信号链的测量分辨率,因为它同时涵盖信号链的SNR和THD贡献。

知道信号链的SNR和THD后,便可根据下式计算出最终SINAD:

| SINAD | = −10 × log | ( | 10 | −SNR | + 10 | −THD | ) |

|

|

|

||||||

| 10 | 10 |

因此,在8 kSPS、SNR为112 dB、THD为−108 dB的条件下,最终SINAD为106.54 dB,符合“空气断路器示例”所述的DR要求。

AD7779提供集成PGA和24位Σ-Δ型ADC的完全集成式信号链解决方案。有关器件的详情,请参考AD7779数据手册。

有关用于测量宽DR信号的系统的更多示例,请参见《模拟对话》文章“过采样ADC与PGA结合,提供127 dB动态范围”。