AN-1388: 使用AD7779 24位同步采样Σ-Δ型ADC实现电能质量测量的相干采样

简介

随着智能电网的发展,电力公司需要提高电网的可见性和自动化程度。提高电网基础设施的自动化程度可提高电网效率,因为可通过调整动态负载来满足相应需求。提高可见性和自动化程度需要增强电网节点的监控能力。为了满足智能电网的各种要求,输配电(T& D)产品的用户需要具备多种功能的高性价比产品。这些功能包括保护、测量和质量监控。输配电设备制造商正在开发集成式硬件/软件解决方案来满足这些要求。在单个硬件/软件解决方案中加入这些功能需要具有下述特性的模数转换器(ADC):

- 一个8/4通道同步采样24位ADC

- 高动态范围(8 kSPS时为114 dB)

- 一个快速建立ADC(低群延迟)

- 微调ADC输出数据速率(ODR)以促使相干采样频率比线路频率小0.01 Hz

AD7779是一种满足所有这些要求的24位同步采样Σ-Δ型ADC。本应用笔记提供了使用AD7779用线路频率实现相干采样的方法,并将这些方法与其他方法进行了对比。

相干采样要求

要使电能计量和电能质量设备的谐波数据和计量参数获得要求的精度,应确保ADC采样速率和电力线频率之间的相干性。

电力线频率可在50 Hz ± 15%或60 Hz ± 15%范围内变化。在电网完善且得到妥善控制的国家,电力线频率的变化率较低。在电网正在发展的国,电力线频率变化较大。电能质量标准IEC 61000-4-30规定了电能质量产品分类的相应频率跟踪分辨率。A类设备必须能够跟踪0.01 Hz的线路频率变化,S类设备必须能够跟踪0.05 Hz的线路频率变化,而B类设备的跟踪要求则由制造商确定。后续版本的IEC 61000-4-30标准可能会移除B类设备。

IEC 61000-4-30标准所采用的电压谐波测量方法在IEC 61000-4-7中确定:离散傅里叶变换(DFT)使用矩形窗以数字方式在一组样本中执行。不建议采用DFT加窗技术,因为DFT窗口的形状(Hamming、Blackman等)会改变谐波的幅值;如果各制造商采用不同的快速傅里叶变换(FFT)加窗技术,则不同产品供应商的谐波分析结果会有所不同。因此,IEC 61000-4-30 A类电能质量设备不能使用DFT加窗技术来实现相干采样。

实现相干采样的现有解决方案

客户目前使用下述方案之一来维持与线路频率的相干性:

- 使用锁相环(PLL)动态调整ADC时钟。

- 使用Goertzel算法对ADC采样并执行DFT。

- ADC进行至少4倍过采样,插入波形样本,使用常规傅里叶变换(FFT)算法执行DFT。

PPL在模拟或数字域内实施。它提供的输出信号的频率等于输入信号的基频。此信号会动态调整ADC时钟并实现ADC采样与线路基频的相干性。PPL的问题是其响应时间,也就是从线路频率变化时刻到PPL输出建立时刻的时间。

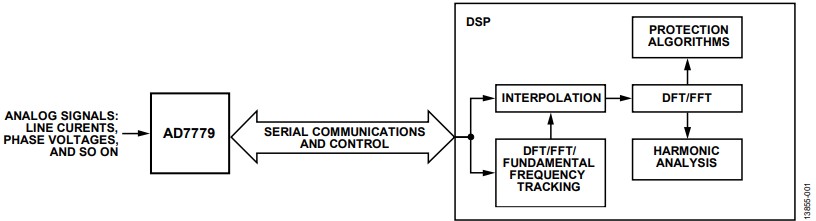

图1显示了由AD7779和数字信号处理器(DSP)组成的保护继电器和测量系统的框图,DSP可计算电压谐波,然后将其用于保护算法中。Goertzel DFT算法会根据实际情况调整傅里叶变换系数在整数线路周期内获得的波形样本数量的函数。这些系数为正弦和余弦系数;因此,DSP必须具有较高的带宽才能应对这种负荷。

也可使用插值方法代替Goertzel算法。将AD777x的输出速率设为32 kSPS,这是通常使用的8 kSPS速率的4倍。DSP插入波形样本以使线路周期内的相同样本数与线路频率无关。插值可以是线性或具有更高的等级,后者得到的结果更准确。DSP必须具有较高的带宽才能应对这种额外的计算负荷。请注意,插值会在测量频带中引入杂散谐波。

现有解决方案都有缺点,如增加功耗(因为更高的DSP计算带宽要求)和成本等。借助AD7779的采样速率转换器(SRC),用户可通过使AD7779 ODR具有足够的分辨率来跟踪电力线频率中的0.01 Hz变化,获得A类电能质量设备。SRC无需采用插值模块,如图1所示。

采样速率

采样速率转换器(SRC)

Σ-Δ型ADC包括一个可高效消除调制器噪声的低通sinc滤波器。sinc滤波器还可使输出数据速率降低一定数量的整数值(与调制器时钟速率相关),该过程称为抽取。通常,抽取限制为一定数量的整数值。AD7779上的sinc滤波器具有同步采样速率转换器(SRC),以便以非整数值进行抽取。用户可在使用此高效成熟的sinc滤波器架构的同时,随时间更改此值。

要使SRC可用,AD7779必须处于SPI控制模式下。上电过程中,通过将FORMAT0引脚和FORMAT1引脚直接与输入/输出数字LDO电源IOVDD相连,选择此模式。

AD7779专为监控主电源电力线网络中的交流电压和电流的应用而设计。这些应用中衡量的两个主要参数是传输线路频率和功耗。通过在ADC产生的输出上执行FFT可确定这两个参数。

AD7779可通过允许用户对特定输出数据速率进行编程,在线路频率内维持相干采样。用户可使用SPI接口对sinc滤波器的抽取系数(N)进行编程。计算输出数据速率(ODR)的公式为

其中:

MCLK为AD7779时钟频率。

AD7779设为高分辨率(HR)模式时M等于4,设为低功耗(LP)模式时M等于8。

fMOD = MCLK/M,指调制器的采样时钟。

计算抽取系数N的步骤如下:

- 将FORMAT0引脚和FORMAT1引脚连接至IOVDD,使AD7779处于SPI控制模式下。

- 选择sinc滤波器、抽取率、功耗模式、PGA增益和内部/外部电压基准,方法是使用SPI接口将这些项目写入相应的存储器映射寄存器。请注意,AD7779仅具有sinc3滤波器。

- 选择ADC的输出数据速率(ODR),数值必须介于表1列出的最小和最大速率之间。

- 根据 fMOD = MCLK/M计算调制器的采样时钟。

- 根据 N = fMOD/ODR计算抽取系数。

| 模式 | 最小ODR (kHz) | 最大ODR (kHz) |

| HR | 0.500000001 | 16 |

| LP | 0.125000001 | 8 |

例如,对于AD7779,可在器件设为LP模式的条件下选用sinc3滤波器。

在一个线路周期内对电压采样64次,以在64点DFT中ADC输出样本。如果线路频率恰为50.00 Hz,则输出数据速率ODR = 50.00 × 64 = 3.200 kHz。调制器的采样时钟为

抽取系数N为

如果线路频率变为50.01 Hz,仍然采样64次。此时输出数据速率ODR = 50.01 × 64 = 3.20064 kHz。

抽取系数N为

使用AD7770/AD7771/AD7779 滤波器型号计算抽取系数和sinc滤波器在任意条件下的响应。

将抽取系数N编入采样速率转换器

在载入SRC前将抽取系数N编入存储器映射。抽取系数由一个整数和一个小数组成。抽取系数编程使用四个存储器映射寄存器。

两个寄存器用于对整数进行编程,可编程值的范围为最小指定值(见表2)至4095。

- 寄存器0x60,SRC_N_MSB位,位[3:0]

- 寄存器0x61,SRC_N_LSB位,位[7:0]

两个寄存器用于对小数(又称插值因子)进行编程,可将待编程的小数表示为16位十进制数。

- 寄存器0x62,SRC_IF_MSB位,位[7:0]

- 寄存器0x63,SRC_IF_LSB位,位[7:0]

表2根据滤波器类型,详细列出了抽取系数N的最小值和最 大值。

| 滤波器类型 | N最小值 | N最大值 |

| Sinc3 (HR 模式) | 128 | 4095 |

| Sinc3 (LP 模式) | 64 | 4095 |

在“采样速率转换器(SRC)”部分的例子中,N = 159.968006。整数为159,小数为0.968006。SRC_N_MSB = 0x00, SRC_N_LSB = 0x9F。

SRC_IF_MSB和RC_IF_LSB寄存器值的计算方法如下:

- 将小数乘以 216: 0.968006 × 216 = 63,439.24。

- 取整数并将其转换为十六进制格式:

- 0xF7写 入 SRC_IF_MSB寄存器,将 0xCF写 入 SRC_IF_LSB寄存器。

AD7770/AD7771/AD7779滤波器型号可计算SRC_N_MSB、 SRC_N_LSB、SRC_IF_MSB和SRC_IF_LSB寄存器的每个抽取系数N(通过计算得到)的寄存器值。

将抽取系数N载入采样速率转换器

SRC_N_MSB、SRC_N_LSB、SRC_IF_MSB和SRC_IF_LSB寄存器仅存储抽取系数。这些抽取系数必须通过SRC加载操作载入DSP。抽取系数可通过软件或硬件加载,具体取决于SRC_UPDATE寄存器(寄存器0x64)中的位7(SRC_LOAD_SOURCE):

- 位 0 = SRC_LOAD_UPDATE

- 位 7 = SRC_LOAD_SOURCE

如果位7 SRC_LOAD_SOURCE的默认值为0,则通过将SRC_LOAD_UPDATE位设为1进行加载。等待至少两个MCLK周期,然后将SRC_LOAD_UPDATE位清0。该位必须清0后才能尝试执行新的加载。

如果位7 SRC_LOAD_SOURCE设为1,则ODR在硬件中进行控制。执行加载的步骤如下:

- 将MODE0/GPIO0引脚连接至MODE1/GPIO1引脚。

- 将MODE2/GPIO2引脚设为高电平,在LP模式下持续两个MCLK周期,在HR模式下持续一个MCLK周期。然后将MODE2/GPIO2引脚设为低电平。

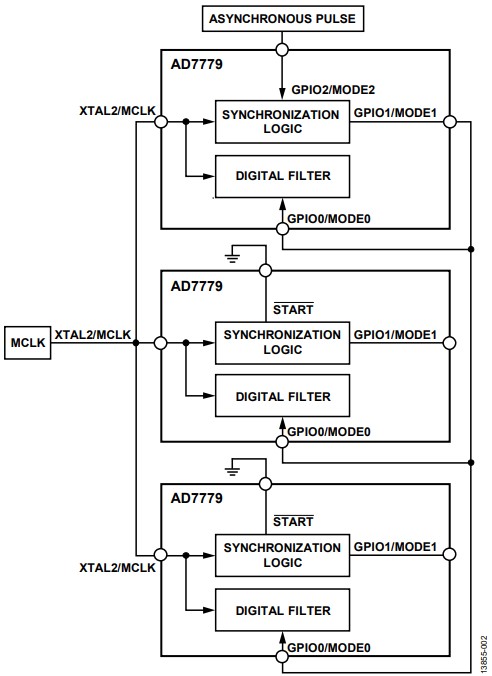

如果多个AD7779器件必须加载相同的同步SRC加载信号,则将一个器件的MODE1/GPIO1引脚连接至其他器件的MODE0/GPIO0引脚。请注意,同步方法需要使用一个共用MCLK(见图2)。

转换为新ODR时的延迟

SRC加载新抽取系数后,转换为新ODR时会出现延迟。出现延迟的原因是SRC会进入转换序列:完成以先前的ODR进行的滤波器输出计算,然后开始以新ODR计算输出。ODR通过监控 DRDY引脚(引脚30)处的信号的周期进行确定。 DRDY引脚保持高电平至少一个DCLK脉冲,以显示最新转换已经完成,数据即将在DOUT引脚提供。

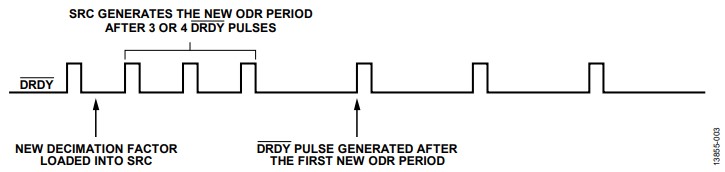

抽取系数加载时刻到在DRDY引脚处看到新ODR的时刻之 间存在延迟。三或四个DRDY脉冲后才会看到新ODR(见 图3)。确切的延迟时间不固定,因为这取决于相对于 DRDY脉冲加载SRC的时间。

在采样速率转变过程中,请勿将新的抽取系数载入SRC。任何此种尝试都将被忽略。

频率

DRDY引脚可用于测量AD7779的ODR。抽取系数为整数 时,DRDY引脚的周期始终固定,等于1/ODR。

例如,如果N = 160,则 ODR = fMOD/N = 512/160 = 3.2 kHz,DRDY 脉冲之间的周期为 1/3200 = 312.5 μs。如果N = 159,则 ODR = 512/159 = 3.220126 kHz ,DRDY脉冲之间的周期为 1/3220.126 = 310.547 μs。

如果抽取系数为非整数值,则DRDY的周期将在不同周期之间振荡,具体取决于抽取系数四舍五入后得到的整数。各个周期的平均值等于预期ODR。但是,各个周期始终以编入AD7779的ODR进行计算。

例如,如果N = 159.968006,DRDY周期将在由N = 159 (310.547 μs)和N = 160 (312.5 μs)确定的周期之间进行振荡,其平均值N/fMOD= 159.968006/512000 = 312.438 μs。

要确定ODR周期是否为预期数值,可测量由下述公式显示的DRDY脉冲数之间的时间。得到的数值近似等于获得预期ODR所需的时间。

当IF≤0.5时,

((1/IF) + 1) 脉冲

当IF>0.5时,

((1/(1 − IF)) + 1) 脉冲

其中,IF为N的小数位。

当DRDY脉冲的数量不是整数时,将结果四舍五入至最近的整数值。

例如,如果N = 159.968006、IF = 0.968006。计算预期ODR周期时必须计数的DRDY 脉冲数如下:

1/(1 − 0.968006) + 1 = 32.35 ≅ 33 DRDY 脉冲