# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

#### **General Description**

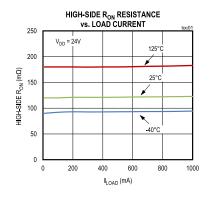

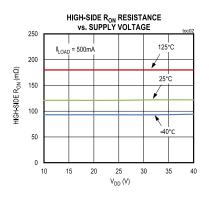

The MAX14914, MAX14914A, and MAX14914B are a family of high-side/push-pull drivers that operate as both industrial digital outputs (DO) and industrial digital inputs (DI). The MAX14914 family features full IEC 61131-2 compliance in both their DO and DI modes of operation. The high-side switch current is resistor settable from 135mA (min) to 1.3A (min). The high-side driver's on-resistance is 120m $\Omega$  (typ) at an ambient temperature of 125°C. Optional push-pull operation allows driving of cables and fast discharge of load capacitance. The output voltage is monitored and indicated through the  $\overline{DOI\_LVL}$  pin for safety applications.

The MAX14914 family complies with Type 1, Type 2, or Type 3 input characteristics when configured for DI operation.

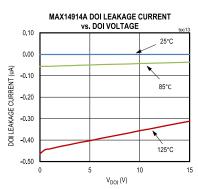

The MAX14914A is a low-DOI-leakage version of the MAX14914, specifically designed to work together with the MAX22000 Industrial Configurable Analog IO device. The MAX14914B features a high-side switch overcurrent indication.

#### **Applications**

- Industrial Digital Output and Input Modules

- Configurable Digital Input/Output

- Motor Control

- Safety Systems

#### **Benefits and Features**

- · Reduces Power and Heat Dissipation

- 240m $\Omega$  (max) HS R<sub>ON</sub> at T<sub>A</sub> = 125°C

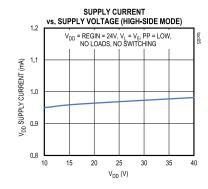

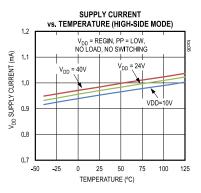

- 0.9mA (typ) High-Side DO-Mode Supply Current

- Accurate Internal Current Limiter for Type 1, Type 2, and Type 3 Digital Inputs

- Enhances System Robustness

- SafeDemag<sup>™</sup> for Safe Turn-Off of Unlimited Inductance

- 60V Supply Tolerance

- · Accurate Short-Circuit DO Mode Current Limiting

- ±2kV IEC 61000-4-5 Surge Protection

- ±20kV IEC 61000-4-2 Air-Gap ESD Protection

- ±7kV IEC 61000-4-2 Contact ESD Protection

- -40°C to +125°C Ambient Operating Temperature

- Reduces BOM Count and PCB Space

- Small 4mm x 4mm TQFN Package

- · Internal Clamp for Fast Inductive Load Turn-Off

- · On-Chip 5V Regulator

- Provides Flexibility

- Configurable as a Digital Input, or a High-Side or Push-Pull Digital Output

- Low-Leakage Mode (MAX14914A) Allows High Accuracy AIO/DIO applications

- Resistor Settable Current Limiting for the High-Side Switch (135mA to 1.3A)

- Pin-Selectable Type 1/3 or Type 2 DI Operation

- Improves System Speed and Throughput

- Propagation Delay of Less Than 2μs

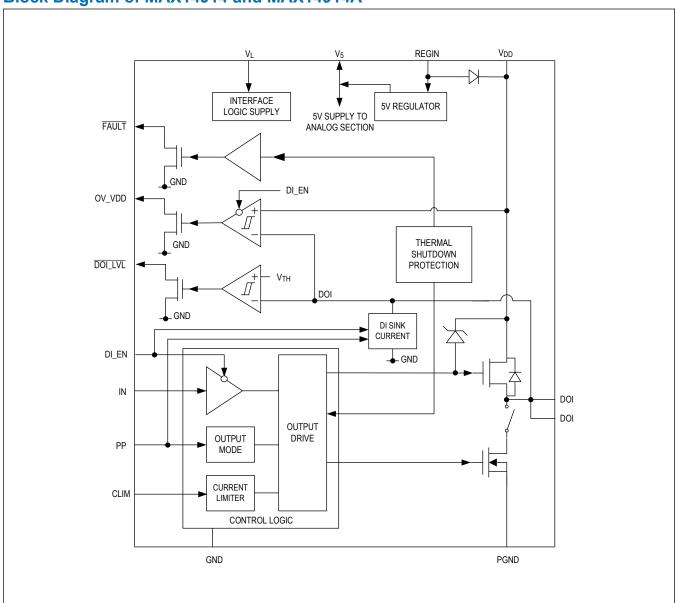

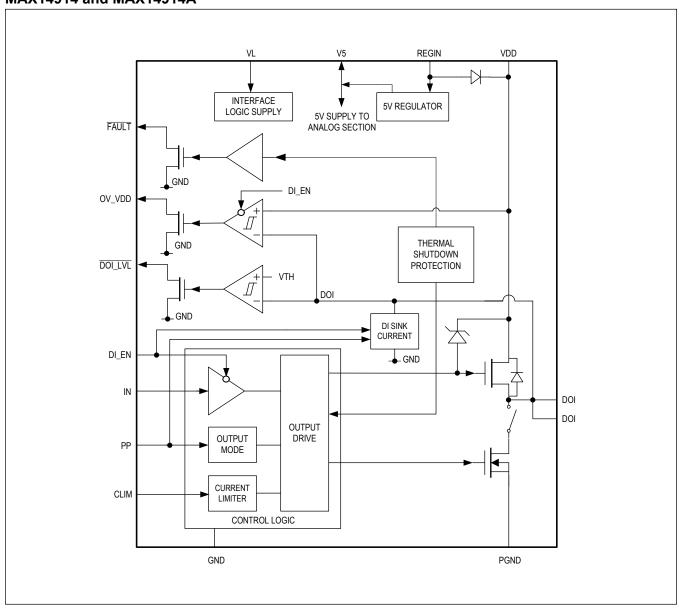

# Block Diagram of MAX14914 and MAX14914A

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

#### **Absolute Maximum Ratings**

|                                                                              | oad CurrentInternally Limited                                    |

|------------------------------------------------------------------------------|------------------------------------------------------------------|

| REGIN0.3V to lower of +65V and (V <sub>DD</sub> + 0.3V) Continu              | uous Current (any other terminal)100mA to +100mA                 |

| PGND0.3V to +0.3V Continu                                                    | uous Power Dissipation (T <sub>A</sub> = +70°C, derate 28,6mW/°C |

| DOI $(V_{DD} < V_{DD} \ OVLOTH)$ $(V_{DD} - 49V)$ to $(V_{DD} + 0.3V)$ above | +70°C)2280mW                                                     |

| DOI $(V_{DD} > V_{DD} OV_{LOTH})$ 1V to $(V_{DD} + 0.3V)$ Inductive          | ive Demagnetization Energy (I <sub>LOAD</sub> < 0.6A)Unlimited   |

| $V_5$ 0.3V to lower of +6V and (REGIN + 0.3V) Operat                         | ting Temperature Range40°C to +125°C                             |

|                                                                              | on TemperatureInternally Limited                                 |

| IN, PP, DIN_EN, FAULT, CLIM0.3V to +6V Storage                               | ge Temperature Range65°C to +150°C                               |

|                                                                              | Γemperature (Soldering, 10s)+260°C                               |

| OV_VDD, OV_CURR0.3V to lower of +65V and (V <sub>DD</sub> + 0.3V)            |                                                                  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **16 TQFN**

| Package Code                                          | T1644+4A       |  |  |  |  |  |

|-------------------------------------------------------|----------------|--|--|--|--|--|

| Outline Number                                        | <u>21-0139</u> |  |  |  |  |  |

| Land Pattern Number                                   | 90-0070        |  |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                  |                |  |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                | 35°C/W         |  |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) | 2.7°C/W        |  |  |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.analog.com/packages">www.analog.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="www.analog.com/thermal-tutorial">www.analog.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{DD} = +10 \text{V to } +40 \text{V}, \ V_5 = +4.5 \text{V to } +5.5 \text{V}, \ T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \ unless otherwise noted.}, \ Typical \ values are at \ T_A = +25 ^{\circ}\text{C}, \ V_{DD} = +24 \text{V}, \ V_L = +3.3 \text{V and } V_5 = +5 \text{V}, \ R_{LIM} = 50 \text{k}\Omega.) \ (\underbrace{Note \ 1}_{C})$

| PARAMETER                          | SYMBOL                 | L CONDITIONS                                                                                                      |     | TYP  | MAX  | UNITS |

|------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| V <sub>DD</sub> SUPPLY             |                        |                                                                                                                   |     |      |      |       |

| Supply Voltage                     | V                      | Operting Conditions                                                                                               | 10  |      | 40   | V     |

| Supply Vollage                     | V <sub>DD</sub>        | Tolerant                                                                                                          | 0   |      | 60   | ]     |

|                                    | I <sub>DD_ON_HS</sub>  | HS mode, PP = low, IN = $V_L$ , DOI high (no switching), no load, $V_5 = V_L = REGIN = 5V$ , $V_{DD} = 40V$ .     |     | 0.6  | 0.95 | mA    |

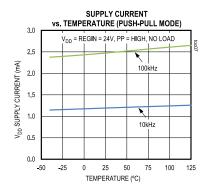

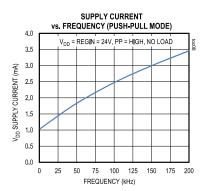

| Supply Current                     | I <sub>DD_ON_PP</sub>  | PP mode, PP = high, 10kHz switching, V <sub>5</sub> = V <sub>L</sub> = REGIN = 5V, V <sub>DD</sub> = 40V, no load |     | 0.85 | 1.4  |       |

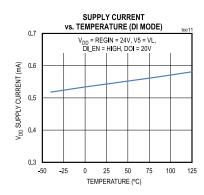

|                                    | I <sub>DD_ON_DI</sub>  | DI mode, DI_EN = V <sub>L</sub> , REGIN = V <sub>DD</sub> = 40V                                                   |     | 0.13 | 0.3  | mA    |

| Undervoltage-Lockout               | V <sub>DD_UVLO</sub>   | $V_{DD}$ rising, $V_5 = V_L$                                                                                      | 8.5 | 9.1  | 9.7  | V     |

| Threshold                          | V <sub>DD_UVLO</sub>   | $V_{DD}$ falling, $V_5 = V_L$                                                                                     | 8   | 8.6  | 9    | V     |

| Undervoltage-Lockout<br>Hysteresis | V <sub>DD_UVHYST</sub> | $V_5 = V_L$ 0.5                                                                                                   |     |      | V    |       |

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

### **Electrical Characteristics (continued)**

$(V_{DD} = +10 \text{V to } +40 \text{V}, V_5 = +4.5 \text{V to } +5.5 \text{V}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}, \text{Typical values are at } T_A = +25 ^{\circ}\text{C} \text{ , } V_{DD} = +24 \text{V}, V_L = +3.3 \text{V and } V_5 = +5 \text{V}, R_{LIM} = 50 \text{k}\Omega.) \text{ } (\underbrace{Note \ 1})$

| PARAMETER                                          | SYMBOL                       | CONDITIONS                                                                                                                           | MIN      | TYP  | MAX  | UNITS |  |

|----------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------|------|------|-------|--|

| V <sub>DD</sub> Overvoltage-                       | V <sub>DD_OVLO</sub>         | V <sub>DD</sub> rising, V <sub>5</sub> = V <sub>L</sub>                                                                              | 41.5     | 43.5 | 45   | V     |  |

| Lockout Threshold                                  | V <sub>DD_OVLO</sub>         | $V_{DD}$ falling, $V_5 = V_L$                                                                                                        | 40.5     | 42.2 | 44   | V     |  |

| V <sub>DD</sub> Overvoltage-<br>Lockout Hysteresis | V <sub>DD_OVHYST</sub>       | $V_5 = V_L$                                                                                                                          |          | 1    |      | V     |  |

| V <sub>L</sub> LOGIC INTERFACE S                   | UPPLY                        |                                                                                                                                      |          |      |      |       |  |

| V <sub>L</sub> Supply Voltage                      | VL                           |                                                                                                                                      | 2.5      |      | 5.5  | V     |  |

| V <sub>L</sub> Supply Current                      | ΙL                           | All logic inputs high or low, all outputs unloaded                                                                                   |          | 10   | 25   | μА    |  |

| V <sub>L</sub> POR Threshold                       | V <sub>L_POR</sub>           | V <sub>L</sub> falling                                                                                                               | 1.12     | 1.27 | 1.52 | V     |  |

| 5V SUPPLY / LINEAR RE                              | GULATOR                      |                                                                                                                                      |          |      |      | •     |  |

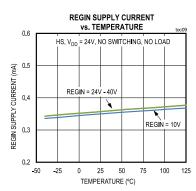

| REGIN Current HS<br>Mode                           | I <sub>REGIN_ON_H</sub><br>S | HS mode, REGIN = 40V, IN = $V_L$ , no load on DOI, no load on $V_5$                                                                  |          | 0.3  | 0.5  | mA    |  |

| REGIN Current PP<br>Mode                           | I <sub>REGIN_ON_PP</sub>     | PP = high, REGIN = 40V, 10kHz<br>switching, no load on DOI, no load on V <sub>5</sub>                                                |          | 0.35 | 0.6  | mA    |  |

| REGIN Current DI Mode                              | IREGIN_ON_DI                 | DI_EN = V <sub>L</sub> , REGIN = 40V                                                                                                 |          |      | 0.5  | mA    |  |

|                                                    | I <sub>V5_HS</sub>           | HS mode, REGIN = $V_5$ = 5V, IN = $V_L$ , no load on DOI                                                                             |          | 0.24 | 0.4  |       |  |

| V <sub>5</sub> Supply Current                      | I <sub>V5_PP</sub>           | PP mode, REGIN = V <sub>5</sub> = 5V, 10kHz switching, no load on DOI                                                                |          | 0.3  | 0.5  | mA    |  |

|                                                    | I <sub>V5_DI</sub>           | DI mode, DI_EN = high, REGIN = V <sub>5</sub> = 5V                                                                                   |          | 0.22 | 0.4  |       |  |

| REGIN Undervoltage<br>Threshold                    | V <sub>REG_UV</sub>          | REGIN rising. V <sub>5</sub> enabled when REGIN > V <sub>REG_UV</sub> .                                                              | 6.75     |      | 7.6  | V     |  |

| REGIN Undervoltage<br>Hysteresis                   | V <sub>REG_UVHYS</sub>       | _                                                                                                                                    |          | 0.45 |      | V     |  |

| V <sub>5</sub> Undervoltage-<br>Lockout Threshold  | V <sub>5_UVLO</sub>          | V <sub>5</sub> rising                                                                                                                | 3.8      |      | 4.2  | V     |  |

| V <sub>5</sub> Undervoltage-<br>Lockout Hysteresis | V <sub>5UV_UVHYST</sub>      |                                                                                                                                      |          | 0.3  |      | V     |  |

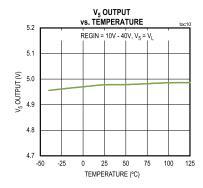

| V <sub>5</sub> Output Voltage                      | V <sub>5</sub>               | 0mA - 20mA external load                                                                                                             | 4.75     | 5.0  | 5.25 | V     |  |

| V <sub>5</sub> Current Limit                       | I <sub>V5_CL</sub>           |                                                                                                                                      | 25       |      |      | mA    |  |

| DRIVER OUTPUT (DOI)                                | _                            |                                                                                                                                      |          |      |      |       |  |

| HS On-Resistance                                   | R <sub>DOI_ON_HS</sub>       | $PP = X$ , $IN = high$ , $I_{DOI} = 500mA$                                                                                           |          | 120  | 240  | mΩ    |  |

| LS Output Low                                      | V <sub>DOI_LOW</sub>         | PP = high, IN = low, I <sub>DOI</sub> = 100mA                                                                                        |          |      | 1.2  | V     |  |

|                                                    | V <sub>DOI_CL</sub>          | Relative to V <sub>DD</sub> , I <sub>DOI</sub> = 500mA, V <sub>DD</sub> < V <sub>DD_OVLO</sub>                                       | -63      | -55  | -49  | V     |  |

| DOI Clamp Voltage                                  | V <sub>DOI_CL</sub>          | Relative to GND, I <sub>DOI</sub> = 500mA,<br>V <sub>DD_OVLO</sub> < V <sub>DD</sub> < 60V                                           | -4.5     | -2.9 | -1.5 | V     |  |

| DOI Leakage<br>MAX14914,                           |                              | V <sub>DD</sub> = 40V, PP = IN = Iow, DI_EN = Iow,<br>0V < V <sub>DOI</sub> < V <sub>DD</sub> , V <sub>L</sub> > V <sub>L</sub> _POR | -60      |      | 60   |       |  |

| MAX14914A,<br>MAX14914B                            | I <sub>DOI_LK</sub>          | V <sub>DD</sub> = 60V, PP = IN = X, DI_EN = low,<br>0V < V <sub>DOI</sub> < V <sub>DD</sub> , V <sub>L</sub> > V <sub>L</sub> POR    | -150 150 |      | 150  | — μA  |  |

### **Electrical Characteristics (continued)**

$(V_{DD} = +10 \text{V to } +40 \text{V}, V_5 = +4.5 \text{V to } +5.5 \text{V}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}, \text{Typical values are at } T_A = +25 ^{\circ}\text{C} \text{ , } V_{DD} = +24 \text{V}, V_L = +3.3 \text{V and } V_5 = +5 \text{V}, R_{LIM} = 50 \text{k}\Omega.) \text{ } (\underbrace{Note \ 1})$

| PARAMETER                              | SYMBOL                   | CONDITIONS                                                                                            | MIN       | TYP                 | MAX       | UNITS |

|----------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|-----------|---------------------|-----------|-------|

|                                        |                          | $V_{DD}$ = 40V, $V_{L}$ < $V_{L}$ POR, PP = IN = DI_EN = X, 0V < $V_{DOI}$ < 15V                      | -2.4      |                     | 0         |       |

| DOI Leakage<br>MAX14914A               | I <sub>DOI_LK</sub>      | $V_{DD}$ = 40V, $V_{L}$ < $V_{L-POR}$ , PP = IN = DI_EN = X, 0V < $V_{DOI}$ < 15V, T = -40°C to +85°C | -0.4      |                     | 0         | μΑ    |

|                                        |                          | $V_{DD}$ = 34V, $V_{L}$ < $V_{L}$ POR, PP = IN = DI_EN = X, -15V < $V_{DOI}$ < 0V                     |           | -80                 |           |       |

| <b>OUTPUT DRIVER CURR</b>              | ENT LIMITING (           | OOI)                                                                                                  |           |                     |           |       |

| HS Current-Limit<br>Minimum            | I <sub>CLIM_HS_MIN</sub> | R <sub>LIM</sub> = 220kΩ                                                                              | 135       | 196                 | 255       | mA    |

| HS Current-Limit<br>Maximum            | ICLIM_HS_MAX             | R <sub>LIM</sub> = 27kΩ                                                                               | 1.3       | 1.6                 | 1.9       | А     |

| HS Current-Limit Offset<br>Error       | ICLIM_HS_OE              | ( <u>Note 2</u> )                                                                                     | -25       |                     | +25       | mA    |

| HS Current-Limit Gain<br>Error         | I <sub>CLIM_HS_GE</sub>  | ( <u>Note 2</u> )                                                                                     | -20       |                     | +20       | %     |

| CLIM Voltage                           | V <sub>CLIM</sub>        |                                                                                                       |           | 1.21                |           | V     |

| CLIM Short Resistor<br>Threshold Value | R <sub>LIM_SHORT</sub>   | ( <u>Note 3</u> )                                                                                     | 10        | 12.9                | 15        | kΩ    |

| CLIM Open Resistor<br>Threshold Value  | R <sub>LIM_OPEN</sub>    | ( <u>Note 4</u> )                                                                                     | 440       |                     | 750       | kΩ    |

| LS Current Limit                       | I <sub>CLIM_LS</sub>     |                                                                                                       | 150       |                     | 280       | mA    |

| DIGITAL INPUT / DOI MO                 | ONITOR                   |                                                                                                       |           |                     |           |       |

| DO Monitor Threshold                   | V <sub>TH_DO</sub>       | DI_EN = low, DOI rising                                                                               | 1.5       |                     | 2.0       | V     |

| Voltage                                | V <sub>TH_DO</sub>       | DI_EN = low, DOI falling                                                                              | 1.3       |                     | 1.8       | V     |

| DO Monitor Hysteresis                  | V <sub>HYS_DO</sub>      | DI_EN = low                                                                                           |           | 0.2                 |           | V     |

| DI Threshold Voltage                   | V <sub>TH_DI</sub>       | DI_EN = high, DOI rising                                                                              | 6.7       |                     | 8         | V     |

| 21 Throundia Voltago                   | * IH_DI                  | DI_EN = high, DOI falling                                                                             | 5.5       |                     | 6.8       | •     |

| DI Hysteresis                          | V <sub>HYS_DI</sub>      | DI_EN = high                                                                                          |           | 1.2                 |           | V     |

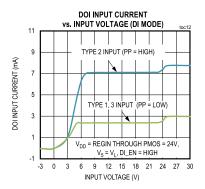

| DI Current Sink Type                   |                          | DI_EN = high, PP = low, $0V < V_{DOI} < 5V$                                                           |           |                     | 2.6       |       |

| 1/3                                    | ldoi                     | DI_EN = high, PP = low, $8V < V_{DOI} < 40V$ , $V_{DOI} < V_{DD}$                                     | 2.0       | 2.3                 | 2.6       | mA    |

|                                        |                          | DI_EN = high, PP = high, $0V < V_{DOI} < 5V$                                                          | 0         |                     | 7.5       |       |

| DI Current Sink Type 2                 | ldoi                     | DI_EN = high, PP = high, $8V < V_{DOI} < 40V$ , $V_{DOI} < V_{DD}$                                    | 6.0       | 7.0                 | 7.7       | mA    |

| LOGIC (I/O)                            |                          |                                                                                                       |           |                     |           |       |

| Input Voltage High                     | V <sub>IH</sub>          |                                                                                                       | $0.7xV_L$ |                     |           | V     |

| Input Voltage Low                      | V <sub>IL</sub>          |                                                                                                       |           |                     | $0.3xV_L$ | V     |

| Input Threshold<br>Hysteresis          | V <sub>IHYST</sub>       |                                                                                                       |           | 0.11xV <sub>L</sub> |           | V     |

| Input Pulldown Resistor                | R <sub>I</sub>           | All logic input pins                                                                                  | 140       | 200                 | 275       | kΩ    |

| Output Logic Low                       | V <sub>OL</sub>          | I <sub>LOAD</sub> = +5mA                                                                              |           |                     | 0.33      | V     |

### **Electrical Characteristics (continued)**

$(V_{DD} = +10 \text{V to } +40 \text{V}, V_5 = +4.5 \text{V to } +5.5 \text{V}, T_A = -40 ^{\circ}\text{C to } +125 ^{\circ}\text{C}, \text{ unless otherwise noted.}, \text{Typical values are at } T_A = +25 ^{\circ}\text{C} \text{ , } V_{DD} = +24 \text{V}, V_L = +3.3 \text{V and } V_5 = +5 \text{V}, R_{LIM} = 50 \text{k}\Omega.) \text{ } (\underbrace{Note \ 1})$

| PARAMETER                               | SYMBOL                                                                                                 | CONDITIONS                                                                                                                        | MIN | TYP  | MAX | UNITS |

|-----------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| DOI_LVL Tristate<br>Leakage             | ILEAK                                                                                                  | $GND < V_{DOI\_LVL} < V_L \qquad -1 \qquad +1$                                                                                    |     | μA   |     |       |

| FAULT Output Tristate<br>Leakage        | I <sub>LEAK</sub>                                                                                      | GND < V <sub>FAULT</sub> < V <sub>5</sub>                                                                                         | -1  |      | +1  | μA    |

| OV_VDD Leakage                          | I <sub>LEAK</sub>                                                                                      | GND < V <sub>OV_VDD</sub> < V <sub>DD</sub>                                                                                       | -1  |      | +1  | μA    |

| OV_CURR Leakage                         | I <sub>LEAK</sub>                                                                                      | GND < V <sub>OV_CURR</sub> < V <sub>DD</sub>                                                                                      | -1  |      | +1  | μA    |

| THERMAL PROTECTION                      | ١                                                                                                      |                                                                                                                                   |     |      |     |       |

| Driver Thermal-<br>Shutdown Temperature | T <sub>JSHDN</sub>                                                                                     | Junction temperature rising                                                                                                       |     | 170  |     | °C    |

| Driver Thermal-<br>Shutdown Hysteresis  | T <sub>JSHDN_HYST</sub>                                                                                |                                                                                                                                   |     | 15   |     | °C    |

| Chip Thermal Shutdown                   | T <sub>CSHDN</sub>                                                                                     | Temperature rising                                                                                                                |     | 150  |     | °C    |

| Chip Thermal-Shutdown<br>Hysteresis     | T <sub>CSHDN_HYS</sub><br>T                                                                            |                                                                                                                                   |     | 10   |     | °C    |

| TIMING CHARACTERIST                     | TICS / OUTPUT D                                                                                        | DRIVER (DOI)                                                                                                                      |     |      |     |       |

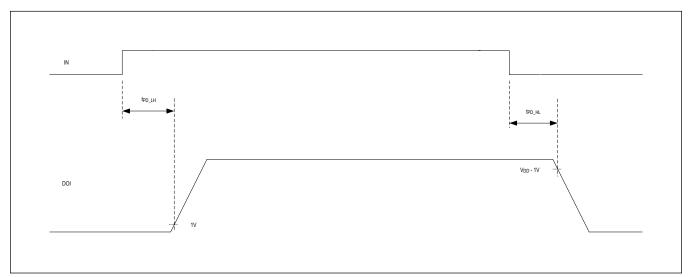

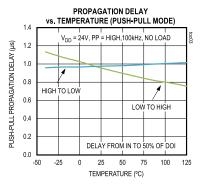

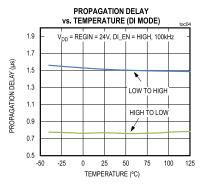

| Output Propagation<br>Delay LH          | t <sub>PD_LH</sub>                                                                                     | PP = low, delay from IN to DOI rising by 1V, $R_L = 5k\Omega$ , $C_L = 100pF$ (Figure 1)                                          |     | 0.4  | 1.5 | μs    |

| Output Propagation                      | t <sub>PD_HL</sub>                                                                                     | PP = low, delay between IN switching low to DOI falling by 1V, $R_L$ = $5k\Omega$ , $C_L$ = $100pF$ , $V_{DD}$ = $24V$ (Figure 1) |     | 0.6  | 1.5 | μs    |

| Delay HL                                | t <sub>PD_HL</sub>                                                                                     | PP = high, delay between IN switching low to DOI falling by 1V, $R_L = 5k\Omega$ , $C_L = 100pF$ (Figure 1)                       |     | 0.6  | 1.5 | μs    |

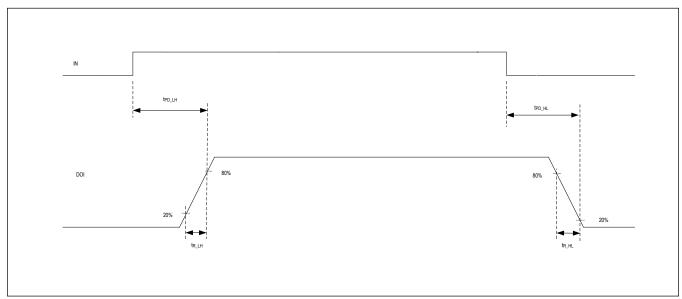

| DOI Output Rise Time                    | t <sub>R</sub>                                                                                         | PP = X, 20% to 80% $V_{DD}$ , $R_L = 5kΩ$ , $C_L$ = 100pF ( <u>Figure 2</u> )                                                     |     | 0.9  | 2   | μs    |

| DOLO 12 1 F. II T                       | $t_{F}$ PP = high, 80% to 20% $V_{DD}$ , $V_{DD}$ = 24V, $R_{L}$ = 5k $\Omega$ , CL = 100pF (Figure 2) |                                                                                                                                   |     | 0.65 | 2   | μs    |

| DOI Output Fall Time                    | t <sub>F</sub>                                                                                         | PP = low, 80% to 20% $V_{DD}$ , $V_{DD}$ = 24V, $R_L$ = 47Ω, $C_L$ = 100pF (Figure 2)                                             | 1   |      |     | μs    |

| TIMING CHARACTERIST                     | TICS / PROPAGA                                                                                         | ATION DELAY (DOI to DOI_LVL)                                                                                                      |     |      |     |       |

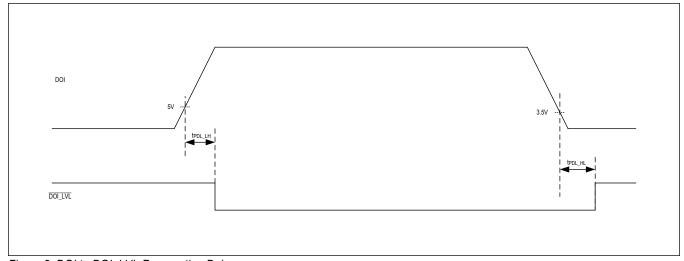

| Propagation Delay LH                    | t <sub>PDL_LH</sub>                                                                                    | DI_EN = low, delay from DOI rising to 5V to DOI_LVL low (Figure 3)                                                                |     | 2.7  | 5   | μs    |

| Propagation Delay LH<br>DI              | t <sub>PDL_HL_DI</sub>                                                                                 | DI_EN = high, delay from DOI rising to 8V to DOI_LVL low                                                                          |     | 1.1  |     | μs    |

| Propagation Delay HL                    | t <sub>PDL_HL</sub>                                                                                    | DI_EN = low, delay from DOI falling to 3.5V to DOI_LVL high 0.9                                                                   |     | 8    | μs  |       |

| Propagation Delay HL<br>DI              | tpDL_HL_DI                                                                                             | DI_EN = high, delay from DOI falling to 5.5V to DOI_LVL high                                                                      |     |      | μs  |       |

| TIMING CHARACTERIST                     | TICS / GLITCH R                                                                                        | EJECTION (IN)                                                                                                                     |     |      |     | 1     |

| Pulse Length of<br>Rejected Glitch      | t <sub>FPL_GF</sub>                                                                                    |                                                                                                                                   | 0   |      | 80  | ns    |

| Glitch Filter Delay Time                | t <sub>D_GF</sub>                                                                                      |                                                                                                                                   |     | 140  | 300 | ns    |

#### **Electrical Characteristics (continued)**

$(V_{DD} = +10V \text{ to } +40V, V_5 = +4.5V \text{ to } +5.5V, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}, \text{Typical values are at } T_A = +25^{\circ}\text{C} \text{ , } V_{DD} = +24V, V_L = +3.3V \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{C} \text{ and } V_5 = +5V, R_{LIM} = 50\text{k}\Omega.) \\ \underbrace{(Note \ 1)}_{NOTE} = +25^{\circ}\text{$

| PARAMETER                                         | SYMBOL                 | CONDITIONS                                                        | MIN  | TYP | MAX | UNITS |

|---------------------------------------------------|------------------------|-------------------------------------------------------------------|------|-----|-----|-------|

| TIMING CHARACTERISTICS / FAULT DETECTION (OV_VDD) |                        |                                                                   |      |     |     |       |

| OV_VDD Threshold                                  | V <sub>TH_OV_VDD</sub> | DI_EN = low, relative to V <sub>DD</sub> . MAX14914 and MAX14914A | 0.22 |     | V   |       |

| OVLO_VDD Debounce<br>Time                         | TD <sub>OVLO_VDD</sub> | DI_EN = low. MAX14914 and MAX14914A.                              | 200  |     | μs  |       |

#### **Electrical Characteristics—ESD and SURGE Protection**

| PARAMETER            | SYMBOL             | CONDITIONS MIN TYP MAX                                                   |    | UNITS |    |    |

|----------------------|--------------------|--------------------------------------------------------------------------|----|-------|----|----|

|                      |                    | DOI pin Contact Discharge (Note 5)                                       |    | ±7    |    |    |

| ESD V <sub>ESD</sub> |                    | V <sub>ESD</sub> DOI pin Air Discharge ( <u>Note 5</u> )                 |    | ±20   |    | kV |

|                      |                    | All other pins. Human Body Model                                         | ±2 |       | 1  |    |

| IEC Surge            | V <sub>SURGE</sub> | DOI to PGND or Earth GND per IEC 61000-4-5 (42Ω/0.5μF) ( <i>Note 6</i> ) | ±2 |       | kV |    |

- Note 1: All the MAX14914ATE+ and MAX14914BATE+ units are production tested at  $T_A$  = +25°C. All the MAX14914AATE+ units are production tested at  $T_A$  = +25°C and +125°C. Specifications over temperature are guaranteed by characterization and design.

- Note 2: Specification is guaranteed by design; not production tested.

- Note 3: Lower resistor values than CLIM\_SHORT act like a CLIM pin short to GND

- Note 4: Higher resistor values than CLIM\_OPEN act like a CLIM open circuit.

- Note 5: Bypass  $V_{DD}$  pin to PGND with  $1\mu F$  capacitor as close as possible to the device for high ESD protection.

- Note 6: With TVS protection on V<sub>DD</sub> to PGND.

Figure 1. IN to DOI Propagation Delay

Figure 2. DOI Rise and Fall Time

Figure 3. DOI to DOI\_LVL Propagation Delay

#### **Typical Operating Characteristics**

$(V_{DD} = +24V, V_L = +3.3V, V_5 = +5V, T_A = +25$ °C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

(V<sub>DD</sub> = +24V,  $V_L$  = +3.3V,  $V_5$  = +5V,  $T_A$  = +25°C, unless otherwise noted.)

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

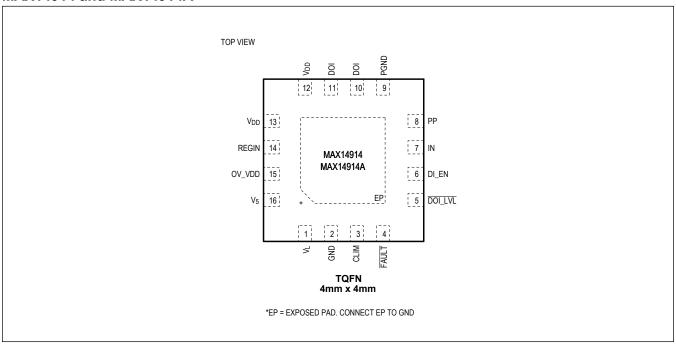

# **Pin Configurations**

#### MAX14914 and MAX14914A

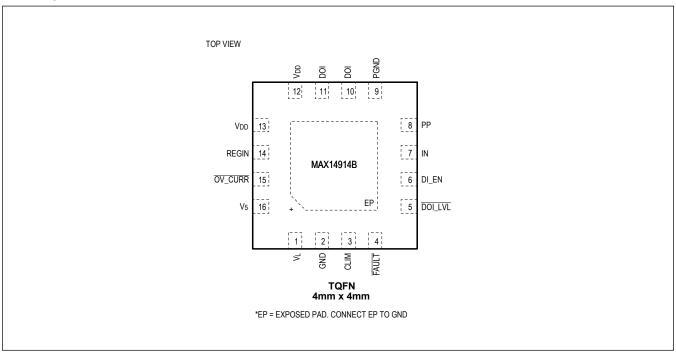

#### **MAX14914B**

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

# **Pin Description**

| Р                            | IN        |                 |                                                                                                                                                                                                                                                                                                                                   |              |

|------------------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| MAX14914<br>and<br>MAX14914A | MAX14914B | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                          | TYPE         |

| 1                            | 1         | VL              | Logic Supply Input. V <sub>L</sub> defines the levels on all I/O logic interface pins. Bypass V <sub>L</sub> to GND through a 100nF ceramic capacitor.                                                                                                                                                                            | Supply       |

| 2                            | 2         | GND             | Analog Ground.                                                                                                                                                                                                                                                                                                                    | Supply       |

| 3                            | 3         | CLIM            | Current Limit Set Input. Connect a resistor from CLIM to GND to set the current limit. See <u>Detailed Description</u> for further information.                                                                                                                                                                                   | Analog Input |

| 4                            | 4         | FAULT           | Open-Drain Fault Output. The $\overline{\text{FAULT}}$ transistor turns on when a fault condition (driver thermal shutdown or loss of ground) occurs. Connect a pull-up to $V_L$ or $V_5$ .                                                                                                                                       | Logic Output |

| 5                            | 5         | DOI_LVL         | Open-Drain DOI Level Output. DOI_LVL is logic-low when DOI voltage is higher than the threshold voltage. DOI_LVL is logic-high (using a pull-up resistor) when DOI voltage is lower than the threshold voltage, except thermal shutdown conditions. The threshold voltage depends on DI_EN. Connect a pull-up to V <sub>L</sub> . | Logic Output |

| 6                            | 6         | DI_EN           | Digital Input Mode Logic Enable Input. Set DI_EN high to enable digital input operation on the DOI pin, which enables the internal current sink and sets Type 1, Type 2, or Type 3 thresholds on DOI_LVL. Select between Type 1 and 3, and Type 2 DI characteristics through the PP input.                                        | Analog       |

| 7                            | 7         | IN              | Switch Control Input. Drive IN high to close the HS switch; drive IN low to open the HS switch and close the LS switch (when PP = low).                                                                                                                                                                                           | Logic Input  |

| 8                            | 8         | PP              | Push-Pull DO or DI Type Select Input. In DO mode, set PP high to enable push-pull mode operation of the DO driver. In DI mode, set PP low for IEC Type 1/3 input characteristics and set high for Type 2 input characteristics.                                                                                                   | Logic Input  |

| 9                            | 9         | PGND            | Power Ground                                                                                                                                                                                                                                                                                                                      | Supply       |

| 10, 11                       | 10, 11    | DOI             | High-Side / Push-Pull Output (DI_EN = low) or Digital Input (DI_EN = high). Connect both DOI pins together externally.                                                                                                                                                                                                            | Power        |

| 12, 13                       | 12, 13    | V <sub>DD</sub> | Supply Voltage, Nominally 24V. Bypass V <sub>DD</sub> to GND through a 1µF capacitor.                                                                                                                                                                                                                                             | Supply       |

| 14                           | 14        | REGIN           | 5V Regulator Input. Connect REGIN to $V_{DD}$ when using the internal 5V regulator. Connect REGIN to $V_5$ when powering $V_5$ from an external regulator.                                                                                                                                                                        | Supply       |

| 15                           | _         | OV_VDD          | Open-Drain Overvoltage Output for the MAX14914 and MAX14914A. The OV_VDD transistor turns off when: 1) a device configured for DI operation; 2) DOI level is higher than V <sub>DD</sub> . Connect a pullup to V <sub>DD</sub> . See <u>Detailed Description</u> and Figure 8 for details.                                        |              |

| _                            | 15        | OV_CURR         | Open-Drain Overcurrent Output for the MAX14914B. OV_CURR turns active low when the load current exceeds the high-side current limit. Connect a pull-up resistor between OV_CURR and V <sub>L</sub> .                                                                                                                              |              |

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

# **Pin Description (continued)**

| P                            | IN        |                |                                                                                                                                                                                                                                                                                        |        |

|------------------------------|-----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| MAX14914<br>and<br>MAX14914A | MAX14914B | NAME           | FUNCTION                                                                                                                                                                                                                                                                               | TYPE   |

| 16                           | 16        | V <sub>5</sub> | Analog Supply Voltage/LDO Output. The MAX14914 requires a 5V supply for normal operation, which can come from the internal linear regulator (REGIN connected to $V_{DD}$ ) or from an external regulator (REGIN connected to $V_{5}$ ). Bypass to GND through a 1µF ceramic capacitor. | Supply |

| _                            | _         | EP             | Exposed Pad. Connect EP to GND.                                                                                                                                                                                                                                                        |        |

High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

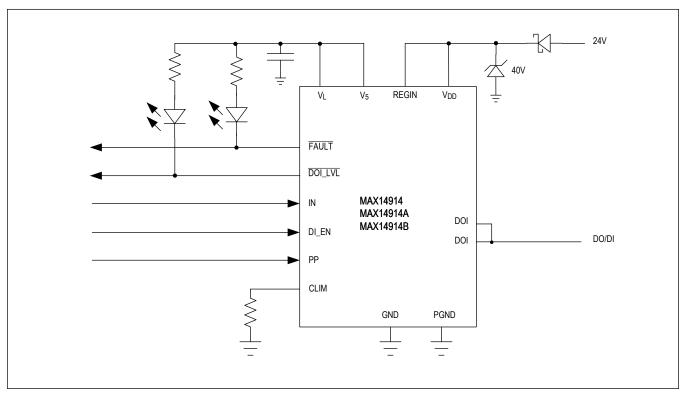

# **Functional Diagrams**

#### MAX14914 and MAX14914A

High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

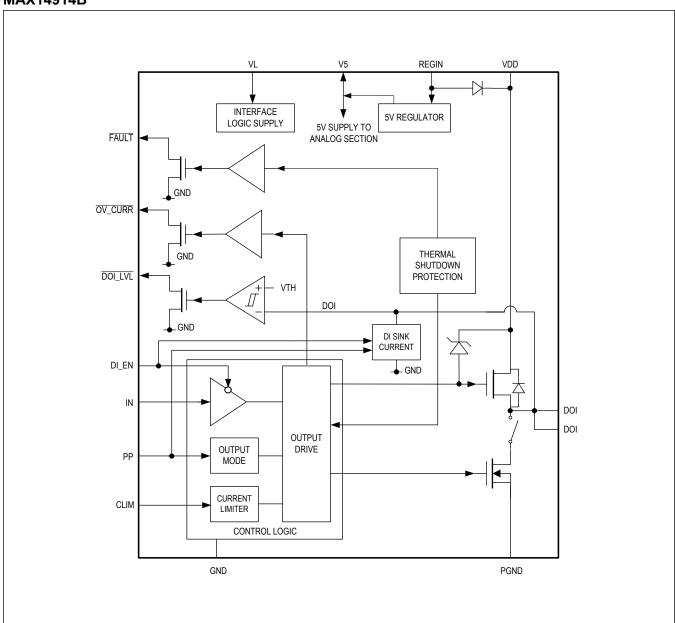

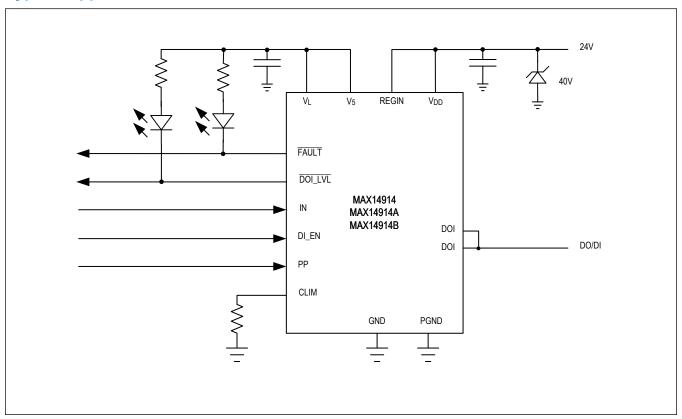

#### **MAX14914B**

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

#### **Detailed Description**

The MAX14914 family of parts is a high-side/push-pull driver that operates as an industrial digital output and can also operate as an industrial digital input. The MAX14914 family is specified for operation with supplies up to 40V. The high-side switch current limiting is resistor settable from 135mA (min) to 1.3A (min). The high-side driver on-resistance is  $120m\Omega$  (typ) and  $240m\Omega$  (max) at  $+125^{\circ}$ C ambient temperature. Optional push-pull operation allows driving of cables and fast discharge of load capacitance. A separate digital  $\overline{DOI\_LVL}$  allows supervision of the DOI voltage in DO mode for safety applications. The MAX14914 family complies with IEC Type 1, Type 2, or Type 3 input characteristics when configured for digital input operation.

The difference between the MAX14914, MAX14914A and MAX14914B versions is summarized in <u>Table 1</u>, and the summary of the control signals is shown in <u>Table 2</u>.

**Table 1. Features Selection**

|           | DOI OVERVOLTAGE<br>(OV_VDD) | DOI OVERCURRENT<br>(OV_CURR) | LOW DOI LEAKAGE<br>(V <sub>L</sub> < V <sub>L_POR</sub> ) |

|-----------|-----------------------------|------------------------------|-----------------------------------------------------------|

| MAX14914  | YES                         | NO                           | NO                                                        |

| MAX14914A | YES                         | NO                           | YES                                                       |

| MAX14914B | NO                          | YES                          | NO                                                        |

**Table 2. Operation Truth Table**

| MODE         | DI_EN | IN   | PP   | DOI         | DOI_LVL  |

|--------------|-------|------|------|-------------|----------|

| DO High-Side | low   | low  | low  | three-state | high/low |

| DO High-Side | low   | high | low  | high        | low      |

| DO Push-Pull | low   | low  | high | low         | high     |

| DO Push-Pull | low   | high | high | high        | low      |

| DI Type 1/3  | high  | х    | low  | high        | low      |

| DI Type 1/3  | high  | х    | low  | low         | high     |

| DI Type 2    | high  | х    | high | high        | low      |

| DI Type 2    | high  | х    | high | low         | high     |

When switching from the DI mode to DO, the following sequence must apply: keep IN input low, change the DI\_EN and PP signals for the selected mode of operation, wait 280µs (min) for the transition time, and then change the IN signal.

#### 5V Supply and Regulator

The MAX14914 family requires a 5V supply on the  $V_5$  pin for normal operation. This 5V supply can come from an external supply or from the internal 5V linear regulator. Connect the REGIN pin to  $V_{DD}$  to enable the internal regulator. Connect the REGIN pin to  $V_5$  pin to disable the internal regulator, when an external 5V is used. The internal 5V regulator can also power the external loads/circuits with of up to 20mA.

#### **Logic Interface**

The logic interface features flexible logic levels, allowing interfacing to a wide range of common logic. The  $V_L$  supply input defines the logic levels and can be set in the range of 2.5V to 5.5V. Connect a 0.1 $\mu$ F capacitor to  $V_L$ .

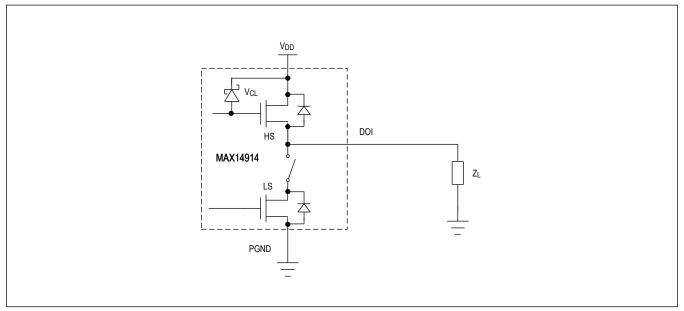

#### **Digital Output Operation**

The driver can be configured for high-side (PP pin is driven low) or push-pull (PP pin is driven high) operation. In DO high-side mode, the DOI output voltage is high ( $V_{DD}$ ) when the logic level on the IN pin is high, and three-state (Hi-Z), when the logic level on the IN pin is low. In DO Push-Pull mode, the DOI output voltage follows the logic level on the IN pin. The high-side driver has 240m $\Omega$  (max) on-resistance at 500mA and  $T_A$  = 125°C. The DOI voltage can drop below ground level, which occurs during the demagnetization of inductive loads. An internal clamping diode limits the negative excursion to ( $V_{DD}$  -  $V_{CL}$ ). See <u>Driving Inductive Loads</u> for details. The low-side (LS) switch speeds up the discharge of

High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

RC loads in push-pull mode.

Figure 4. Digital Output Driver

#### Low DOI Leakage Mode

The MAX14914A features a low-leakage mode in which the DOI leakage current is less than  $0.4\mu A$  with temperature up to +85°C and DOI between 0V and +15V. This is useful when the DOI pin is connected to an analog input/output (I/O) line and does not affect the performance of the analog I/O device. Low-leakage mode is enabled when the  $V_L$  voltage is held low below  $V_{LPOR}$  (min) = 1.12V. Note that the logic inputs, like IN, DI\_EN and PP, can be held high or low in low-leakage mode.

#### **Current Limit Adjustment**

The MAX14914 family has a settable current limiting of the HS switch. The load current is limited to a range between 135mA (min) and 1.3A (min), depending on the value of the resistor used at the CLIM pin. A short-circuit or overcurrent generally creates a temperature rise in the chip; both the HS and LS FET's temperatures are continuously monitored. When any switch temperatures exceed 170°C, the DOI output is put in Hi-Z until the temperature falls by 15°C. Connect a resistor (RLIM) from CLIM to GND to set the required current limit. The current is given by:

$$I_{IIM} = K \times V_{IIM} / R_{IIM}$$

where,  $V_{LIM}$  = 1.21V and K = 35.6 x 10<sup>3</sup>. If no resistor is connected to CLIM (i.e., CLIM is kept floating) or RLIM is more than 440k $\Omega$ , the ILIM is internally set to 1.1A (typ). If the RLIM resistor is less than 12.9k $\Omega$  (typ), the output is turned off. CLIM is short-circuit protected.

Use the formulas below to validate the accuracy range:

$I_{LIM\_MAX} = I_{LIM} \times (1 + |I_{CLIM\_HS\_GE}|/100) + |I_{CLIM\_HS\_OE}|$   $I_{LIM\_MIN} = I_{LIM} \times (1 - |I_{CLIM\_HS\_GE}|/100) - |I_{CLIM\_HS\_OE}|$

#### **Low-Side Current Limit**

The low-side transistor has fixed-current limiting, when enabled in push-pull mode (PP driven high). The low-side driver limits current at 200mA (typ). The load current is actively controlled and the low-side switch only turns off if the driver temperature has fallen by the hysteresis value.

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

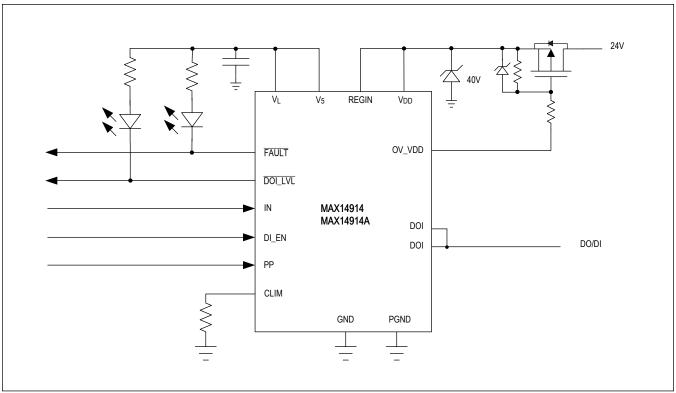

#### **Overcurrent Signaling**

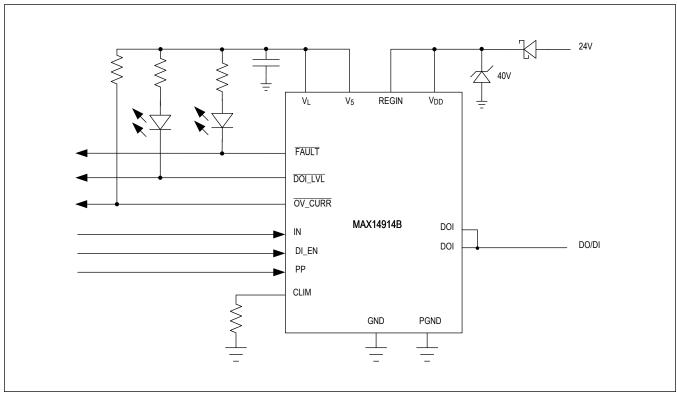

The MAX14914B features an overcurrent output ( $\overline{OV\_CURR}$ ), which provides a diagnostic signal as soon as the load current exceeds the high-side driver's set current limit in both high-side and push-pull DO modes ( $DI\_EN$  = low and PP = x). When the high-side FET detects an overcurrent for a duration longer than 8µs, the  $\overline{OV\_CURR}$  open-drain signal becomes active low and remains low until the overcurrent condition disappears. The overcurrent condition also disappears every time the high-side switch turns off when a short-circuit condition exists and the FET turns off for thermal shutdown protection. Note that  $\overline{OV\_CURR}$  does not signal an overcurrent on the low-side driver in push-pull mode. The typical application circuit with the overcurrent signaling is shown in Figure 5.

Figure 5. MAX14914B Application Diagram

#### **Short-Circuit Protection**

Short circuits at the DOI output generate high transient currents until the active current limiting kicks in. In order to protect the MAX14914\_ against high currents that can be seen over an extended time, especially if the output is switching at a high rate into a short circuit, the MAX14914\_ enters a protective mode. When the MAX14914\_ detects that the DOI current is over 3x higher than the set current limit, the driver is switched to protective mode with reduced turn-on slew rate of the rising and falling edges for a duration of 4ms. The FAULT signal does not become active and the chip operates normally, but with reduced slew rate. If the cause for the short circuit is not removed, the protective mode will remain for an additional 4ms until the short circuit is removed.

#### **Overvoltage Lockout**

When the  $V_{DD}$  supply voltage exceeds the OVLO threshold voltage of 42.2V (typ), for a time duration longer than 200 $\mu$ s, the high-side and low-side switches automatically turn off. They remain off until  $V_{DD}$  is reduced to below the threshold OVLO voltage minus hysteresis. When  $V_{DD}$  is above the OVLO threshold, the OV\_VDD output is active.

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

#### **Undervoltage Lockout**

When the  $V_{DD}$ ,  $V_5$ , or  $V_L$  supply voltages are under their respective UVLO thresholds the DOI driver is turned off (three-stated). DOI automatically turns back on, once  $V_{DD}$ ,  $V_5$ , and  $V_L$  rise above their UVLO threshold.

Note that when  $V_L \le 1.12V$ , the MAX14914ATE+ and MAX14914BATE+ force the OV\_VDD pin low while the MAX14914AATE+ keeps this pin in a Hi-Z state.

#### **Driving Capacitive Loads**

When charging/discharging purely capacitive loads with a push-pull driver, the driver dissipates power that is proportional to the switching frequency. The power can be estimated by PD  $\sim$  C x  $V_{DD}^2$  x f, where C is the load capacitance,  $V_{DD}$  is the supply voltage, and f is the switching frequency. For example, in an application with a 10nF load and 10kHz switching frequency, the driver dissipates 130mW at  $V_{DD}$  = 36V. Therefore, switching to a higher capacitance can induce thermal shutdown, which limits the operational frequency.

#### **Driving Inductive Loads**

The DOI pins can be pulled below ground potential when the high-side transistor is off. The MAX14914\_ has an internal clamping diode from  $V_{DD}$  to DOI that limits the negative voltage excursion to ( $V_{DD}$  - 55V) typ. Turning off the current flowing through ground-connected inductive loads results in a negative voltage at the DOI pin, which is limited to  $V_{CL}$  below  $V_{DD}$  by the internal clamping diodes.

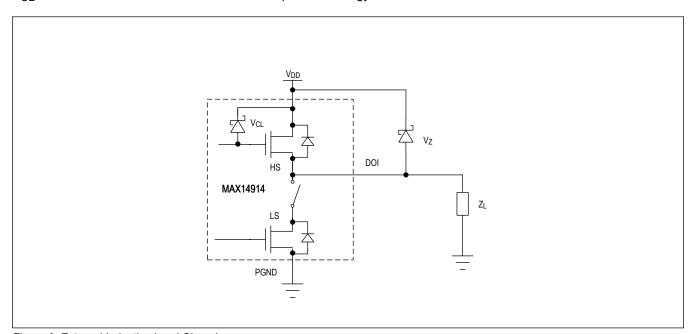

The MAX14914\_ features SafeDemag, meaning that there are no limits for load inductance that it can demagnetize, for load currents of up to 600mA. Turn-off of large inductive loads with currents larger than 600mA requires an external clamping diode, as shown in Figure 6. The clamping (breakdown) voltage of such diode needs to be less than  $V_{CL}$ :  $V_Z < V_{CI}$ . Ensure that the Zener diode is able to dissipate the energy.

Figure 6. External Inductive Load Clamping

#### Monitoring of the DOI Output

The driver output (DOI) is <u>monitored</u> in both high-side and push-pull modes, <u>and the corresponding logic level</u> can be seen through the inverted <u>DOI\_LVL</u> logic output. The threshold voltage for the <u>DOI\_LVL</u> comparator is between 1.5V and 2.0V. This feature is useful for functional safety applications.

Note that when the switch is under thermal shutdown, the DOI\_LVL logic is kept low regardless of the state of the DOI pin.

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

In case of a loss of ground in DO mode, the DOI\_LVL is set to high. In both cases, the thermal shutdown and loss of ground, the FAULT signal is low, indicating fault conditions.

#### **Digital Input Operation**

The MAX14914\_ can operate as an industrial digital input. Drive the  $\underline{\text{DI\_EN}}$  pin high to enable digital input operation. The 2.3mA/7mA internal current sink on DIO is then enabled, and the  $\overline{\text{DOI\_LVL}}$  logic output presents the inverse of the DOI logic, with threshold voltages compliant with IEC61131-2 Type 1, Type 2, or Type 3 levels. IN DI mode, the PP input allows selection between IEC Type 1/3 and Type 2 input characteristics. Set the PP low for Type 1/3 compatibility and set the PP high for Type 2 compatibility. To allow the DOI input voltage to go above the VDD supply voltage and prevent race condition, an external Schottky diode can be placed in series with the VDD supply, as shown in Figure 7. Alternatively, an external pMOS transistor can be connected in series with the 24V supply, as shown in Figure 8, to allow the DOI voltage to exceed VDD. The gate of the pMOS can be driven by the open-drain OV\_VDD output (MAX14914 and MAX14914A only). When DI\_EN = high, the OV\_VDD pin turns the pMOS off permanently. Therefore, VDD is one forward diode voltage (of the pMOS) below the external 24V field supply, when the DOI voltage is less than the field supply voltage. The MAX14914\_ is parasitically powered by the external DOI input, when the DOI voltage is higher than the VDD supply. Note that the power dissipation increases strongly when Type 2 DI mode is selected (PP = high), particularly with high DOI input voltages due to the 7mA (typ) current sink. When the VDOI voltage exceeds 42.5V (typ), the sink current is automatically decreased from 7mA (typ) to 2.3mA (typ) to reduce the power dissipation.

Figure 7. DO/DI Configuration with External Schottky Diode

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

Figure 8. DO/DI Configuration with External pMOSFET

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

#### **Applications Information**

#### **Layout Considerations**

The PCB designer should follow some critical recommendations in order to get the best performance from the design.

- Keep the input/output traces as short as possible. Avoid using vias to make low-inductance paths for the signals.

- Have a solid ground plane underneath the high-speed signal layer.

A suppressor/TVS diode should be used between  $V_{DD}$  and PGND to clamp positive-surge transients on the  $V_{DD}$  supply input and surges from DOI. The standoff voltage should be higher than the maximum operating voltage of the device, while the breakdown voltage should be below 65V. As long field-supply cables can generate large voltage transients on the  $V_{DD}$  supply due to large dI/dt, it is recommended to add a large  $10\mu F$  capacitor to the  $V_{DD}$  line at the point of field supply entry.

#### **Surge Protection**

DOI is protected against  $\pm 2kV/42\Omega$  surge pulses as per IEC61000-4-5. Thus, no external surge suppression is needed on DOI. A suppressor/TVS diode (SMBJ40A, for example) should be used between  $V_{DD}$  and PGND to clamp high-surge transients on the  $V_{DD}$  supply input and surges from DOI. The breakdown voltage of TVS should be higher than the maximum operating voltage of the equipment, while the maximum clamping voltage should be below 65V.

#### **Conducted RF Immunity**

To insure that the DOI driver, configured for HS mode with the switch turned off, is not turned on during IEC61000-4-6 RF immunity testing, a 10nF capacitor should be applied between the DOI output and PGND. For PP mode a capacitor on DOI is not needed.

#### **Reverse Current into DOI**

Reverse current flow into DOI pin in DO mode will heat up the device and can destroy it thermally. The allowed reverse current depends on  $V_{DD}$ , the ambient temperature and the thermal resistance. At an ambient temperature of 25°C, the continuous reverse current into DOI pin should be limited to 250mA at  $V_{DD}$  = 40V and 400mA at  $V_{DD}$  = 24V. Using a pMOS transistor or a Schottky diode (as shown in <u>Figure 7</u> and <u>Figure 8</u>) removes the reverse current flow path into the 24V field supply.

# **Typical Application Circuits**

# **Ordering Information**

| PART           | PACKAGE | BODY SIZE | PIN PITCH | TEMP RANGE (°C) |

|----------------|---------|-----------|-----------|-----------------|

| MAX14914ATE+   | TQFN16  | 4mm x 4mm | 0.65mm    | -40 to +125     |

| MAX14914ATE+T  | TQFN16  | 4mm x 4mm | 0.65mm    | -40 to +125     |

| MAX14914AATE+  | TQFN16  | 4mm x 4mm | 0.65mm    | -40 to +125     |

| MAX14914AATE+T | TQFN16  | 4mm x 4mm | 0.65mm    | -40 to +125     |

| MAX14914BATE+  | TQFN16  | 4mm x 4mm | 0.65mm    | -40 to +125     |

| MAX14914BATE+T | TQFN16  | 4mm x 4mm | 0.65mm    | -40 to +125     |

<sup>+</sup>Denotes a lead (Pb)-free/RoHS-compliant package

T = Tape and Reel

# High-Side Switch with Settable Current-Limiting, Push-Pull Driver Option and Digital Input Configuration

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |

|--------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 0                  | 12/16         | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                   |

| 1                  | 07/17         | Corrected pin number in <i>Pin Description</i> section and updated various typos                                                                                                                                                                                                                                                                                                                                                                                                          | 1, 10, 13           |

| 2                  | 12/17         | Updated the Electrical Characteristics global specifications                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-5                 |

| 3                  | 6/18          | Updated the Electrical Characteristics, Typical Operating Characteristics, Pin Description, and Function Diagram sections, and Figures 4 and 5                                                                                                                                                                                                                                                                                                                                            | 5, 9, 10,<br>12–14  |

| 4                  | 9/20          | Added MAX14914A and MAX14914B; updated the General Description, Benefits and Features, Block Diagram, Electrical Characteristics, Pin Configuration, Pin Description, Functional Diagrams, Overvoltage Lockout, Undervoltage Lockout, Driving Inductive Loads, and Ordering Information sections; updated Figures 1–2 and before renumbering, Figures 6–7; added TOC18, the Low DOI Leakage Mode and Overcurrent Signaling sections, and a new Figure 5 and renumbered subsequent figures | 1–25                |

| 5                  | 11/24         | Modified content under Electrical Characteristics, Removed images under TOC, Modified content under Pin Description, Added text under Operation Truth Table, Added note under Monitoring of the DOI Output                                                                                                                                                                                                                                                                                | 6, 10,13,<br>17, 20 |