逐次比較型(SAR)ADCは、高分解能、高精度、低消費電力のコンバータです。システム設計者は高精度のSAR ADCを選択してから、最良の結果が得られるようにサポート回路を決定する必要があります。この場合、アナログ入力信号をADCに接続するフロントエンド、電圧リファレンス、デジタル・インターフェースという3つの主要領域を考慮しなければなりません。本稿では、フロントエンドを設計する際の回路条件とトレードオフについて説明します。システム/デバイス固有のほかの領域については、データシートや本書の参考文献を参照してください。

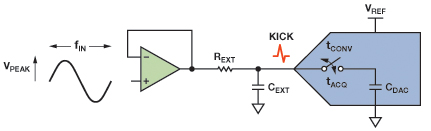

フロントエンドは、駆動アンプとRCフィルタという2つのデバイスで構成されます。アンプは入力信号を調整するとともに、信号源とADC入力間の低インピーダンス・バッファとしても機能します。RCフィルタはADC入力に入る帯域外ノイズの量を制限し、ADC入力におけるスイッチド・キャパシタからのキックバックを減衰することができます。

SAR ADCに最適なアンプとRCフィルタを選択することは、そう簡単ではありません。ADCのデータシートを通常どおり使用できないアプリケーションの場合は特にそうです。ここでは、アンプやRCの選択に影響を及ぼすさまざまなアプリケーション側の要因を考慮し、最良のソリューションを実現するための設計の指針をご紹介します。主に考慮しなければならないものは、入力周波数、スループット、入力マルチプレクシングです。

適切なRCフィルタの選択

適切なRCフィルタを選択するには、シングル・チャンネルまたは多重化アプリケーションのRC帯域幅を計算してからRとCの値を選ぶ必要があります。

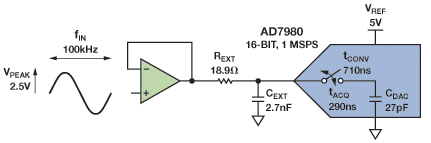

図1は、代表的なアンプ、単極RCフィルタ、ADCを示しています。ADC入力は、駆動回路にスイッチド・キャパシタ負荷を提供します。入力帯域幅は10MHzですが、このため、高いS/N比(SNR)を実現するには広い帯域幅で低ノイズが必要です。RCネットワークは入力信号の帯域幅を制限し、アンプと後置の回路によってADCへのノイズを低減します。ただし、帯域幅を制限しすぎると、セトリング時間が長くなり、入力信号に歪みが生じます。

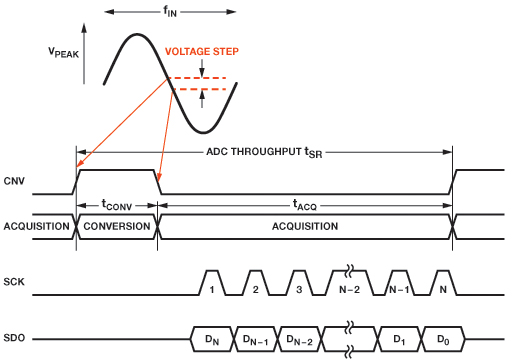

ノイズの最適な帯域制限を行いつつADC入力をセトリングするための最小RC値は、ステップ入力のセトリングが指数関数的であると想定して計算します。ステップのサイズを計算するには、入力信号の周波数、振幅、およびADCの変換時間を知る必要があります。変換時間tCONV(図2)は、容量性DACが入力から切断されて、ビット・トライアルを実行してデジタル・コードを生成している時間です。変換の終了時に、前のサンプル電荷を保持している容量性DACは入力にスイッチバックされます。このステップ変化は、入力信号がその時間にどれだけ変化したかを示します。このステップのセトリングに要する時間をリバース・セトリング時間と言います。

特定の入力周波数が歪む事のないサイン波信号の最大変化率は、次式で計算できます。

ADCの変換レートが最大入力周波数よりかなり高い場合、入力電圧が変換時間中に変化した最大値は次式で得られます。

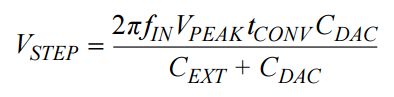

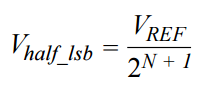

これは、容量性DACがアクイジション・モードに戻るときに発生する最大電圧ステップです。このステップは、ADCの容量と外部コンデンサの容量の並列組み合わせによって減衰されます。このため、外部コンデンサは比較的大きなもの(数ナノファラッド)となります。この分析では、入力スイッチのオン抵抗がほとんど影響を及ぼさないものと仮定します。セトリングが必要なステップ・サイズは次式で得られます。

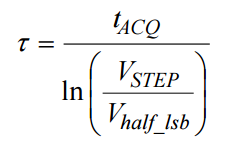

次に、ADCのアクイジション時間内にADC入力を1/2LSBにセトリングするための時定数を計算します。ステップ入力の指数関数セトリングを想定した場合、必要なRC時定数τは次式で表すことができます。

ここで、tACQはアクイジション時間、NTCはセトリングに必要な時定数の数です。必要な時定数の数は、ステップ・サイズVSTEPと次式のセトリング誤差(この場合は1/2LSB)との比の自然対数から計算できます。

これにより、

これを前の式に代入すると、

また、等価のRC帯域幅は

になります。

例:RC帯域幅の計算式を用意したら、16ビットADCのAD7980を選択します。図3に示すようにこのADCの変換時間は710ns、スループットは1MSPS、リファレンス電圧は5Vです。対象となる最大入力周波数は100kHz です。この周波数の最大ステップ・サイズを計算すると、次のようになります。

このステップは、外部コンデンサからの電荷によって減衰されます。使用するDAC容量が27pFで、外部容量が2.7nFとなる場合、減衰係数は約101となります。これらの値をVSTEP の式に使用すると、以下のようになります。

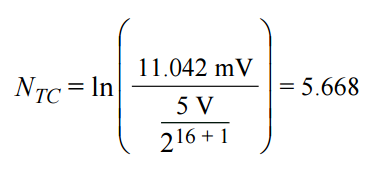

次に、リファレンスが5Vの場合に1/2LSB(16ビット・コード)にセトリングするための時定数の数を計算します。

アクイジション時間は次のようになります。

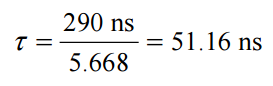

τ について計算すると、

したがって、帯域幅=3.11MHz、REXT=18.9Ωです。

最小帯域幅、スループット、入力周波数の3つの関係から、入力周波数が増大するほど広いRC帯域幅が必要になることがわかります。同様に、スループットが高くなると、アクイジション時間が短くなり、RC帯域幅は広くなります。アクイジション時間は、必要な帯域幅に対して最も大きな影響を与えます。アクイジション時間が2倍になると(スループットは低下)、必要な帯域幅は半分になります。この簡略化された分析には、低周波のときに支配的となる二次電荷のキックバック効果は含まれていません。DCを含む超低入力周波数(<10kHz)の場合は、コンデンサDACでセトリングする約100mVの電圧ステップが必ず存在します。上記分析では、この数値を最小可能電圧ステップとして使用します。

マルチプレクサ入力信号はめったに連続することはなく、一般的にはチャンネル間の切替え時の大きなステップで構成されます。最悪の場合、ひとつのチャンネルが負のフルスケール、次のチャンネルが正のフルスケールとなります(図4)。この場合、マルチプレクサでチャンネルを切り替えるときにステップ・サイズはADCのフルレンジ(上の例では5V)になります。

上の例のマルチプレクサ入力を使用すると、リニア応答に必要なフィルタ帯域幅は3.93MHz にまで増大します(ステップ・サイズは、シングル・チャンネルで1.115Vであるのに対し5V)。これは、マルチプレクサが変換開始後すぐにスイッチング動作を行うことを仮定しています(図5)。また、アンプとRCのフォワード・セトリング時間が十分にあって、アクイジション開始前に入力コンデンサがセトリングするものと仮定しています。

計算したRC帯域幅については、表1で確認することができます。この表からわかるように、フルスケール・ステップが16ビット・レベルにセトリングするには11倍の時定数が必要になります。計算したRCについては、フィルタのフォワード・セトリング時間は11×40.49ns=445nsとなります。これは710nsの変換時間よりずっと小さい値です。フォワード・セトリングは必ずしも変換時間中(コンデンサDACが入力に切り替えられる前)に発生する必要はありませんが、フォワード・セトリング時間とリバース・セトリング時間を合計した値は所要のスループット・レートを超えてはなりません。低周波の入力の場合、信号が変化する速度はかなり遅いため、フォワード・セトリングはそれほど重要ではありません。

表1. Nビット分解能の各レベルにセトリングするための時定数の数| 分解能(ビット) |

LSB (%FS) |

1LSB誤差に対する時定数の数 |

| 6 | 1.563 | 4.16 |

| 8 | 0.391 | 5.55 |

| 10 | 0.0977 | 6.93 |

| 12 | 0.0244 | 8.32 |

| 14 | 0.0061 | 9.70 |

| 16 | 0.0015 | 11.09 |

| 18 | 0.00038 | 12.48 |

| 20 | 0.000095 | 13.86 |

| 22 | 0.000024 | 15.25 |

近似フィルタの帯域幅を計算したら、REXTとCEXTの値を選択することができます。上述の計算では、CEXT=2.7nFとしています。これはデータシートに記載されているアプリケーション回路の代表的な値です。大きなコンデンサを選択すれば、コンデンサDAC切替え時のキックバックの減衰量が増大するでしょう。しかし、コンデンサの値が大きいと、駆動アンプが不安定になる可能性も増大します。特に、任意の帯域幅に対してREXTの値が小さくなるとそうなります。REXTの値が小さくなりすぎると、アンプの位相余裕が低下してアンプの出力にリンギングが発生するか、または出力が不安定になる可能性があります。直列抵抗REXTを小さくして負荷を駆動する場合は、低出力インピーダンスのアンプを使用する必要があります。位相余裕が十分であることを確認するために、RC組み合わせ回路とアンプのボード線図を使って安定性を分析することができます。最良の選択は、アンプを安定に保つための適正な抵抗値と1 ~ 3nFの容量値を選ぶことです。また、歪みを低く抑えるには電圧係数が低いコンデンサ(NP0タイプなど)を使用することも重要です。

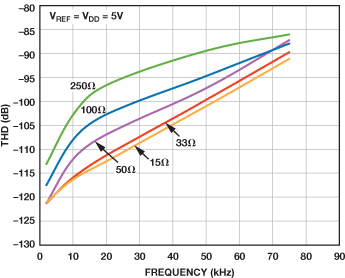

REXTの値によって条件を満たす歪みレベルを維持することは重要です。図6は、AD7690において駆動回路の抵抗が周波数の関数として歪みにどのように影響するかを示しています。歪みは入力周波数とソース抵抗が大きくなるほど増大します。この歪みは、主にコンデンサDACのインピーダンスの非線形性に起因します。

低入力周波数(<10kHz)の場合は、大きい直列抵抗値を使用できます。歪みは入力信号の振幅にも左右されます。抵抗値が大きくても振幅を小さくすれば、歪みを同じレベルに維持できます。上記の例でτ = 51.16ns、CEXTの値を2.7nFと仮定してREXTを計算すると、抵抗値18.9Ωが得られます。これらは、アナログ・デバイセズのデータシートのアプリケーションのセクションに記載されている一般的な値に近い値です。

ここで計算した公称のRC値は最終的な値というより、役に立つ目安です。REXTとCEXTの間で適正なバランスがとれる値を選択するには、入力周波数範囲、アンプで駆動できる容量の大きさ、受容可能な歪みレベルなどの知識が必要になります。RC値を最適化するには、実際のハードウェアで実験して最高の性能を実現できるようにすることが重要です。

適切なアンプの選択

前節では、入力信号とADCスループットに基づいてADC入力に適したRC帯域幅を計算しました。ADCを駆動するための最適なアンプを選択するには、この情報を使用する必要があります。ここでは、以下の事項について検討します。

- アンプの大信号/小信号帯域幅

- セトリング時間

- アンプのノイズ仕様とシステム・ノイズの影響

- 歪み

- 歪みと電源レールのヘッドルーム条件

アンプの小信号帯域幅は一般にデータシートに規定されています。しかし、入力信号のタイプによっては大信号帯域幅のほうが重要になることがあります。これは特に、高い入力周波数(>100kHz)または多重化アプリケーション(電圧振幅が大きいため)の場合に当てはまり、入力信号のフォワード・セトリングのほうが重要になります。たとえば、ADA4841-1の小信号帯域幅は80MHz(20mVp-p信号)で、大信号帯域幅は3MHzです(2Vp-p信号)。上の例でAD7980を使用すると、RC帯域幅の計算値は3.11MHzになりました。ADA4841-1の80MHzの小信号帯域幅はリバース・セトリングにはかなり余裕があるので、このアンプは低入力周波数の場合に優れた選択肢となりますが、多重化アプリケーションでは相当苦戦するはずです(大信号振幅ではRC帯域幅条件は3.93MHzまで増大します)。この場合は、大信号帯域幅が30MHzのADA4897-1アンプのほうが適しています。一般に、アンプの小/大信号帯域幅は、リバース/フォワード・セトリングのいずれが優勢かによってRC帯域幅の2 ~3倍以上としてください。これは、電圧ゲインを提供するアンプ段が必要なために、使用できる帯域幅が減少する場合には特に重要です。この場合は、もっと広い帯域幅のアンプが必要になるかもしれません。

フォワード・セトリング条件を考える場合は、アンプのセトリング時間の仕様も役に立ちます。一般には、規定ステップ・サイズの一定のパーセンテージにセトリングするための時間を使用します。16 ~ 18ビット性能の場合は一般に0.001%までのセトリングが必要となりますが、ほとんどのアンプはステップ・サイズにより0.1%または0.01%で仕様規定されています。したがって、ADCのスループットでセトリング動作が受入れ可能かどうかについては、これらの数値である程度妥協する必要があります。ADA4841-1の仕様では、0.01%までのセトリング時間は8Vステップで1μsです。1MSPS(1μs 間)でAD7980を駆動する多重化アプリケーションではフルスケール・ステップで入力を時間内にセトリングすることはできませんが、おそらく低いスループット、たとえば500kSPSであれば可能です。

RC帯域幅は、アンプの最大許容ノイズを決めるときに重要な意味を持ちます。アンプのノイズは、一般にノイズ曲線平坦部の高周波の広帯域幅ノイズ・スペクトル密度と低周波の1/fノイズ(0.1 ~ 10Hz)によって規定されています(図7)。

ADCの総入力換算ノイズは次のように計算できます。まず、RC帯域幅におけるアンプの広帯域幅スペクトル密度に起因するノイズを計算します。

ここで、en =ノイズ・スペクトル密度(nV/√Hz)、N=アンプ回路のノイズ・ゲイン、BWRC=RC帯域幅(Hz)です。

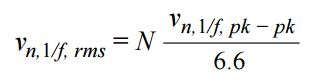

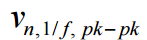

次に、低周波の1/f ノイズを算入します。このノイズは一般にピークtoピークで規定されるため、通常は以下の式を使ってrmsに換算する必要があります。

ここで

=1/fピークtoピーク・ノイズ電圧、N=アンプ回路のノイズ・ゲインです。

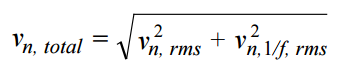

総ノイズは2乗和平方根で与えられます。

SNR全体への影響を最小限に抑えるために、総ノイズはADCのノイズの約1/10とします。ノイズはターゲット・システムのSNRに応じて大きくなってもかまいません。たとえば、ADCのSNRが91dBでVREFが5Vの場合、総ノイズは下記の値以下にしてください。

この数値から、1/ f ノイズおよび広帯域ノイズ・スペクトル密度の最大許容仕様値を簡単に計算できます。対象となるアンプの1/f ノイズが無視できる程度の大きさで、そのアンプがユニティ・ゲインで動作し、前に計算したRC帯域幅(3.11MHz)を持つフィルタを使用する場合は、次の値が得られます。

したがって、アンプは広帯域ノイズ・スペクトル密度を2.26nV/√Hz以下にする必要があります。ADA4841-1は、2.1nV/√Hzの仕様でこの条件を満たしています。

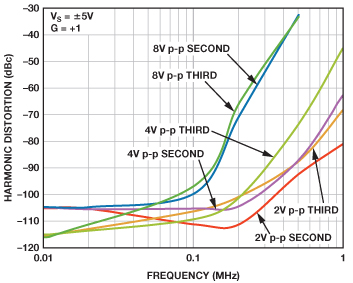

アンプについて考慮すべきもう一つの重要な仕様は、特定の入力周波数での歪みです。一般に、最高の性能を得るために、当該入力周波数での全高調波歪み(THD)は16ビットで約100dB、18ビットADCの場合は約110dBが必要です。図8は2Vp-p入力信号を使用したADA4841-1の代表的な歪み周波数特性を示しています。

図では全高調波歪みではなく、通常最も優勢な二次高調波成分と三次高調波成分を示しています。ADA4841-1は十分にクリーンであり、最大約30kHz の18ビットADCを駆動して優れた歪み特性を示します。入力周波数が100kHz 付近からそれを超えるまでになると、歪み性能が劣化し始めます。高周波数で歪みを抑えるには、高出力、広帯域のアンプが必要となります。信号が大きくなる場合も、それに応じて性能は低下します。ADC入力が0 ~ 5Vの場合、歪み性能の信号範囲は5Vp-pに増大します。これによって図8に示す歪み図とは異なる性能が生じるため、アンプが条件を満たしているか確認するためのテストを行う必要があります。図9は、複数の出力電圧レベルで歪み性能を比較しています。

THDはヘッドルームによっても影響を受けます。すなわち、アンプの実際の最大入力/出力振幅と正/負電源レールとの差による影響です。アンプはレールtoレール入力/出力を持つものがあり、最大1V以上のヘッドルームが必要になることがあります。レールtoレール入力/出力でも、アンプのレールに近い信号レベルで実行していれば優れた歪み性能を達成するのは容易ではありません。したがって、最大入出力信号がレールに近づかないような電源レベルを選択するとよいでしょう。ここで、たとえばADA4841-1アンプで入力レンジ0 ~ 5VのADCを駆動し、ADCのレンジを最大化しなければならない場合について考えてみましょう。アンプはレールtoレール出力を持ち、入力には1Vのヘッドルームが必要です。ユニティ・ゲイン・バッファとして使用する場合は、1V以上の入力ヘッドルームが必要となるため、正電源は6V以上にする必要があります。出力はレールtoレールですが、正電源またはグラウンドの約25mV以内にしか駆動されないので、グラウンドまで全範囲で駆動するには負の電源が必要となります。負の電源は、歪み性能に余裕を持たせるために、たとえば-1Vにすることができます。

ADC入力レンジが狭まることを受け入れて、SNRがいくらか低下してもよいという場合であれば、負電源なしで済ませることができます。たとえば、ADCの入力レンジが0.5 ~ 5Vにまで狭まれば、ADCレンジが10%失われてSNRは約1dB低下します。しかし、この場合は負のレールをグラウンドに接続することができるため、負電源の生成に必要な回路がなくなり、消費電力やコストを低減することができます。

このように、アンプを選択するときは、入出力信号レンジの条件を考慮することが重要です。この条件によって必要な電源電圧が決まります。この例では、5V動作の仕様のアンプでは十分ではありません。ADA4841-1は最大12Vで仕様規定されているため、高い電源電圧を使用すればうまく機能します。こうすれば、適正な電源マージンが確保できます。

その他の注目製品に関する情報

レールtoレール出力の低消費電力、低ノイズ、低歪みのオペアンプ

ADA4841-1は、2nV/√Hzの広帯域ノイズと-110dBcのスプリアスフリー・ダイナミック・レンジ(SFDR)を実現する低消費電力オペアンプです。16ビット/ 18ビットPulSAR®ADCの駆動に最適です。また、携帯型計測器、工業用プロセス制御、医療機器にも最適な製品です。ユニティ・ゲインが安定しているほか、60μVの入力オフセット電圧、114dBのオープンループ・ゲイン、114dBの同相ノイズ除去、80MHzの帯域幅(-3dB)、12V/μsのスルーレート、175nsのセトリング時間(0.1%)といった特性を備えています。入力信号は負レールから100mV下側まで拡張でき、出力の振幅はいずれか一方のレールの100mV以内まで対応するため、真の単電源機能を提供します。ADA4841-1は2.7 ~ 12Vの単電源または±1.5 ~±6Vの両電源で動作し、その消費電流はノーマル・モードで1.1mA、パワーダウン・モードで40μAです。8ピンSOICパッケージ採用のこの製品は-40 ~+125℃の温度範囲で仕様規定されており、1,000個受注時の米国での単価は$1.59です。

レールtoレール出力の低ノイズ、低消費電力のオペアンプ

ADA4897-1はレールtoレール出力、1nV/√Hzの電圧ノイズ、2.8pA/√Hzの電流ノイズ、230MHzの帯域幅、120V/μsのスルーレート、45nsのセトリング時間、ユニティ・ゲイン安定を提供する低ノイズの高速オペアンプです。超音波、低ノイズ・プリアンプ、高性能ADCの駆動、高性能DACのバッファリングなど、さまざまなアプリケーションに最適です。3 ~ 10V単電源で動作し、消費電力は3mAです。8ピンMSOP、LFCSP、SOICパッケージを採用し、-40 ~+125℃の温度範囲で仕様規定されています。1,000個受注時の米国での単価は$1.89です。

7mWで動作する16ビット、1MSPS、逐次比較型ADC

AD7980は低消費電力の逐次比較型ADCであり、1MSPSサンプリング・レートでノー・ミスコードの16ビット分解能を実現します。0 ~VREFレンジの疑似差動入力に対応し、91.5dBの信号/ノイズ&歪み比(SINAD)、-110dBの全高調波歪み(THD)、±1.25LSBの最大積分非直線性を提供します。この逐次比較型アーキテクチャにより、パイプライン遅延がなくなります。また、デイジーチェーン接続により、複数のADCでシングル・バスを共有させることができます。変換と変換の間に自動的にパワーダウンするため、消費電力はスループット・レートに応じて調整できます。2.5V単電源で動作するAD7980は1MSPSで7mW、10kSPSで70μWの電力を消費し、スタンバイ・モードで350pAの電流を消費します。10ピンMSOPパッケージを採用し、-40 ~+85℃の温度範囲で仕様規定されています。1,000個受注時の米国での単価は$11.95からです。

EngineerZoneのAnalog Dialogue Communityに掲載している”adc front ends”についてのブログ(英語)についてのコメントもお待ちしております。

参考資料

AN-931 アプリケーション・ノート:PulSAR ADC サポート回路の解説

AN-1024 アプリケーション・ノート:マルチプレクサのセトリング・タイムとサンプリング・レートの計算方法

MT-048 Tutorial. Op Amp Noise Relationships; 1/f Noise, RMS Noise, and Equivalent Noise Bandwidth.

Ardizzoni, John, ドライビングMiss ADC RAQ-84, July 2012.

Ardizzoni, John. 大いなる遺産は基本的な理解から RAQ-85, August 2012.

Ardizzoni, John, and Jonathan Pearson. 高速差動ADCドライバの「交通規則」 Analog Dialogue, Volume 43, Number 2, 2009.